脉动阵列专题

谷歌TPU_脉动阵列实现矩阵乘法(附完整Verilog代码)

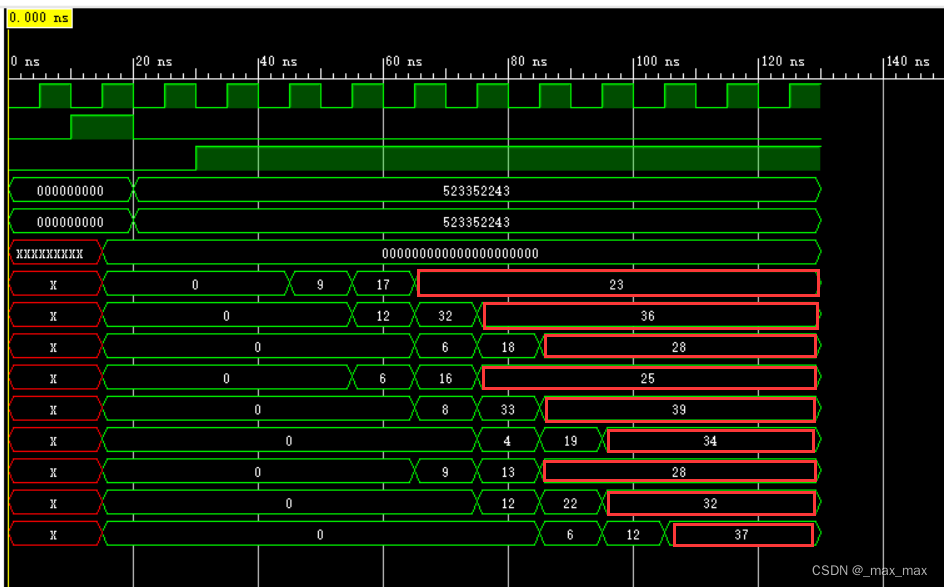

谷歌TPU_脉动阵列实现矩阵乘法(附完整Verilog代码) 一、谷歌TPU介绍TPU计算核心的硬件架构 二、矩阵乘法单元硬件架构三、脉动阵列实现矩阵乘法原理四、Verilog实现PE单元顶层文件Testbench文件仿真结果 一、谷歌TPU介绍 谷歌的 TPU(张量处理单元)是一种专门为机器学习工作负载优化的定制硬件加速器。TPU 通过高效地执行矩阵乘法、卷积运算和其他常

通用脉动阵列systolic array及矩阵乘法Matrix Multiplication

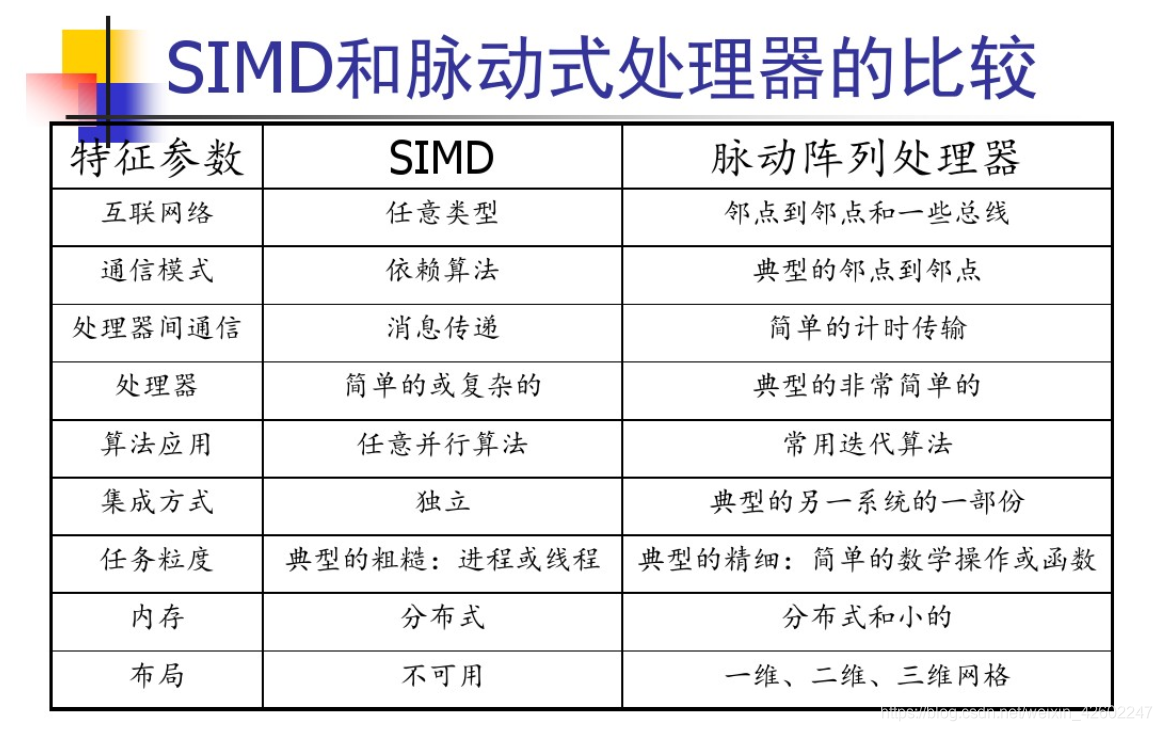

目录 脉动阵列的特点Matrix Multiplication矩阵乘法通用SA(systolic array)发展趋势SIMD和SA处理器的比较Reference 脉动阵列的特点 优点: 结构简单,规整,控制方便 计算并行度高,吞吐量高 缺点: 具有一定的专用性 Matrix Multiplication矩阵乘法 下图原文有个小错误,A[J,K]应该是A[I,K] 为