管脚专题

士兰微 SC32F5432 通过配置寄存器方式 将管脚配成开漏输出模式和TTL输入模式

目录 前言: 士兰微电子介绍 士兰微 SC32F5432介绍 士兰微 SC32F5432 通过配置寄存器方式 将管脚配成开漏输出模式和TTL输入模式 开漏输出模式 TTL输入模式 前言: 下面是对我在工作时公司所使用的一款国产芯片(士兰微 SC32F5432)开发过程所遇到的一些问题的记录与解决。 士兰微电子介绍 杭州士兰微电子股份有限公司(600460)坐落于杭州

管脚复用中对管脚功能确定的一点经验

在嵌入式画板的时候, 我们需要先明确功能需求, 然后选择芯片, 然后再确定管脚, 特别是在嵌入式资源比较紧缺的时候, 合理分配管脚显得尤为重要. 但是当功能变得非常多的时候, 合理两个字也变得有一定的难度. 我这里谈谈我的一次分配的过程, 供大家参考. 第一步. 确定好功能和芯片 如我们要用 gd32f103 的 usart, i2c, spi 各一组, 由于芯片有很多管脚的封装, 这里功

串口接收异常,接收管脚无法被拉低

场景:调试氧气浓度芯片AOF1010,此芯片通过串口通信,通电后自动通过串口上传数据 问题:环境搭好,通电,没有进串口接收中断 推测: 1)数据没有发送过来? 通过逻辑分析仪检测,发现Rx管脚没有收到数据,此时判断是芯片问题,没有自动发数据回来(后来发现这种判断是错的,因为逻辑分析仪是需要边沿触发的,通过示波器,检测到有数据发来,只是低电平是3v,高电平是3.3v,所以没有

全志A40平台管脚复用配置

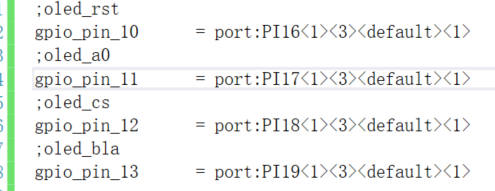

一 资源分配 1 实际项目需要使用I2C接口的OLED,由于OLED有RST复位线,A0命令和地址线,CS片选线,背光控制线BLK。控制线选定T19_UART2_RTS - RST T23_UART2_CTS-A0 T24_UART2_TX-CS T22_UART2_RX-BLK,实际电路图如下: 二 根据实际修改管脚复用配置 1 打开lichee/tools/product/conf

OMAPL138管脚复用配置

OMAP-L138 C6000 DSP+ARM Processor Technical Reference Manual (Rev.A).pdf 里的252页有相应的管脚配置说明 MUX_CFG(DA850, UART1_RXD, 4, 24, 15, 2, false) MUX_CFG(DA850, UART1_TXD, 4, 28, 15

Xilinx FPGA 管脚的默认电平配置方法 XDC约束

目录 未使用的引脚,XDC约束其他已使用的引脚,XDC约束 未使用的引脚,XDC约束 set_property BITSTREAM.CONFIG.UNUSEDPIN PULLDOWN [current_design]set_property BITSTREAM.CONFIG.UNUSEDPIN PULLUP [current_design]set_property BITST

FPGA复位专题---(41)复位管脚PR报错?

(41)复位管脚PR报错? 1 目录 (a)FPGA简介 (b)Verilog简介 (c)复位简介 (d)复位管脚PR报错? (e)结束 1 FPGA简介 (a)FPGA(Field Programmable Gate Array)是在PAL (可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出

linux开发之设备树六、linux下pinctrl子系统管理设置pin管脚的复用功能(一般原厂提供)

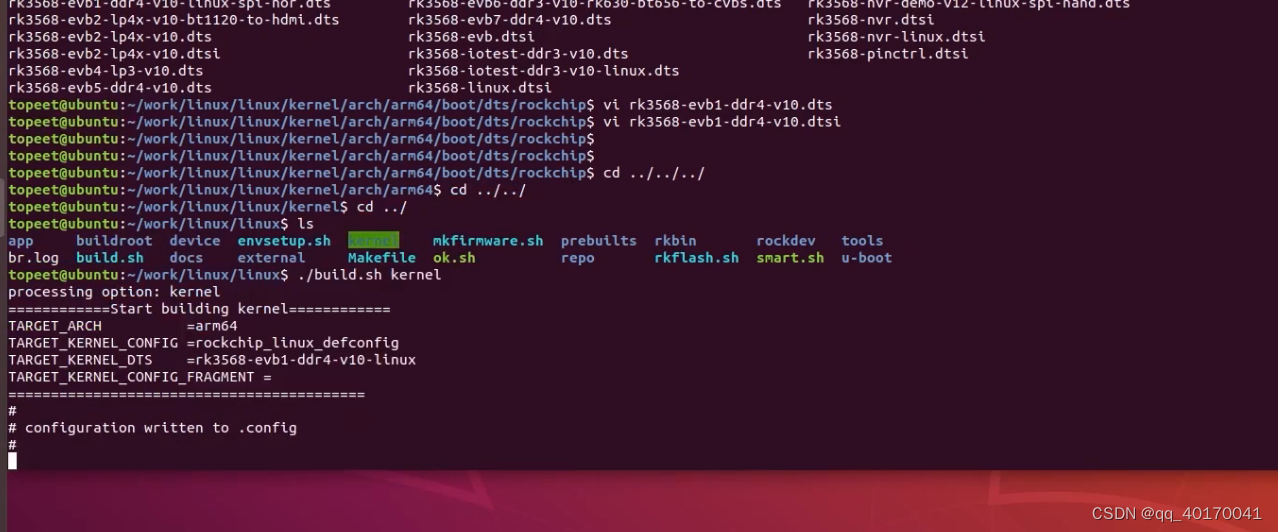

客户端的编写格式是固定的,不管哪家原厂的处理器,格式都是一样的 对于服务端部分是原厂提供,各个芯片肯定就不一样了,主要在于编写的格式不同 pinctrl客户端写法 使用pinctrl设置管脚复用 在kernel/arch/arm64/boot/dts/rockchip路径下面放置了dts和dtsi文件 1、去掉 RK3568 Linux 源码包中的 led 灯的节点。然后我们自己写一个

在BootLoader中使用gpio--获取gpio的高低电平,以及设置相应的管脚的电平高低

以下以rv1108平台为例: 在项目中,需要实现一个功能,在Linux kernel加载前BootLoader判断一个引脚电平的高低状态,从而决定加载不同的kernel,以及相应的文件系统,以实现双系统的功能。 //判断按键的电平高点状态:#if 1//set gpio3_a4's direction intputu32Reg = read_XDATA32(0x10330000 + 0x00

如何分配FPGA管脚

如何有效的利用 FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑这种方法往往是不可取的,RTL验证与验证板设计必须是同步进行的,在验证代码出来时验证的单板也必须设计完毕,也就是管脚的分配也必须在设计代码出来之前完成。所以,管脚的分配更多的将是依赖人,而非工具,这个时候就更需要考虑各方面的因素。 1

FPGA中的VREFB管脚的作用

首先说IO standard:这个是用于支持对应不同的电平标准。FPGA IO口的电压由IO bank上的VCC引入。一个bank上引入3.3V TTL电平,那么此时整个bank上输出3.3V的TTL电平。设置这个第一是为了和current strength一起计算功率。第二个是用于在IO口上加载正确的上拉/下拉电阻。只要你设置完成,Quartus会按照你的电平标准自动布线。 第二是IO

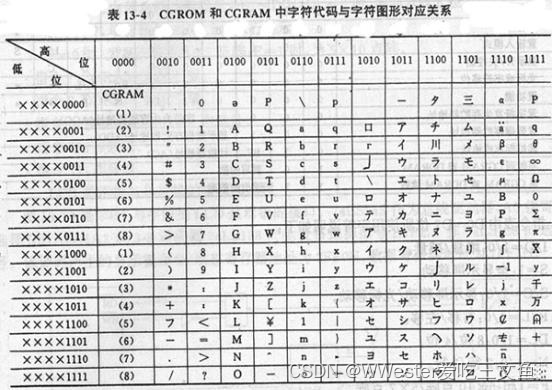

STM32 LCD1602 _1_液晶屏简介和管脚配置

LCD1602介绍 LCD1602中02的意思是可以显示2行,如果是1604就是4行,16的意思是在每行中可以显示16个字符。 市面上字符液晶绝大多数是基于 HD44780 液晶芯片的,控制原理是完全相同的,因此 HD44780 写的控制程序 可以很方便地应用于市面上大部分的字符型液晶。字符型 LCD 通常有 14 条引脚线或 16 条引脚线的 LCD,多出来

【Vivado常见问题】【DRC NSTD-1 DRC UCIO-1】无法生成bitstream(部分管脚位置或电平未指定)

假如工程就是有些信号暂时没法指定管脚呢,比如顶层设计端口包含串口,LED、按键,此时只想验证按键和串口,LED由于当前硬件限制没有对应的物理电路,没法确定管脚。这种情况可以使用一句脚本语言来暂时忽略该限制。 set_property SEVERITY {Warning} [get_drc_checks NSTD-1]set_property SEVERITY {Warning} [get_dr

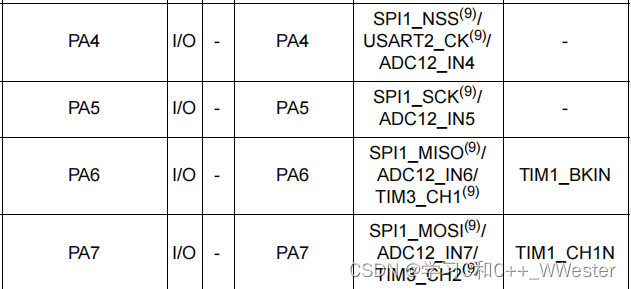

STM32 SPI通信协议1——协议基本原理及管脚定义

SPI介绍 SPI全称为Serial Peripheral interface,译为串行外围设备接口。SPI主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号编码器之间。 SPI是一种高速,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便。STM32

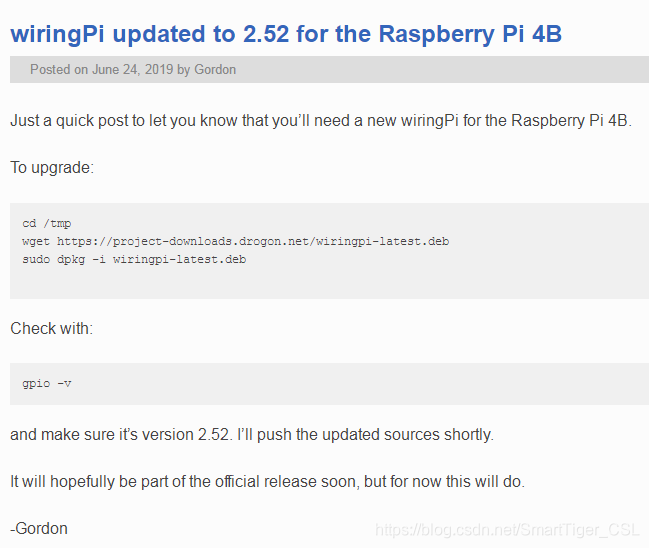

树莓派4B 使用gpio readall无法查询到管脚信息的问题及解决办法

树莓派4B 安装的系统版本是2019-06-20-raspbian-buster-full.img 1.安装网上的步骤(https://blog.csdn.net/m0_37509650/article/details/85403217)修改了串口映射,想测试串口通信功能,但发现使用gpio readall命令时,出现无法查询到管脚信息的错误: pi@raspberrypi:~ $ gpio r

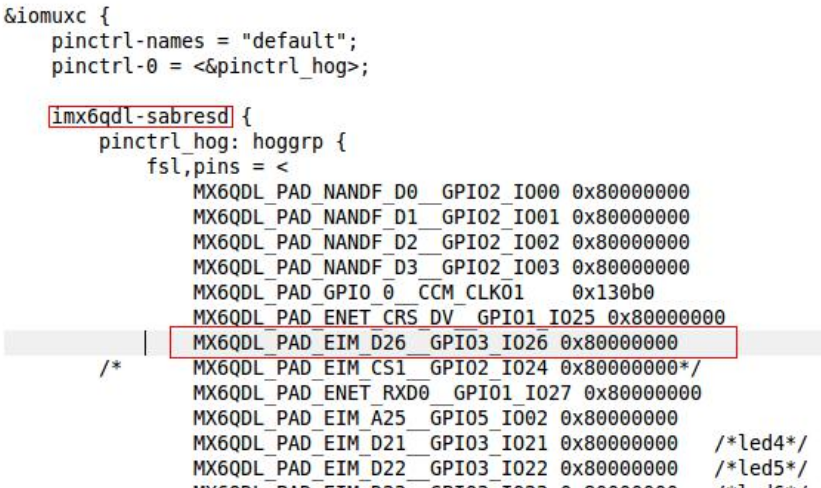

IMX6Q,在uboot下在内核下,修改管脚成GPIO

博主使用的是天嵌的IMX6Q_coreC,CPU是IMX6Q, 内核下修改GPIO: 内核版本4.1.15 以下使用 EIM_D26 为例介绍修改一个已经被驱动占用的管脚,将其修改为 gpio 1.在 imx6q-pinfunc.h 文件中搜索 EIM_D26,搜索的结果如图所示: 从图片可以看出EIM_D26 是GPIO3_26管脚。 2.

【AMD Xilinx】ZUBoard(2):通过AXI GPIO控制PL端的管脚输出

【AMD Xilinx】ZUBoard(2):通过AXI GPIO控制PL端的管脚输出 一、基本功能和流程二、Vivado工程1. 总体框图2. AXI GPIO相关部分3. 配置AXI GPIO4. 绑定管脚4.1 根据原理图查找对应管脚4.1.1 LED04.1.2 LED1 4.2 I/O Planning 5. XDC 三、ARM代码1. 地址空间2. 函数说明3. 实际的C代码实现

Quartus II中FPGA管脚的分配策略

1. FPGA管脚介绍 2. FPGA管脚分配方法 3. 编写FPGA管脚分配文件 4. 保存FPGA管脚分配文件 https://wenku.baidu.com/view/394b592c6137ee06eef9182b.html

HC89S003F4管脚快速设置函数GPIO,方便懒人

不用记那么多寄存器的名称了,直接输入管脚号和管脚状态就可以了。例子在最下面几行 变量 P 被厂家用了,只能使用GPIO了。 本函数占用约200字节,地方不够的慎用 /******管脚设置函数 by abin******/ #define P00 0 #define P01 1 #define P02 2 #define P03 3 #define P04

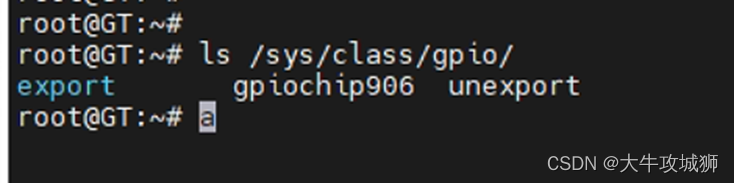

Zynq-7000、FMQL45T900的GPIO控制(三)---linux管脚编号计算

本文主要对在Linux下使用zynq-7000或者FMQL45T900控制MIO/EMIO 首先内核配置项 如下,这个不用太多关注,一般都是默认打开的 CONFIG_GPIO_SYSFS=yCONFIG_SYSVIPC=yCONFIG_GPIO_ZYNQ=y 两者的控制都是流程都是一样的,在细节上又区别 首先都在/sys/class/gpio/查看对应节点 FMQL45T900

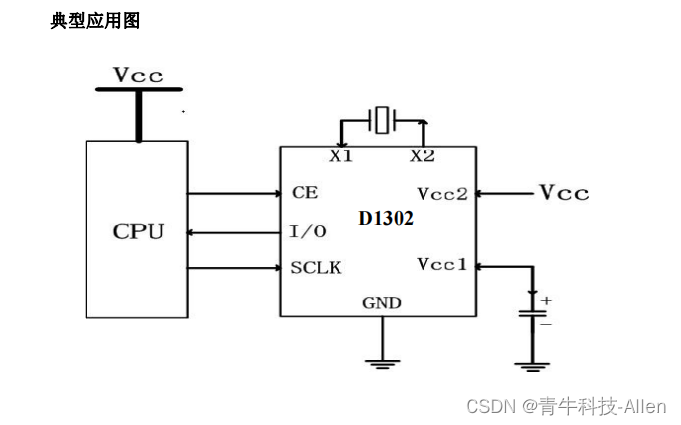

涓流充电计时电路芯片D1302,具有双管脚主电源和备用电源,可编程涓流充 电器VCC1,还有 31 字节的暂存器等功能

D1302 涓流充电计时电路包含一个实时时钟 / 日历和 31 字节的静 态RAM ,通过简单的串行接口与微处理器通讯。这个实时时钟 / 日历 提供年月日、时分秒信息,对于少于31 天的月份月末会自动调整, 还有闰年校正。由于有一个 AM/PM 指示器,时钟可以工作在 12 小 时制或者 24 小时制。除计时功能外,还有如下特点:双管脚主电源和备用电源,可编程涓流充 电器

易灵思Inout管脚操作指南

易灵思Inout管脚操作指南 一.原理说明二.软件设置界面三.逻辑内的设置 一.原理说明 易灵思器件在设计时,逻辑层和硬件(硬核接口,管脚接口)层是分开独立的,无论是MIPI,,DDR,PLL 和 JTAG,对于用户来说,可以把硬件层当做外围器件来看待,只需要关注和逻辑层关联的接口的时序; LVDS 和 GPIO 一样,当然也都是同样的设计理念; 二.软件设置界面 1.

管脚的上拉下拉,推挽输出

1.对于传感器的信号输入引脚,悬空状态会导致读取错误的情况,若输入高电平有效,就将输入引脚置低,若输入低电平有效,输入引脚置高。 2.一般都是将输出方式变为推挽输出, 在开漏输出模式下,P-MOS管不工作,只有N-MOS管起作用。若输出数据寄存器的值为0,则N-MOS导通,IO口输出低电平;若输出数据寄存器的值为1,则N-MOS截止;由于P-MOS不工作,此时IO口既不是高电平,也不是低电平,