摆幅专题

DDR3的DQS_p/n信号电平摆幅变化不一致现象

环境: zynq7100, MT41J64M16 现象: (1) 处理器读DDR3的操作,DQS_p/n信号与DQn信号一道,由DDR3发出,处理器接收。 测量发现,DQS信号电平摆幅低低高高的现象,摆幅高时能达到正常摆幅要求,低时只是正常摆幅的一半左右。 (2) 处理器写DDR3的操作,DQS_p/n与DQn一道,由处理器发出,DDR3接收。 测量信号正常,DQS信号差分摆幅一

【氮化镓】栅极漏电对阈值电压和亚阈值摆幅影响建模

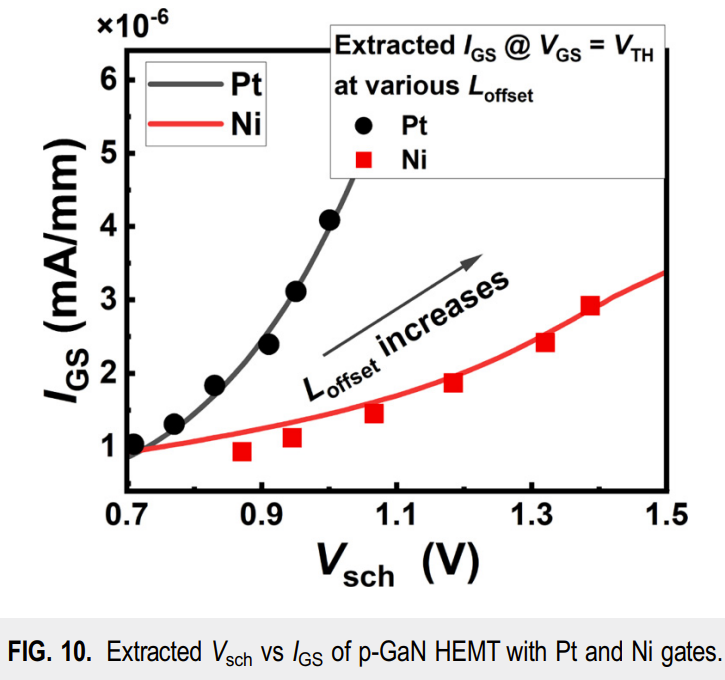

本文是一篇关于p-GaN门AlGaN/GaN高电子迁移率晶体管(HEMTs)的研究文章,发表于《应用物理杂志》(J. Appl. Phys.)2024年4月8日的期刊上。文章的标题为“Analysis and modeling of the influence of gate leakage current on threshold voltage and subthreshold swing

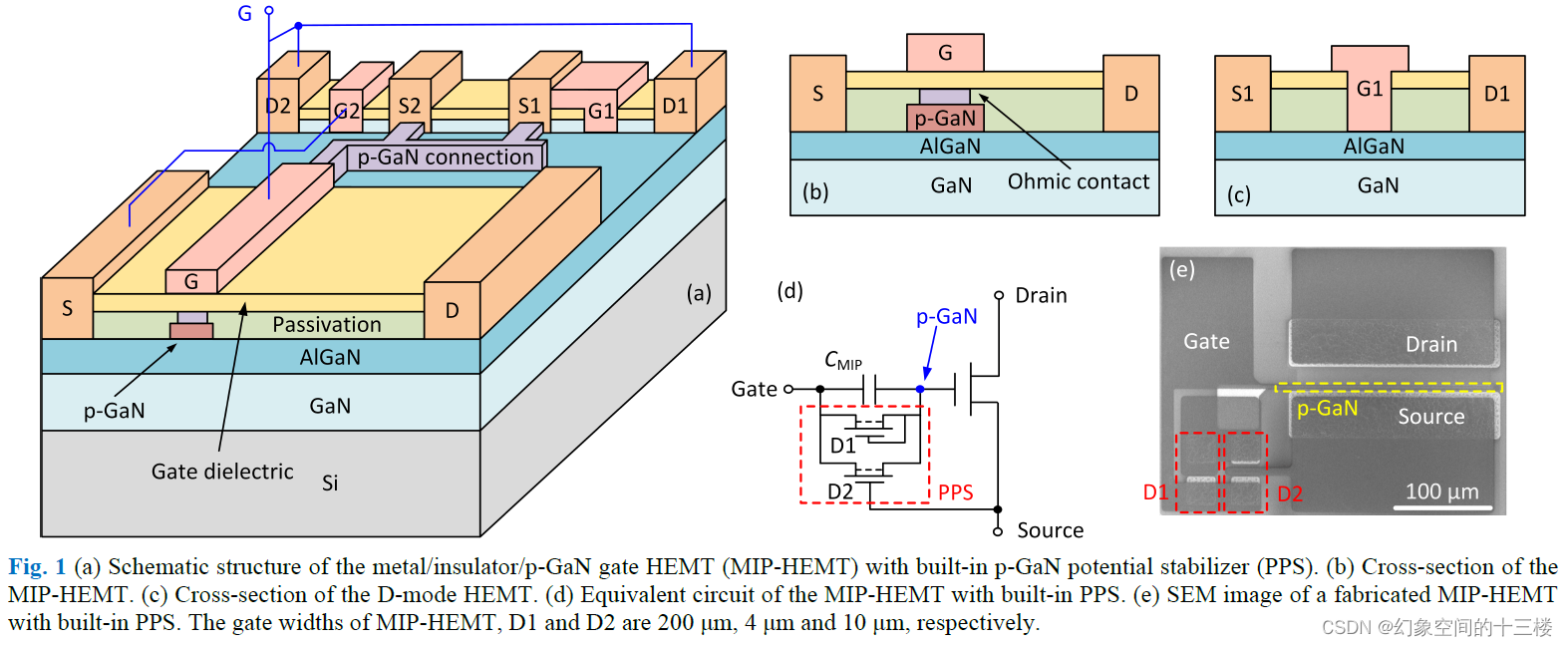

在金属/绝缘体/p-GaN栅极高电子迁移率晶体管中同时实现大的栅压摆幅和增强的阈值电压稳定性

标题:Simultaneously Achieving Large Gate Swing and Enhanced Threshold Voltage Stability in Metal/Insulator/p-GaN Gate HEMT (IEDM2023) 摘要 摘要:对于增强型GaN功率晶体管的发展,栅压摆幅和阈值电压稳定性通常是互相排斥的。本文展示了一种具有内置p-GaN电位稳定器(