异构计算专题

实时计算及异构计算随笔笔记

3、异构计算的典型应用 异构计算并不神秘,目前已渗透各个领域,不仅是PC领域,也包括了手持移动设备领域、行业领域,甚至是云计算、分布式计算领域。事实上,异构计算至少在应用端(前台)并不像它的名字这样生涩,很多应用里面,都有异构计算的身影。小到网页及视频加速,大到DNA计算、蛋白质计算、气象运算,都能和异构计算搭上关系。但都有一定的限制,如_global_

9U_VPX信号处理机,传感器大数据异构计算平台

9U_VPX信号处理机 1 介绍 1.1 产品概述 9U_VPX信号处理机是一款面向前端射频系统的高速记录、存储和处理系统。信号处理机为应对军用电子信息系统面临的目标种类多样化、战场环境复杂化、执行任务多元化等多重难题,而研发出来的***数据记录存储系统。信号处理机担负传感器大数据的记录存储/回放和管理任务。 信号处理机由多端口光纤模块,高速实时信息处理模块,综合管理配置模块以及大容量数据

什么是异构计算架构?

🍉 CSDN 叶庭云:https://yetingyun.blog.csdn.net/ 异构计算架构是一种计算系统设计理念,它结合了使用不同类型指令集和体系架构的计算单元,例如 CPU、GPU、NPU、DSP、ASIC 和 FPGA,以实现高效的计算性能和能耗比。这种架构允许这些不同的计算单元共享一个统一的内存系统,但要求程序必须为每种不同的指令集分别编写,以充分利用每个计算单元的特点和优

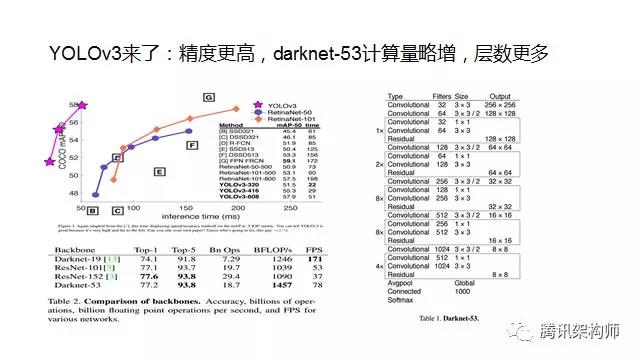

异构计算架构师眼中的AI算法(object detection)

导语:虽然detection在classification基础上焕发了春天,但算法的复杂度确实增加了不少。对于底层平台来说,虽然看起来还是一堆卷积,但图片的增大,带来了一些列问题。 目标检测object detection由于除了要识别what,还要找出where,从算法本身上复杂了许多。虽然最终实现端到端检测的网络是一个卷机网络,貌似和之前没有多大差别,但大图片除了计算量增加xx倍

c++异构计算获取计算进度

异步运行任务,并定期检查任务是否已完成。如果没有,您希望打印出任务的进度。但是,您提供的代码存在一些问题: 1。“TaskRun”类未在您提供的代码段中定义。请确保其定义正确,并且“run”方法是“TaskRun”的成员函数。 2.“taskManage”对象未在代码段中定义。请确保它已正确初始化,并且可以在代码范围内访问。 3.“relSimVec”对象未在代码段中定义。请确保它已正确初始

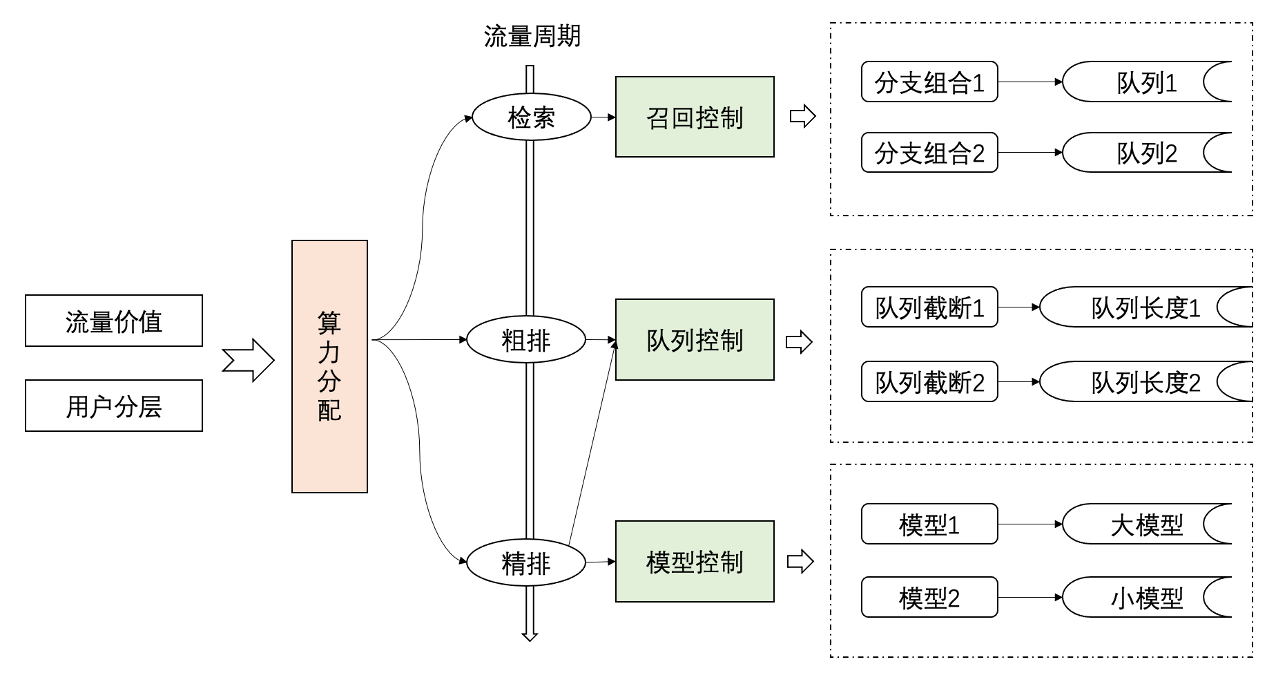

京东广告算法架构体系建设--在线模型系统分布式异构计算演变 | 京东零售广告技术团队

一、现状介绍 算法策略在广告行业中起着重要的作用,它可以帮助广告主和广告平台更好地理解用户行为和兴趣,从而优化广告投放策略,提高广告点击率和转化率。模型系统作为承载算法策略的载体,目前承载搜索、推荐、首焦、站外等众多广告业务和全链路的深度学习建模,是广告算法算法创新和业务迭代发展的重要基石。 架构全景图: 1.平台能力: 1.高吞吐高并发:百亿PV,百万QPS 2.低延迟,高可靠

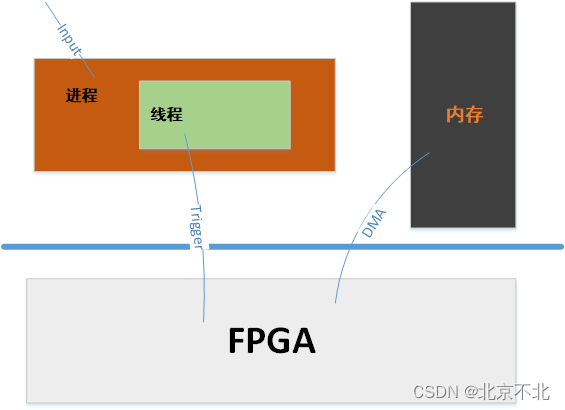

异构计算关键技术之多线程技术(四)

异构计算关键技术之多线程技术(四) 最近遇到了一个项目,需要写一个用户态的测试程序(独立进程),用来测试FPGA PCIe DMA的性能,具体的要求如下: 1. 需要一个主线程,用来配置FPGA的寄存器,同时启动从线程;2. 如果不进行人为干涉,子线程一直进行FPGA的相关操作,比如下发trigger信号、配置burst次数、数据长度;3. 进行人为干涉,子线程退出,并返回子线程执行

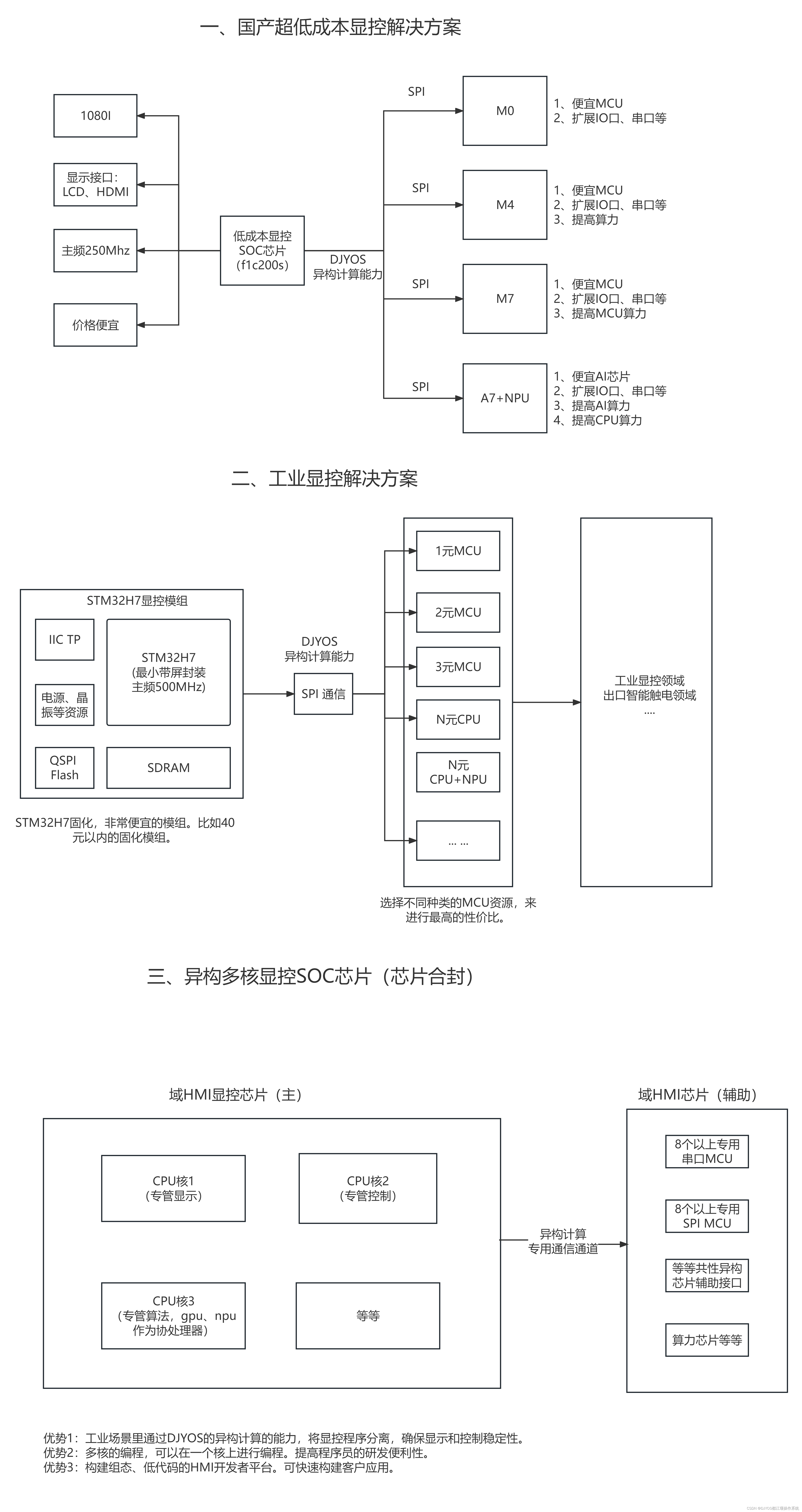

DJYOS物联屏:工业HMI里的显控异构计算的超稳定解决方案

1、超稳定性:DJYOS物联屏的超稳定依赖于都江堰泛计算操作系统天然支持多核、多机的异构计算能力,可以一核运行HMI、一核运行控制程序,多核之间可以通过djyos的异构计算去中心化运行(确保各自程序不干扰运行),又可以相互调度进行信息交互,确保程序稳定又互联互通。 2、超高性价比(超低成本):DJYOS的异构计算,可以使用非常便宜的显控芯片,以及最小封装。然后通过便宜的MCU,进行外设扩展。整体还

深入理解CPU和异构计算芯片GPU/FPGA/ASIC (下篇)

深入理解CPU和异构计算芯片GPU/FPGA/ASIC (下篇) 3.2.1 CPU计算能力分析 这里CPU计算能力用Intel的Haswell架构进行分析,Haswell架构上计算单元有2个FMA(fused multiply-add),每个FMA可以对256bit数据在一个时钟周期中做一次乘运算和一次加运算,所以对应32bit单精度浮点计算能力为:(256bit/32bit) 2(FMA)