异或门专题

第一篇 逻辑门(与门、或门、非门、异或门)

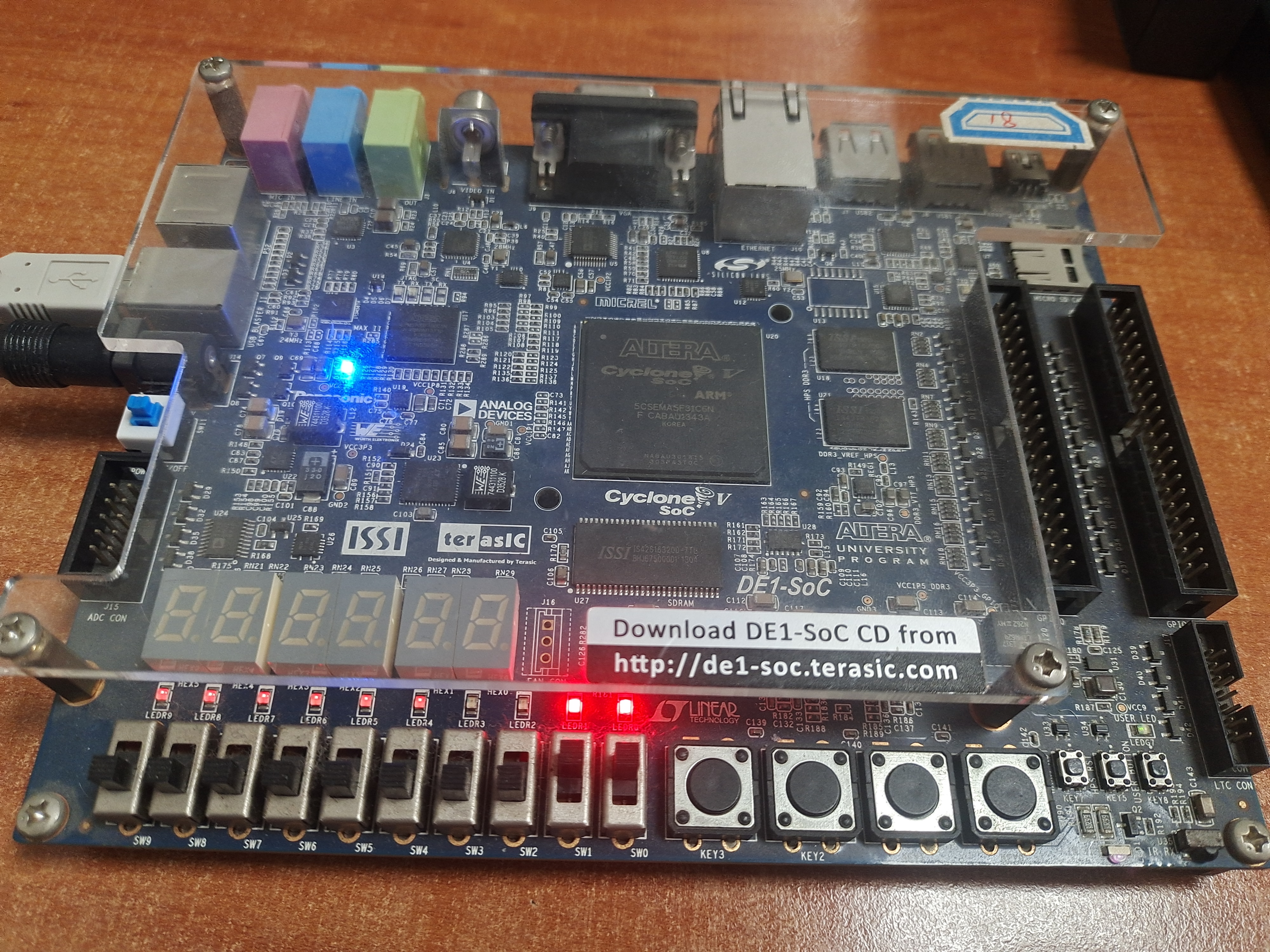

一、实验目的 了解DE1-SOC开发板一些外设。 掌握常用组合逻辑门电路的基本原理。 学习Verilog HDL的基本语法。 学习使用ModelSim工具对设计的电路进行仿真,包括编写Testbench仿真代码,以及ModelSim工具的使用。 熟悉使用Quartus软件从创建Quartus工程到最终配置FPGA并观察实验现象的流程。 二、逻辑门电路介绍 逻辑门电路是数字电路中最

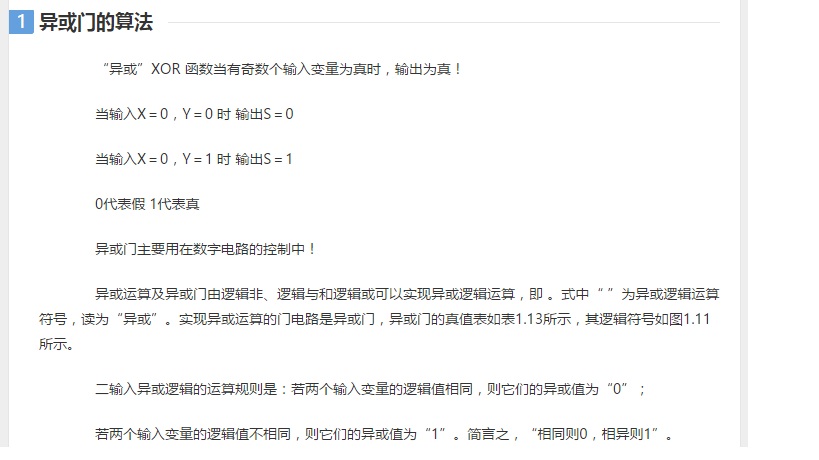

【电路笔记】-异或门

异或门 文章目录 异或门1、概述2、数字逻辑异或门3、异或门等效电路 异或逻辑函数是一个非常有用的电路,可用于许多不同类型的计算电路。 1、概述 异或门是算术运算中常用的另一种数字逻辑门,因为它可以用来给出两个二进制数的和以及错误检测和纠正电路。 在前面的文章中,我们看到通过使用三个主要门,与门,或门和非门,我们可以构建许多其他类型的逻辑门功能,例如与非门和或非门或任何

TensorFlow代码实现(二)[实现异或门(XOR)]

第一个实验:用神经网络实现异或门 测试数据如下: [0,0]->[0] [1,0]->[1] [1,1]->[0] [0,1]->[1] 数据量很小,但异或门远没有我想象的好写,原来在第一层的时候我使用的激活函数是relu,第一层有两个神经元;输出层使用的激活函数是softmax;学习率是0.01;loss function选的是梯度下降算法,weights和biases都是随机产生的

![TensorFlow代码实现(二)[实现异或门(XOR)]](/front/images/it_default.gif)