光刻专题

麻省理工学院将电子束光刻推进至9纳米

麻省理工学院(MIT)的研究人员们宣称已经开发出了一种新技术,能将用于芯片图案蚀刻的高速电子束光刻的分辨率尺度推进到9nm(纳米),远远超出人们此前的预想。MIT表示,电子束光刻工具之前最小的形体尺寸是25nm,而他们的新发现将会大大延长电子束光刻技术在半导体制造业中的寿命。 MIT透露,他们的这次突破主要得益于两点,一是使用更薄的绝缘层来尽量避免电子散射,二是使用特殊材料对接收电子较多的

半导体光刻机行业深度报告:复盘ASML,探寻本土光刻产业投资机会

报告来源:西南证券 1、 提要:光刻工艺是晶圆制造最核心环节,光刻产业链协同发展成为光刻机突破关键因子 1.1 光刻定义晶体管尺寸,光刻工艺合计占芯片成本近 30% 2019 年全球半导体市场规模达 4090 亿美元,成为数码产业的基石。第二次工业革命就 是数码产业的革命,据麦肯锡预测,2020 年全球数码产业将占全球企业总产值的 41%,而 半导体则成为数码产业的基石。根据 WSTS 统计

EUV光刻,没有那么重要?

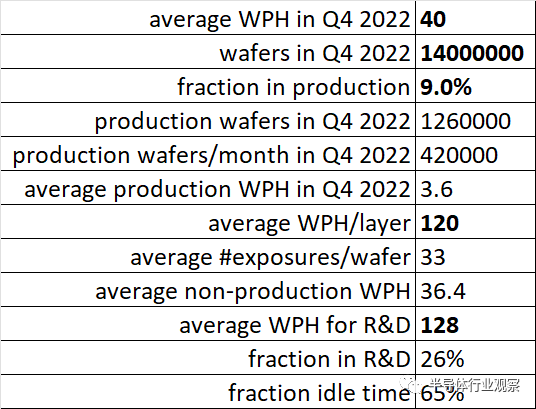

关注、星标公众号,精彩内容每日送达来源:内容由半导体行业观察(ID:icbank)编译自semiwiki,谢谢。 在 2023 年 SPIE 高级光刻和图案化会议上,ASML 展示了其该领域 EUV 光刻系统的最新动态 。EUV 晶圆曝光输出如下表所示: 根据这些信息,我们可以尝试提取和评估每季度的 EUV 晶圆产量。首先,由于有些季度没有报告产出,我们将使用四次多项式拟合进行插值。使用四次

7纳米duv和euv_EUV光刻技术竞争激烈,三星7纳米EUV制程已完成新思科技物理认证,台积电紧追其后...

在晶圆代工市场,台积电与三星的竞争始终是大家关心的戏码。三星虽然有高通等VIP客户,但在7纳米制程节点,高通预计会转投台积电,三星要想受更多客户的青睐,只能从制程技术着手了。这也是三星为什么跳过非EUV技术的7纳米制程,直接上7纳米LPPEUV制程技术的原因。如今,三星终于公布了7纳米LPP制程已完成新思科技(Synopsys)物理认证,意味着7纳米EUV制程将可全球量产了。 目前全球前几大晶

半导体制造工艺(一)光刻

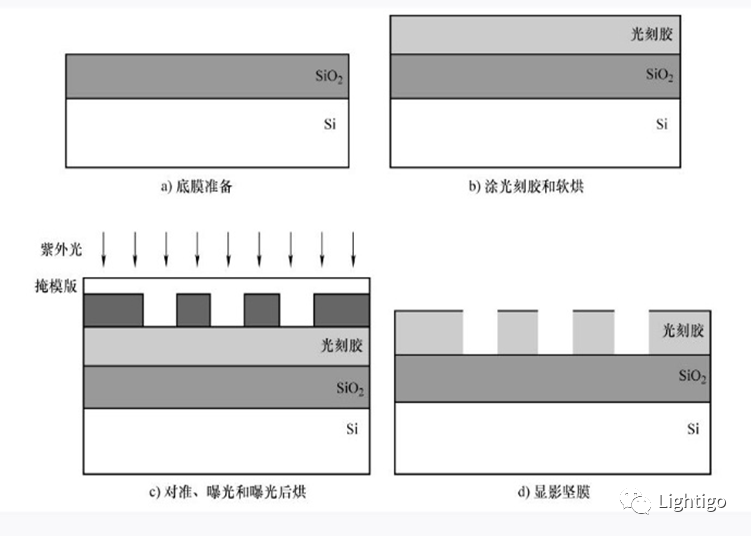

在这里开个新专题,主要详细描述半导体制造整个流程中所用到的设备工艺步骤。 在集成电路制造工艺中,光刻是决定集成器件集成度的核心工序,该工序的作用是将图形信息从掩模版(也称掩膜版)上保真传输、转印到半导体材料衬底上。光刻工艺的基本原理是利用涂敷在衬底表面的光刻胶的光化学反应作用,记录掩模版上的器件图形,从而实现将集成器件图形从设计转印到衬底的目的。 光刻工艺的关键指标包括分辨率、灵敏

2024北京国际光刻设备及光掩膜技术展览会

2024北京国际光刻设备及光掩膜技术展览会 Beijing Photolithography Equipment and Mask Application Technology Exhibition2024 基本信息 时间:2024年7月24-26日 地点:北京国家会议中心 展会简介 微电子技术的发展一直是光刻设备和技术变革的动力,21世纪光刻技术将继续居于诸多技术之首。光刻技术从诞生以来,