二路专题

UVA11997K Smallest Sums(优先队列+二路归并)

题目:UVA11997K Smallest Sums(优先队列+二路归并) 题目大意:求K个最小和。给出K行,每行有K个数,在每行中取一个元素相加,求这些和中最小的k的值。 解题思路:每一行排列一下,那么对于两张表a1< a2 < a3 < a4... ,可以将a1 + b1(最小的), a1+ b2, a1 + b3...a1 + bk存到优先队列中,然后最小的出队,就尝试将剩余

「数组」数组双指针算法合集:二路合并|逆向合并|快慢去重|对撞指针 / LeetCode 88|26|11(C++)

目录 概述 1.二路合并 思路 复杂度 Code 2.逆向合并 思路 复杂度 Code 3.快慢去重 思路 复杂度 Code 4.对撞指针 思路 复杂度 Code 总结 概述 数组的线性枚举是我们学习编程时遇到的第一种枚举手段。但是它看起来有点愚蠢:只有一个索引i承担全部的工作,如果有第二个索引j,它总是被嵌套在一次for循环的内部。 像这样: fo

二路归并排序的算法设计和复杂度分析(C语言)

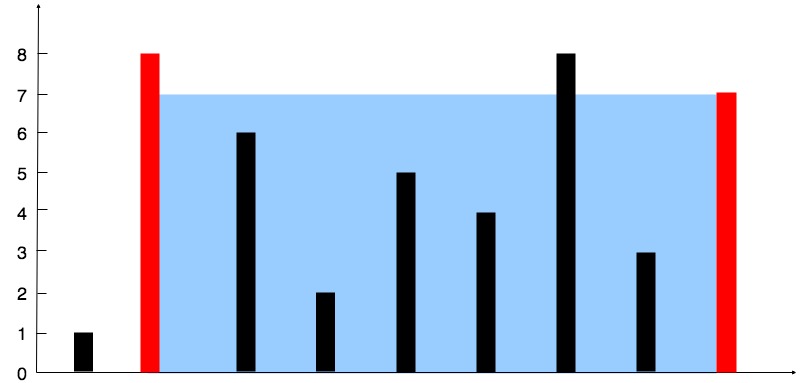

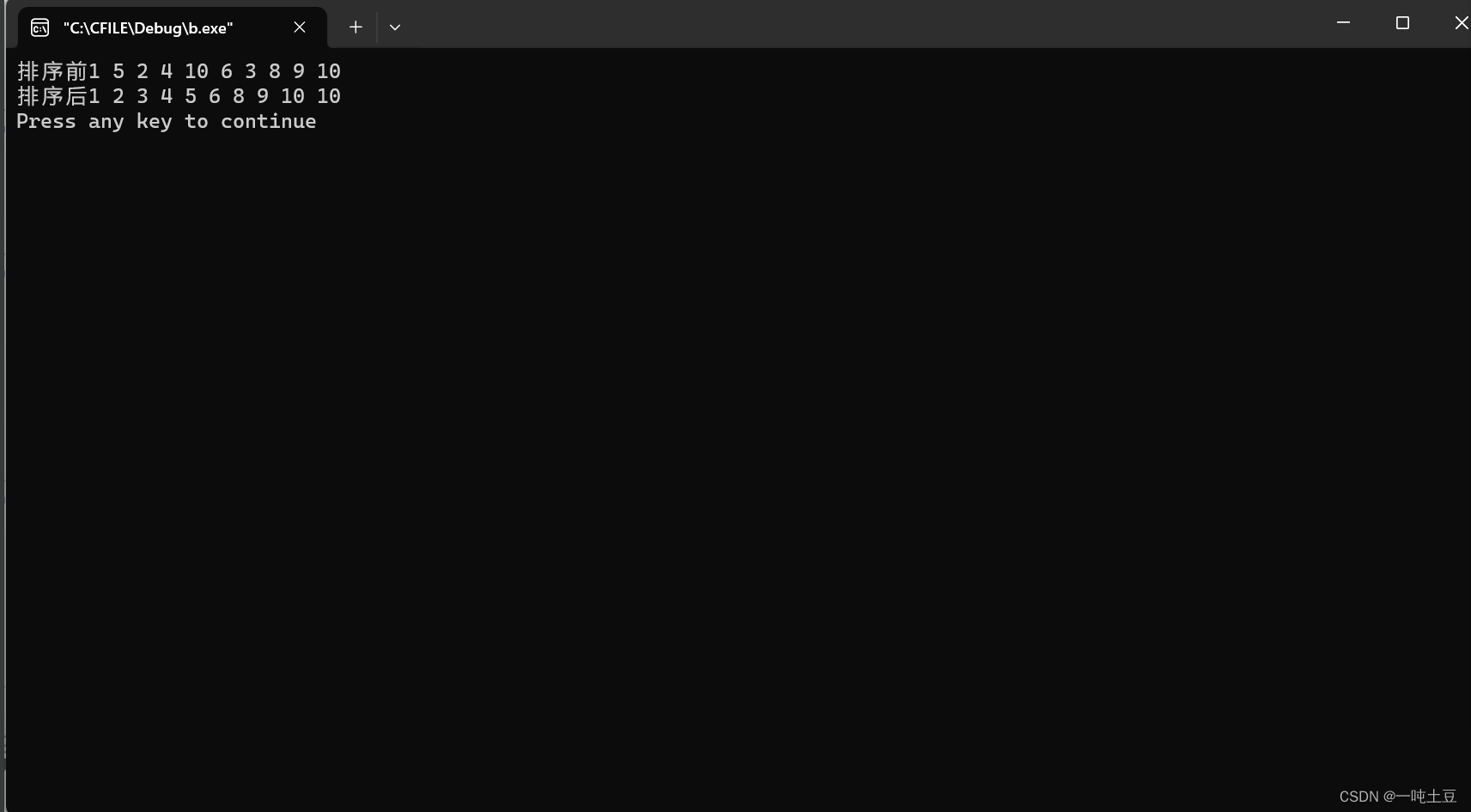

目录 实验内容: 实验过程: 1.算法设计 2.程序清单 3.运行结果 4.算法复杂度分析 实验内容: 二路归并排序的算法设计和复杂度分析。 实验过程: 1.算法设计 二路归并排序算法,分为两个阶段,首先对待排序列进行拆分,然后进行合并排序。 第一阶段:将待排序列分长度成大致相等的两个子序列,按照同样的拆分方法,对每个子序列进行拆分,直到子序列中只有一个元素

4-20mA转0-10V二路分配器、4-20ma转0-5V隔离放大转换变送模块

4-20mA转0-10V、0-5V隔离放大转换变送模块 工业生产中为增加设备带载能力并保证连接同一信号的设备之间互不干扰,提高电控安全性能,需要将仪器仪表或传感器输出的电压电流、频率、电阻等信号进行采集运算、隔离放大、转换变送及去干扰处理后,得到行业通用的标准模拟电流或电压信号,安全送给二次仪表或PLC/DCS/PC机使用。用户使用模拟信号隔离器/隔离放大器/隔离变送器/数据采集器等产品,有时会遇

二路归并排序的算法设计和复杂度分析and周记

数据结构实验报告 实验目的: 通过本次实验,了解算法复杂度的分析方法,掌握递归算法时间复杂度的递推计算过程。 实验内容: 二路归并排序的算法设计和复杂度分析 实验过程: 1.算法设计 第一步,首先要将数组进行划分,假设等待排序的数组是A[SIZE],我们每次从数组的中间开始划分。 1).假设等待划分的数组是A{high …low} (是A中的一小段),划分点是它的中点,mid=(

C++ 非递减序列 二路归并

文章目录 一、二路归并 源码二、算法思路:三、完整源码:四、知识点小笔记:1.vector<int> merged(m + n, 0);2.for (int num : nums1)3.vector<int> nums1 = {1, 3, 5, 0, 0, 0}; int m = 3; 一、二路归并 源码 void merge(vector<int>& num1, int

Verilog HDL小练习(一)二路选择器amp;amp;三位加法器

二路选择器是一种及基础的逻辑电路其基本功能描述为,当选择0时输出a,选择1时输出b RTL级描述如下: module muxtwo(out,a,b,sl);input a,b,sl;output out;//============================reg out;always@(sl or a or b)//表示只要有一个变化就执行下面的语句if(!sl)out=

服务器摆放需要预留U位么_多核全能,引领风尚:基于AMD二代EPYC的戴尔易安信二路服务器首测...

经过多年的蛰伏,AMD于2017年重回服务器市场,并带来了基于全新“Zen”架构的第一代EYPC服务器处理器(代号Naples,即那不勒斯)。在无限渴求性能增长的数据中心市场,更多内核、更多内存通道以及更多的PCIe通道数,无疑为提升性能打开了一扇新的大门。 如同十多年前AMD提出“x64”一样,EPYC迅速得到了市场的响应。作为全球最大的服务器制造商,也与AMD有着多年合作历史的Dell E

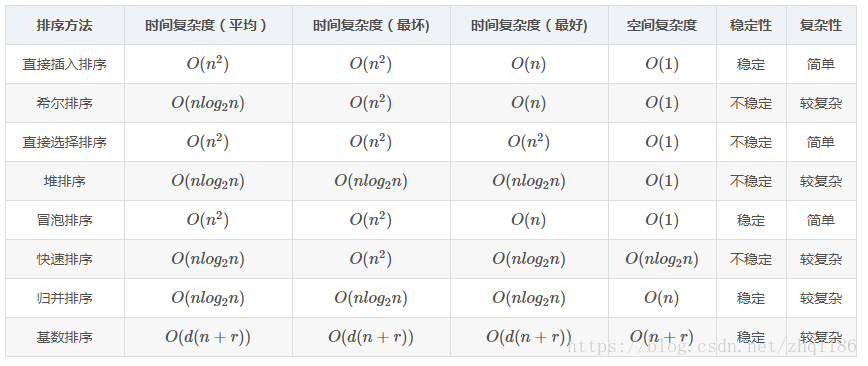

C语言——十四种内部排序算法【插入排序 希尔插入 折半二分插入 二路插入 表插入排序 简单选择排序 直接选择 树形选择插入 堆排序 冒泡 快速 归并排序 基数排序 计数排序 桶排序】

文章目录: 一:插入排序 1.直接插入排序 算法演示 2.希尔排序 算法演示 3.折半插入排序(二分查找) 图解 4.二路插入排序 算法演示 5.表插入排序 算法演示 二:选择排序 1.简单选择排序 算法演示 2.直接选择排序 算法演示 3.树形选择排序(锦标赛排序) 算法演示 4.堆排序 算法演示 三:交换排序 1.冒泡排序 算法演示 2.快速

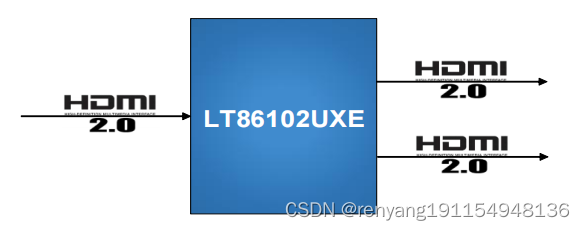

龙迅LT86102UXE HDMI2.0转二路HDMI2.0/1.4,支持音频剥离,支持4K60HZ

龙迅LT86102UXE 1.描述: 龙迅 LT86102UXE HDMI2.0 分路器具有符合 HDMI2.0/1.4 规范的 1:2 分路器、最大 6Gbps 高速 数据速率、自适应均衡 RX 输入和预加重 TX 输出(用于支持长电缆应用)、内部 TX 通道交换以 实现灵活的 PCB 布线。 LT86102UXE HDMI2.0分路器自动检测电缆损耗,并自适应优化均衡设置。CDR可清