上板专题

FPGA上板项目(三)——RAM测试

目录 实验内容实验原理实验步骤实验用时序波形HDL 代码仿真综合实现上板测试 实验内容 对 FPGA 内部的 RAM 进行数据读写操作。 实验原理 RAM (Random Access Memory),是可以进行数据交换的存储器,可读可写;而 ROM(Read-Only Memory)为只读存储器,只可读取不可写入。 实验步骤 添加 Block Memory Gene

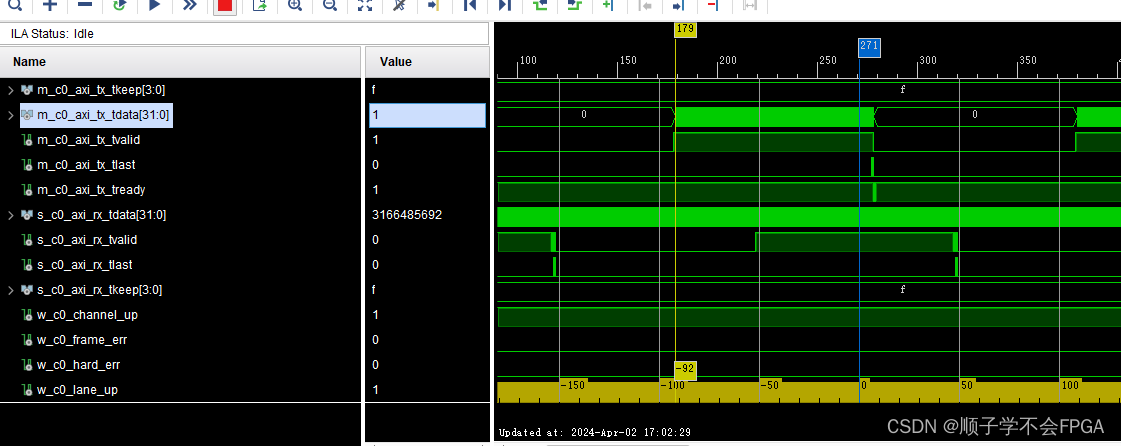

xilinx的Aurora8B10B的IP仿真及上板测试(高速收发器十七)

前文讲解了Aurora8B10B协议原理及xilinx相关IP,本文讲解如何设置该IP,并且通过示例工程完成该IP的仿真和上板。 1、生成Aurora8B10B IP 如下图所示,首先在vivado的IP catalog中输入Aurora 8B10B,双击该IP。 图1 查找Aurora 8B10B IP Aurora 8B10B相对GTX的配置相对简单,主要配置如下

基于GTX 8B10B编码的自定义PHY上板测试(高速收发器十四)

前文整理了GTX IP,完成了自定义PHY协议的收发模块设计,本文将通过光纤回环,对这些模块上板测试,首先需要编写一个用于生成测试数据的用户模块。 1、测试数据生成模块 本模块用于生成自定义PHY协议的测试数据,通过axi_stream接口向PHY发送模块生成测试数据。 对应代码如下所示,通过计数器发送每字节递增的数据,代码比较简单。 //--#################

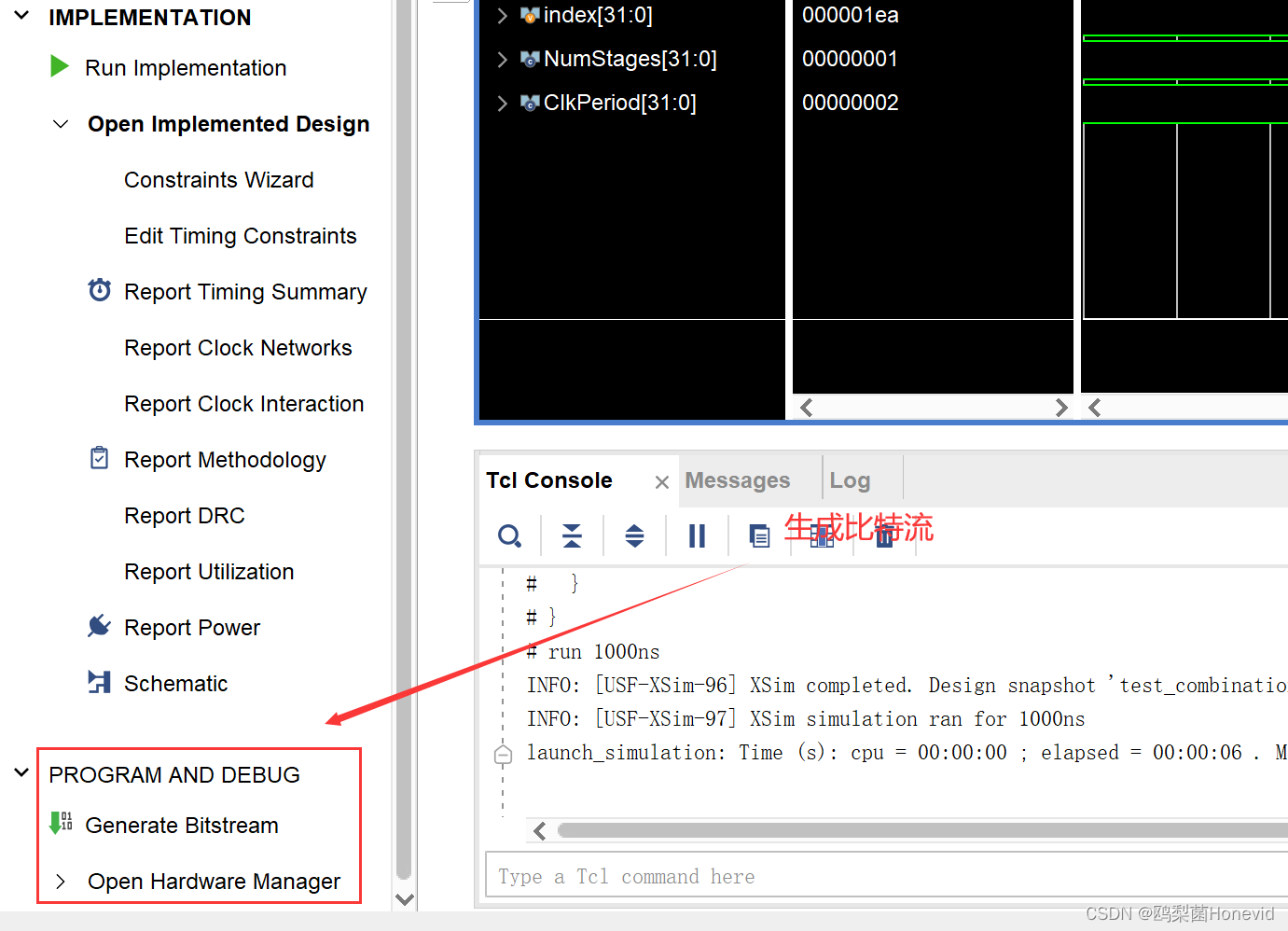

使用Vivado进行上板验证过程

环境介绍 2023.2版的vivado,是比较新的,弃用了之前三个黄色菱型的设计,采用的是AMD的图标。 Vivado v2023.2 (64-bit) SW Build: 4029153 on Fri Oct 13 20:14:34 MDT 2023 IP Build: 4028589 on Sat Oct 14 00:45:43 MDT 2023 SharedData Build: 4

Aurora8b10b(2)上板验证

文章目录 前言一、AXI_Stream数据产生模块二、上板效果总结 前言 上一篇内容我们已经详细介绍了基于aurora8b10b IP核的设计,本文将基于此进一步完善并且进行上板验证。 设计思路及代码思路参考FPGA奇哥系列网课 一、AXI_Stream数据产生模块 AXIS协议是非常简单的,看过之前的AXI_FULL协议应该会很容易理解。 该模块有以下需要注意的点:

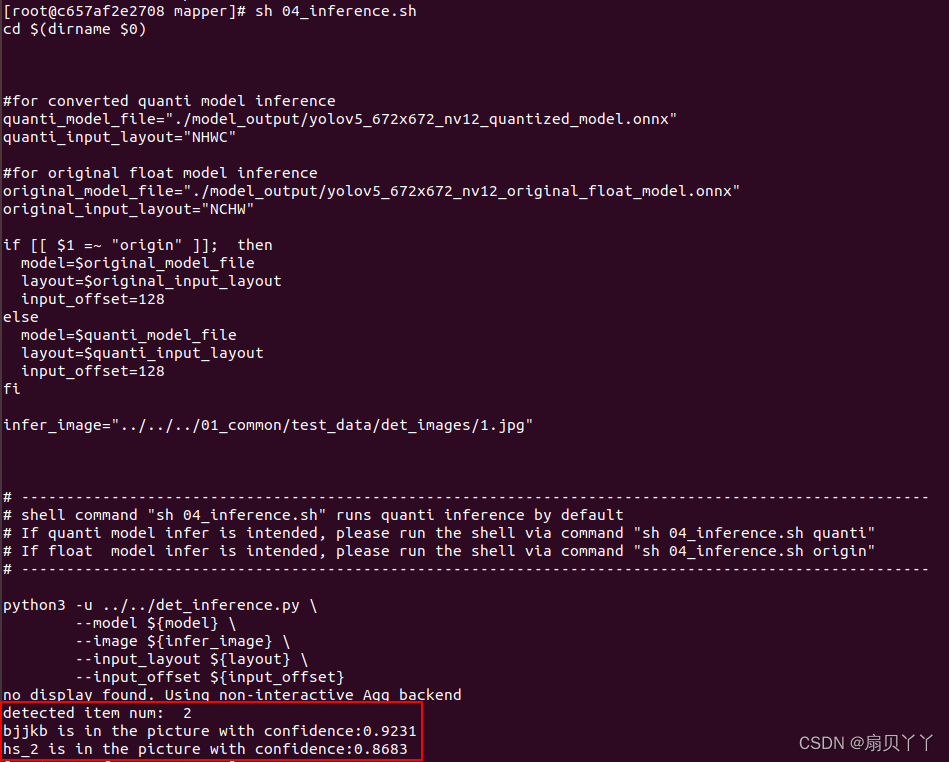

地平线X3pi基于YOLOv5-5.0版本程序上板运行推理

地平线X3pi 基于YOLOv5-5.0版本进行模型转换 注意:首先确保本地环境支持YOLOv5能够正常运行。 1. 官方模型转换onnx模型(pt->onnx) 1.1、从官方网站github上下载5.0版本源码 链接直达 1.2、转换指令: python export.py --weights yolov5s.pt --img 672 --batch 1 --opset=11

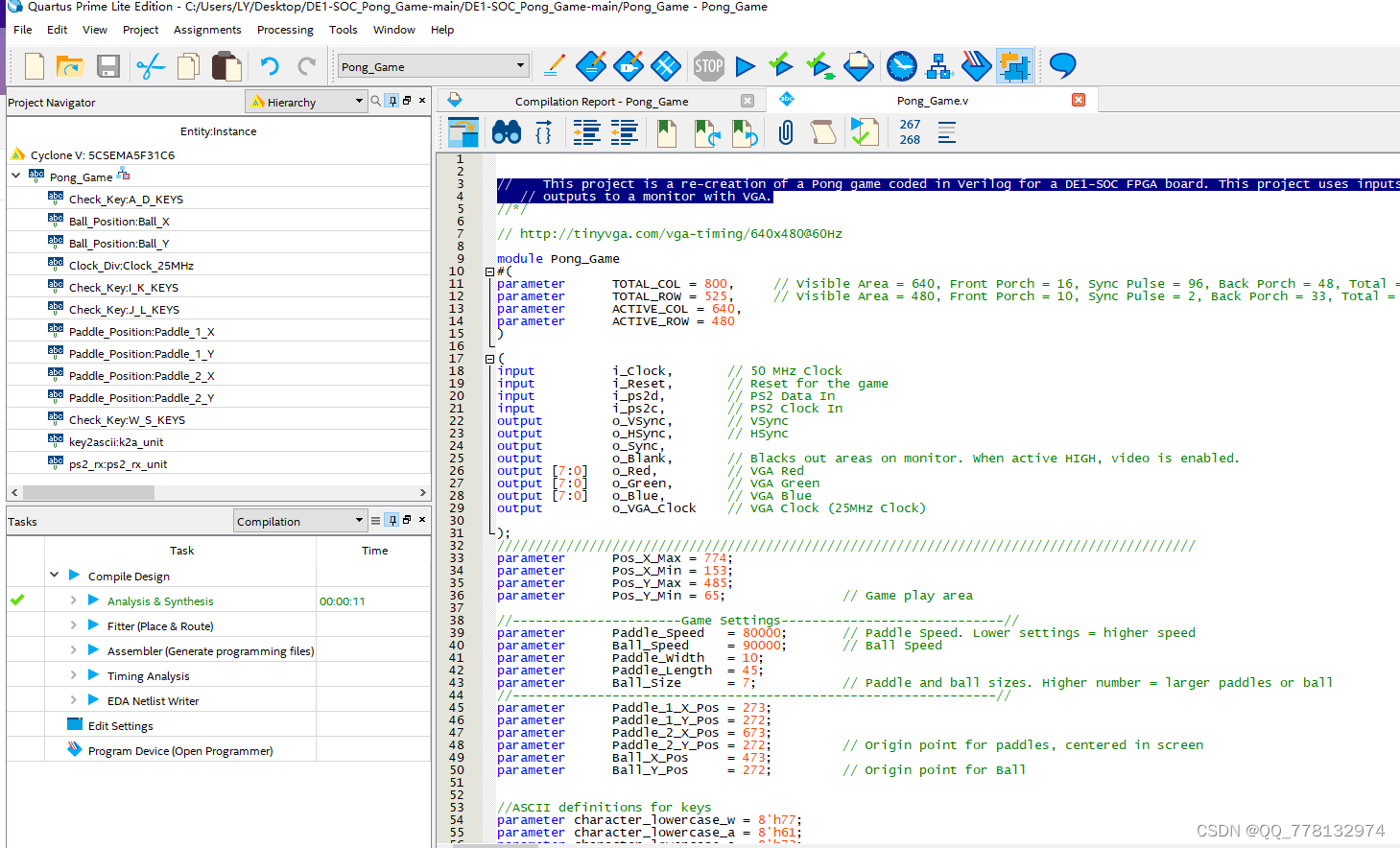

DE1开发板verilog实现简易乒乓球游戏(有上板照片验证)

开发平台:DE1开发板 软件平台:Quartus II 19.1 实现在乒乓球游戏设计,使用PS2键盘的输入和VGA显示器的输出,在显示器上可以看到两个板子控制小球的反弹。 使用PS2接口的键盘控制板子的运动方向; 通过640*480分辨率的VGA接口显示游戏画面。 下面是工程截图: 顶层代码如下: module Pong_Game#( parameter TOTAL_COL =