三速专题

FPGA——三速自适应以太网设计(2)GMII与RGMII接口

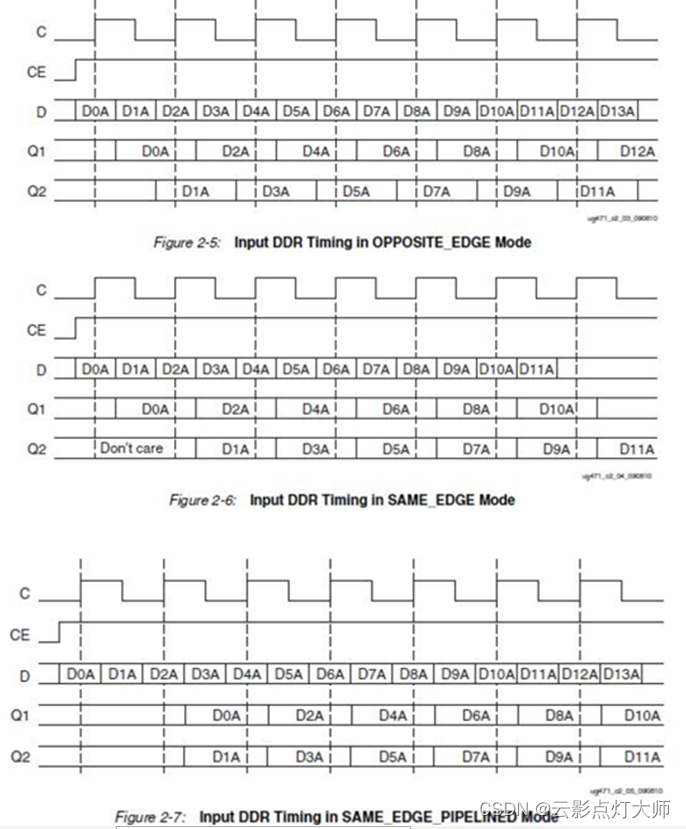

FPGA——以太网设计(2)GMII与RGMII 基础知识(1)GMII(2)RGMII(3)IDDR GMII设计转RGMII接口跨时钟传输模块 基础知识 (1)GMII GMII:发送端时钟由MAC端提供 下降沿变化数据,上升沿采集数据 (2)RGMII 时钟是双沿采样 RGMII:ETH_RXCTL线同时表示有效和错误,有效和错误位相异或得到。 时钟偏移,方便

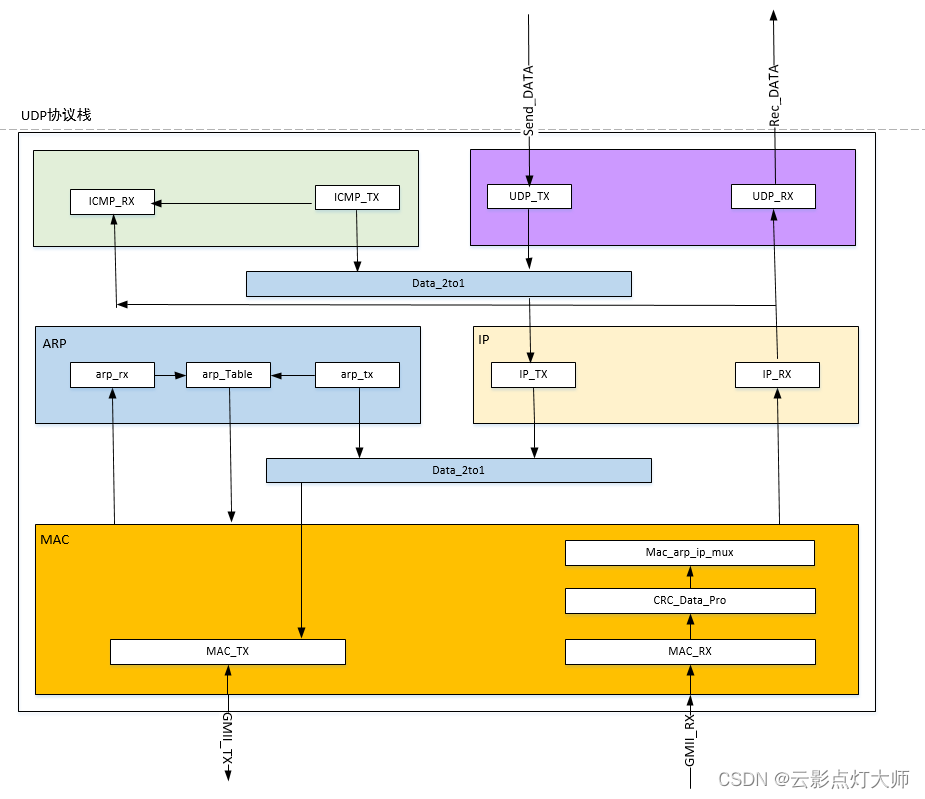

FPGA——三速自适应以太网设计(1)基本模块

FPGA——以太网设计(1)基本模块 1. 协议解析(1)MAC层(2)IP层 和 ARP层(3)UDP层 和 ICMP层 2.1 MAC接收模块2.2 MAC发送模块3.1 IP接收模块3.2 IP发送模块4.1 UDP接收模块4.2 UDP发送模块5.1 ICMP接收模块5.2 ICMP发送模块6.1 ARP接收模块6.2 ARP发送模块6.3 ARP表模块7 CRC数据对比模块8 MA