xinlinx专题

Xinlinx FPGA如何降低Block RAM的功耗

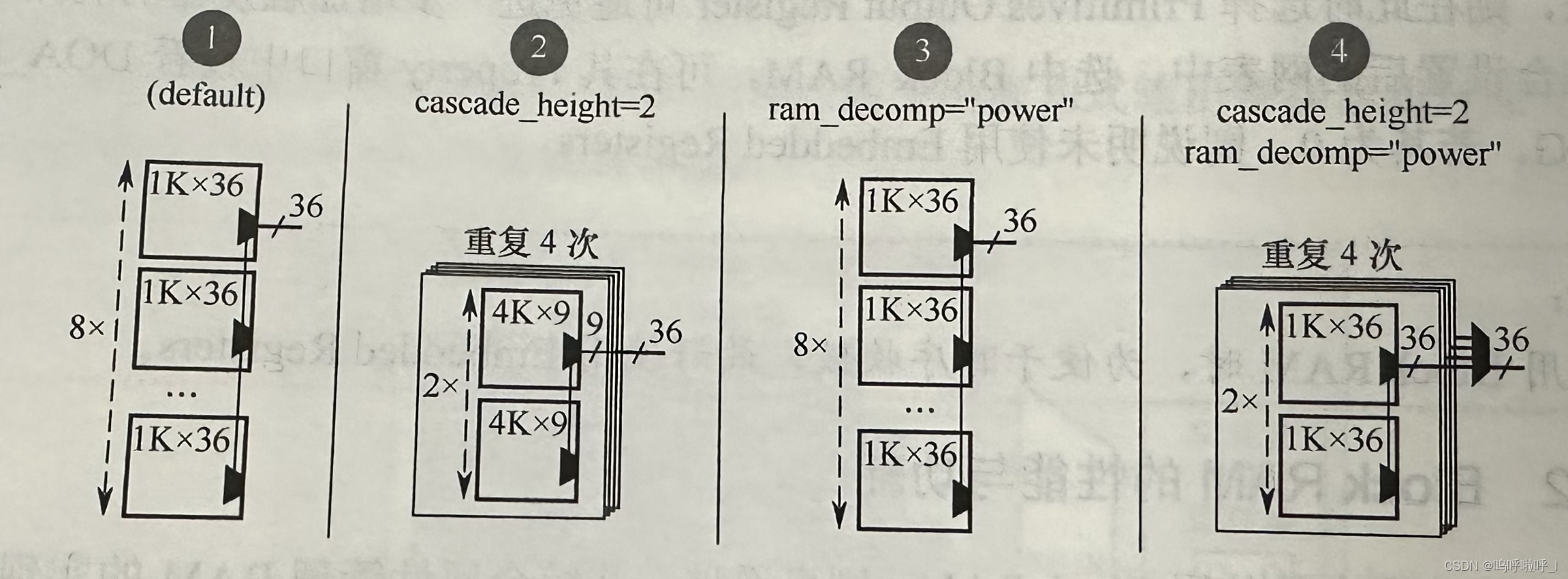

FPGA中降低Block RAM的功耗有两种方式,分别是选择合适的写操作模式以及Block RAM的实现算法及综合设置。我们知道对于采用IP核生成对应的RAM时,会有最小面积算法、低功耗算法以及固定原语,但是采用最小功耗算法有时由于级联长度导致无法实现,我们可以通过综合选项得到一个折中的效果,下面将具体介绍。 一、写操作模式 之前我们介绍过BRAM的各种设计细节,可以参考如下文章: Xinl

Xinlinx FPGA内的存储器BRAM全解

目录 一、总体概述1.7系列FPGA的BRAM特点2.资源情况 二、BRAM分类1.单端口RAM2.简单双端口RAM3.真双端口RAM 三、BRAM的读写1、Primitives Output Registers读操作注意事项2.三种写数据模式(1)Write_First(2)Read_First(3)No_change 3.读写冲突(1)读写时钟同步(2)读写时钟异步 四、三种BRAM实

创龙Xinlinx Artix-7系列FPGA采集卡的EEPROM、电源接口和拔码开关

TL-A7HSAD是一款由广州创龙基于Xilinx Artix-7系列FPGA自主研发的高速数据采集卡,可配套广州创龙TMS320C6655、TMS320C6657、TMS320C6678开发板使用。该采集卡包含1个双通道250MSPS*12Bit的高速高精度ADC及1路175MSPS*12bit高速高精度DAC,配备高性能的Xilinx Artix-7系列FPGA可进行高速数据转换和时序控制。

创龙Xinlinx Artix-7系列FPGA采集卡的按键、串口

TL-A7HSAD是一款由广州创龙基于Xilinx Artix-7系列FPGA自主研发的高速数据采集卡,可配套广州创龙TMS320C6655、TMS320C6657、TMS320C6678开发板使用。该采集卡包含1个双通道250MSPS*12Bit的高速高精度ADC及1路175MSPS*12bit高速高精度DAC,配备高性能的Xilinx Artix-7系列FPGA可进行高速数据转换和时序控制。

创龙Xinlinx Artix-7系列FPGA采集卡的拓展IO、SRIO接口

TL-A7HSAD是一款由广州创龙基于Xilinx Artix-7系列FPGA自主研发的高速数据采集卡,可配套广州创龙TMS320C6655、TMS320C6657、TMS320C6678开发板使用。该采集卡包含1个双通道250MSPS*12Bit的高速高精度ADC及1路175MSPS*12bit高速高精度DAC,配备高性能的Xilinx Artix-7系列FPGA可进行高速数据转换和时序控制。

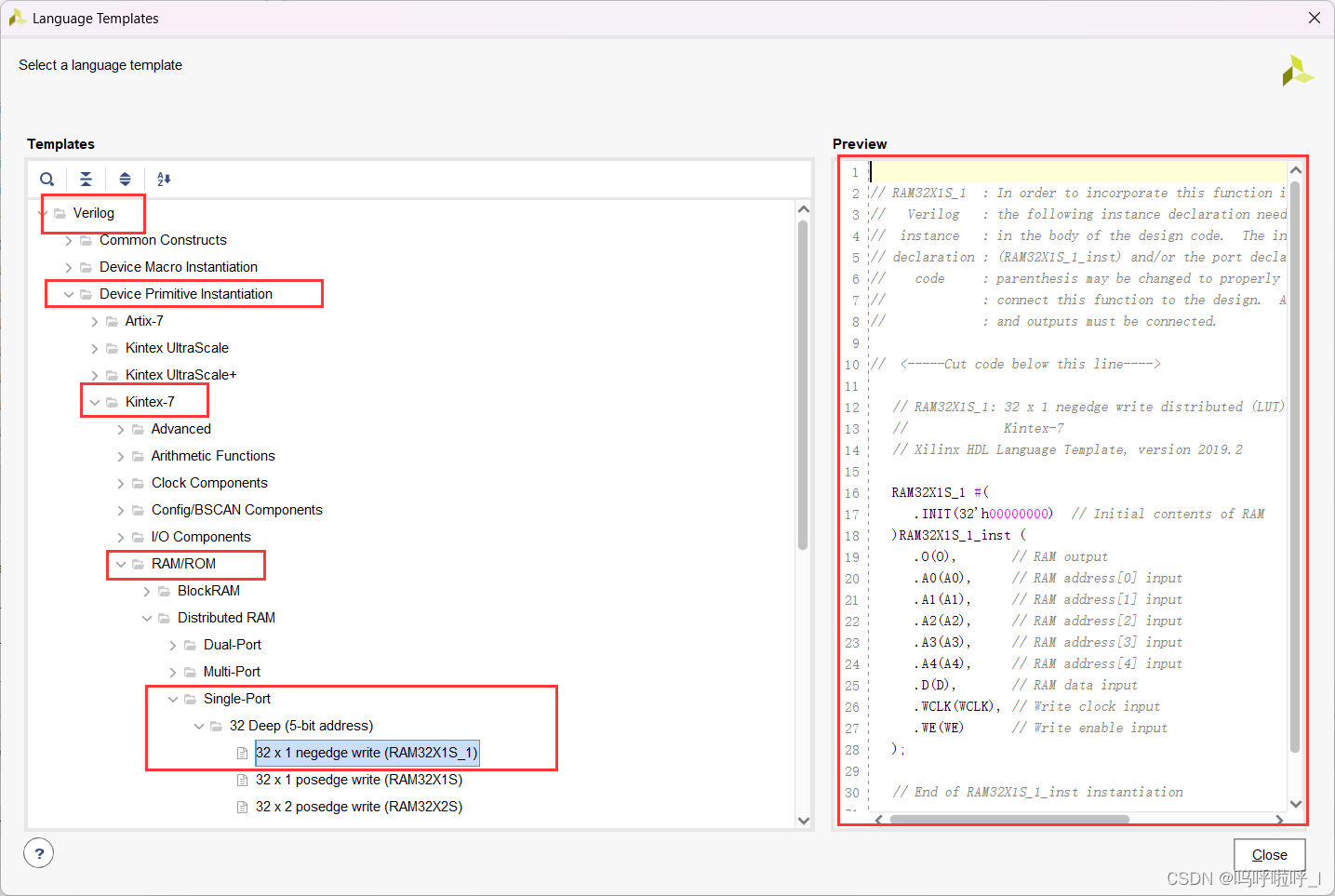

Xinlinx原语在哪查看如何使用/原语示例

1.打开Vivado 2.点击Tools,选择Language Templates 3.选择Language类型、Device Primitive Instantiation(原语)、Kintex-7(芯片系列),之后可以选择自己需要使用的类型,这里以分布式RAM为例,选中32×1的单端口分布式RAM后右侧就会给出例化的示例。

创龙Xinlinx Artix-7系列FPGA采集卡的PCIe接口、高速ADC接口

TL-A7HSAD是一款由广州创龙基于Xilinx Artix-7系列FPGA自主研发的高速数据采集卡,可配套广州创龙TMS320C6655、TMS320C6657、TMS320C6678开发板使用。该采集卡包含1个双通道250MSPS*12Bit的高速高精度ADC及1路175MSPS*12bit高速高精度DAC,配备高性能的Xilinx Artix-7系列FPGA可进行高速数据转换和时序控制。

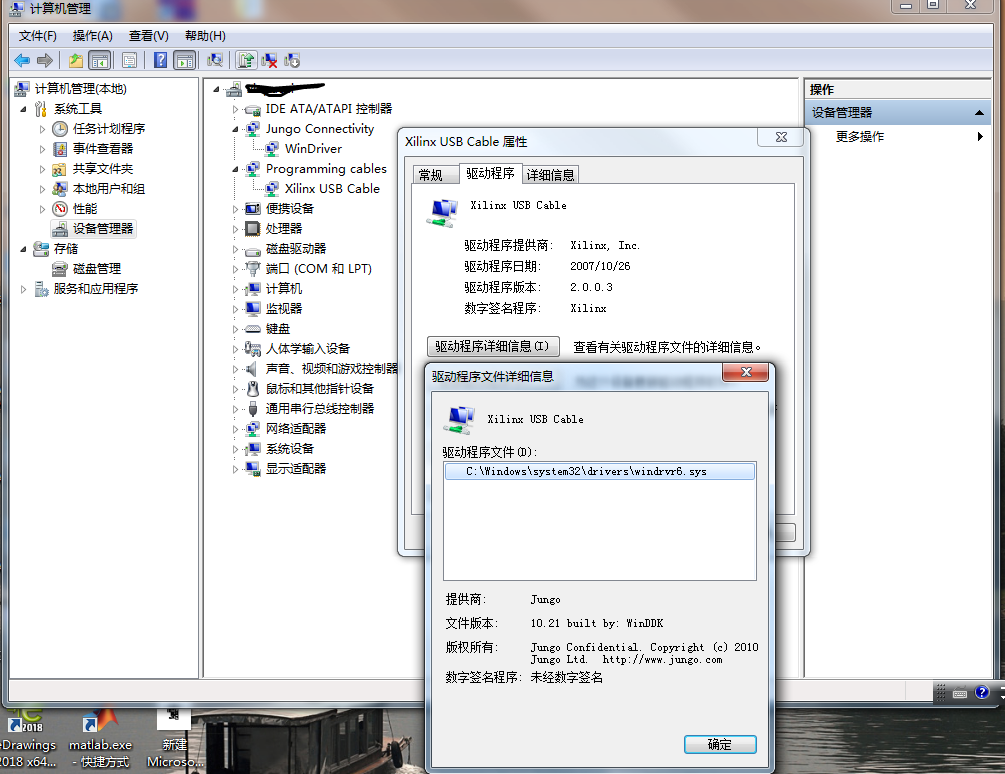

xinlinx impact出现错误can not find cable,check cable setup的解决方案

xinlinx impact出现错误can not find cable,check cable setup的解决方案 1、右键xilinx usb cable,驱动程序详细信息,找到路径C:\windows \system32\drivers\windrvr6.sys 2、删除此路径下的该文件C:\windows \system32\drivers\windrvr6.sys