vivado2021.1专题

ZynqMP Vivado2021.1 bit文件格式解析

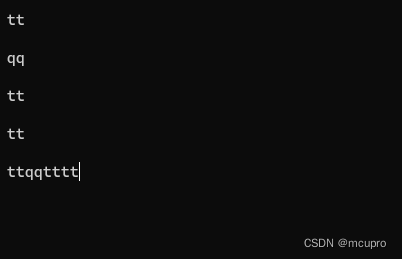

前言: 在裸机下运行的需手动加载不同的代码到PL执行。 PS的xilfpga库支持Vivado生成的bit和bin文件及bootgen生成的boot.bin到PL上运行。 Vivado的bit文件是在bin文件头部多了一些描述信息,头部信息长度不固定。 描述信息可以使用file命令查看 其中我个人最关心的是data length,这个数据长度表示bin文件的长度。 1、准备:

ZynqMP Vivado2021.1 PL 点亮LED

前言: 文章目标:用PL的IO点亮一个LED灯。 硬件环境:Xilinx ZynqMP XCZU4EV-SFVC784-1-I 硬件引脚:LED - AE15, Key- AE14, 200MHz晶振 - AE5 软件环境:Ubuntu20.04LTS + Vivado2021.1 + Vitis2021.1 新建Vivado工程: 1、打开Vivado2021.1,创建一个工程,

15EG使用vivado2021.1实现LWIP的网络传输

创建工程模板在hello_world中已经介绍过了,这里直接从配置完zynq ip核开始,由于使用vivado的版本不同,配置ZYNQ时需要用到的tcl文件我会放在工程文件夹下的file文件夹中 配置好IP核后,右键设计模块,点击Generate Output ... 右键设计模块生成HDL文件,本工程不会使用到bit文件所以不用生成bit文件,接下来是创建vitis工程。由于使用