srio专题

C66xx SRIO DoorBell的使用

关于SRIO DoorBell中断的路径 Keystone DSP的SRIO模块共有24个system Interrupt,即INTDST0~23。其中INDTST0~15为通用的system Interrupt,可以连接到LSU或者DoorBell中断,再输入到CIC0,而INTDST16~23只连接DoorBell中断,属于system Event,直接输入到CorePac。 KeySto

关于xilinx srio ip复位问题

关于xilinx srio ip复位问题 语言 :Verilg HDL 、VHDL EDA工具: Vivado 关于xilinx srio ip复位问题一、引言二、FPGA 之间 srio通信复位处理复位时序不同步:SRIO 模块未正确初始化:等待复位完成的时间不足:SRIO 配置不匹配: 三、FPGA与DSP之间srio通信复位处理四、FPGA与PPC之间srio通信复位处理

创龙Xinlinx Artix-7系列FPGA采集卡的拓展IO、SRIO接口

TL-A7HSAD是一款由广州创龙基于Xilinx Artix-7系列FPGA自主研发的高速数据采集卡,可配套广州创龙TMS320C6655、TMS320C6657、TMS320C6678开发板使用。该采集卡包含1个双通道250MSPS*12Bit的高速高精度ADC及1路175MSPS*12bit高速高精度DAC,配备高性能的Xilinx Artix-7系列FPGA可进行高速数据转换和时序控制。

创龙TI KeyStone C66x多核定点/浮点DSP TMS320C665x 的底板B2B连接器、SRIO接口

广州创龙结合TI KeyStone系列多核架构TMS320C665x及Xilinx Artix-7系列FPGA设计的TL665xF-EasyEVM开发板是一款DSP+FPGA高速大数据采集处理平台,其底板采用沉金无铅工艺的6层板设计,适用于高端图像处理、软件无线电、雷达声纳、高端数控系统、机器视觉等高速数据处理领域。核心板在内部通过uPP、EMIF16、SRIO通信接口将DSP与FPGA结合在一起

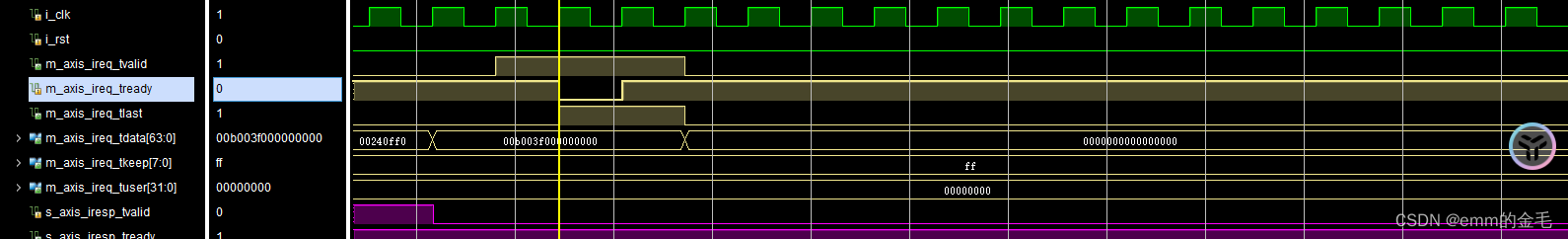

SRIO系列-仿真测试

一、前言 前两篇已经讲述了SRIO协议的概况,以及xilinx SRIO IP核的使用方式,已经在搭建工程的过程中时钟和复位的注意事项。 二、设计框图 整个框图也是按照之前的工程进行搭建,首先时SRIO_Channel,由SRIO IP核和时钟、复位模块组成,这是在之前的工程搭建中一种采用的一种Channel结构。其次,SRIO Module是按照QPLL共享的方式去管理Channel,

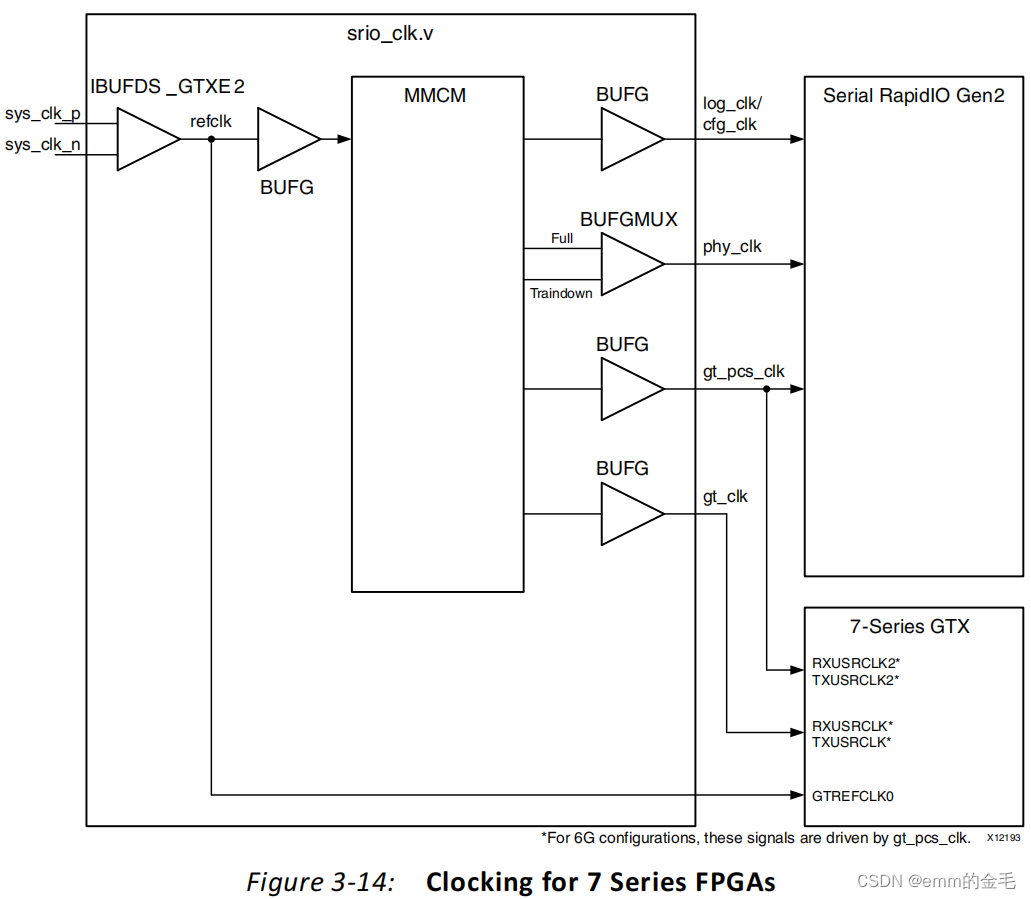

SRIO系列-时钟逻辑与复位逻辑

一、前言 上一篇讲述了SRIO协议的基本概念,传输的HELLO帧格式、事务类型等,本篇说一下SRIO IP核的时钟关系。 基本的IP设置可以参考此篇文章:【高速接口-RapidIO】Xilinx SRIO IP 核详解-CSDN博客 二、时钟关系 PHY可以在两个时钟域上运行: phy_clk,这是主核心时钟,和gt_pcs_clk,这是用于串行收发器接口。gt_clk不由PHY使用,但

SRIO--IP讲解及环回测试

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录 前言一、IP例化文件二、SRIO环回工程搭建三、板级验证3.1 本实验的板级验证环节,主要验证以下几个目标:3.2 系统所需硬件3.3 ILA波形 前言 本章将为大家介绍 “Serial RapidIO Gen2 ”IP 的使用以及配置方法。“Serial RapidIO Gen2 ”IP

SRIO—IP讲解及说明

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录 前言一、SRIO IP 概述1.1 逻辑层1.1.1 I/O 端口(I/O Port)1.1.2 消息端口(Messaing Port)1.1.3 用户自定义端口(User-Defined Port)1.1.4 维护端口(Maintenance Port) 1.2 缓冲层1.3 物理层 二、协议格式2.1 传

Tsi721 SRIO退出程序再启动问题解决办法

1、背景介绍 项目中使用Tsi721连接加速模块进行RapidIO收发数通信。在调试过程中,用户会手动结束任务,当再次启动任务时会报以下异常信息, 此时就无法再收到加速模块发来的数据。在这种情况下,必须要重启模块才能收到数据。 2、原因分析 用户在收数时使用的是封装的接口函数库,收数流程如下: 在收数过程中会创建门铃接收任务,等待门铃中断,当用户收到退出程序

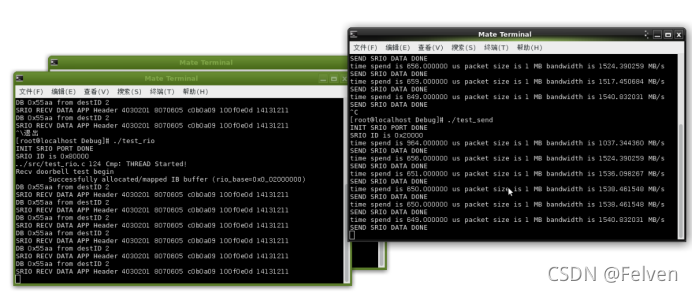

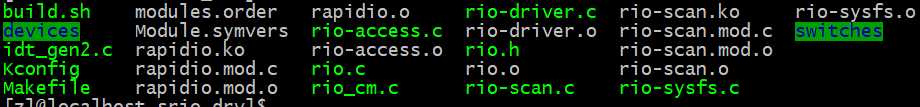

tsi721板卡和FPGA之间SRIO通信

1.安装基本依赖包 使用sudo yum install 命令安装make git vim, kernel-devel, elfutils-libelf-devel. 2.从git下载相关rapidio驱动和测试代码包: git clone https://github.com/RapidIO/kernel-rapidio.git 将得到的kernel-rapidio文件夹拷贝到工作目

CPS1848国产替代芯片 国产SRIO交换芯片

原位替换CPS1848芯片的,在功能参数性能与CPS1848相同,寄存器一致,满足条件要求的情况下可以实现替换兼容 塑封 工业档-40℃~+85℃ 满足工业档 塑封 宽温-55℃~+125℃ 满足GJB-N1级 陶封 宽温-55℃~+125℃ 满足GJB-B级 典型功耗13.7W。 (VDD=VDDS=VDDA=CDDT=1.2V,VDD3=VDD3A=3.3V,18个端口配置成8个4X

计算机板卡设计仿真,PCI-Express X4总线的SRIO接口板卡

基于PCI-Express X4总线的SRIO接口板卡 产品概述 本板卡为PCI-Express x4转两路Serial RapidIO x4标准接口的板卡。本板卡对外接口为两路SRIO(Serial RapidIO)接口,两路SRIO接口分别由IDT的TSI721接口芯片和Kintex7 FPGA控制,同时板载Tsi-574标准SRIO Switch交换芯片,可实现SRIO交换机功能。本板卡可

zynq srio枚举id方案设计

常见的SRIO枚举分配ID操作在Powerc平台比较常见,本文使用zynq7045实现SRIO枚举功能,PL端有SRIO IP,只需要将AXI维护端口挂到AXI-GP接口上,PS软件就可以通过AXI总线访问SRIO IP实现枚举自动分配ID功能。本次测试硬件拓扑图如下图所示。 srio交换芯片采用的时1848交换芯片,SRIO1和SRIO2本次实验