reg专题

SRL_STAGES_TO_REG_INPUT

寄存器级可以通过SLR输入拉出,也可以使用 SRL_STAGES_TO_REG_INPUT属性。 这提供了对流水线寄存器结构的控制,以在流水线下和流水线上寻址 SRL基元的输入侧。 架构支持 所有架构。 适用对象 •单元格(get_cell)作为叶级SRL实例。 价值观 •1:Vivado逻辑优化将从指定的SRL中提取寄存器 原始输入。 •-1:Vivado逻辑优化将把寄存器推入指定的SRL基元中

【无标题】verlog中wire 和reg用法

wire(组合逻辑) wire用来连接模块实例化的输入和输出端口; wire用作实际模块声明中输入和输出; wire 元素必须由某些东西驱动,并且在没有被驱动的情况下,无法存储值; wire 元素不能用在 always模块中 = 或者 <= 的左边; wire元素是assign语句左侧 唯一的合法类型; wire 元素是在基于Verilog的设计中连接两片的无状态方式; wire 只能用在 组合

Verilog中端口应该设置为wire形还是reg形

初学Verilog时,一直搞不清Verilog描述模块时端口应该取什么类型;是reg形?还是wire形?模块对应测试文件的端口类型为什么又与模块的端口类型不一样?因此有必要进行学习与整理: 先写结论: verilog中的端口具有三种传输方向:input、output、和inout,所有的端口均默认为wire类型; 模块描述时,input端口只能为线网形,output端口可以为线网/reg,in

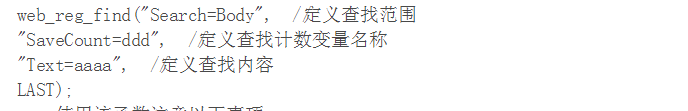

Loadrunner:性能测试浅析关联函数web_reg_save_param()

背景:关联是性能测试中必不可少的技术点,即为了模拟真实场景而设计的,同样关联的接口测试亦是如此;首先介绍loadrunner工具的几个相关函数:大抵函数的参数部分,除了Ordinal不写就是默认Ordinal=1(取出第一个匹配的参数),写了Ordinal=All即为保存响应满足左右边界的所有参数,那此时{param_1}就不是一个正确的参数引用,而就是{param_1}字符串,下面来以web_r

altera 防止reg/wire 优化

转载:# 关于SignalTap中的节点查找不到的问题_signaltap找不到信号-CSDN博客 关于SignalTap中的节点查找不到的问题 在选择需要查看的信号节点时,有一个信号节点,我翻遍了所有的模块,始终未能看到它的影子,然后上网查了一下,找到了问题所在。 因为在使用quartus编译综合时,某些信号会被优化掉,就会导致在查找此信号节点时,会发现找不见。 解决方法: 1.对

终于搞懂Linux 设备树中的#address-cells,#size-cells 和reg 属性

目录 一、前置知识 1. 处理器平台2. reg 属性的基本格式3. reg 属性的作用 reg 用法 二、#address-cells 和 #size-cells 属性 1. 示例1 2. 示例23. 示例3 一、前置知识 要理解#address-cells和#size-cell 这两个属性,就要先了解 reg属性。 1. 处理器平台 下面的介绍,主要基于 IMX6ULL进行 2

LR的web_reg_save_param详解

运行脚本时,web_reg_save_param 函数将扫描所访问的后续 HTML 页。如果指 定左边界和/ 或右边界, VuGen 将搜索这些边界之间的文本。VuGen 找到文本 后,会将其分配给某个参数。 函数的语法如下所示: 下表列出可用的属性。注意,属性值字符串(例如 Search=all)不区分大小写。 NotFound 找不到边界并且生成了空字符串时的处理方法。默认值

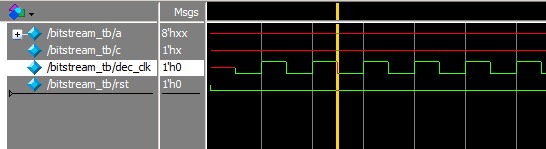

INVS 对时钟二分频器(reg-clkgen)的理解和处理

在时钟树的设计中,有很多方式处理分频时钟,常见的无外乎两种模式: 时钟二分频器(reg-clkgen)门控时钟 二者在功能上略有不同,比较的大差异是前者可以简单的实现50%占空比,后者却对功耗友好同时降低了实现难度。这里结合INVS在CTS的手法,一起了解一下INVS对二者的处理差异。闲言少叙,ICer GO! 就后端工具而言,CTS是其三大引擎之一,在当下设计的高工艺、高性能的背景下,

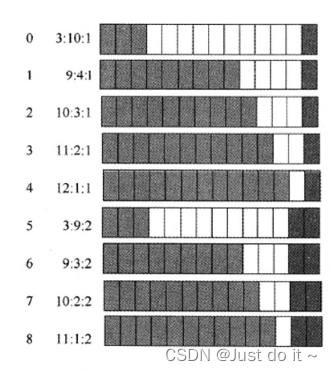

5G NR - PDCCH学习笔记3 - CORESET之CCE-REG mapping

CCE是PDCCH的逻辑资源,需要映射到CORESET的物理资源才能传输。 CCE-REG映射分两种方式:Interleaved mapping和 Non-Interleaved mapping. 每个CORESET配置一种CCE-REG mapping方式。 对于Interleaved mapping, CCE所映射的REGs以REG bundle为单位离散的分布在频域上,如下图所示

【verilog 设计】 reg有没有必要全部赋初值?

一、前言 在知乎发现“reg有没有必要全部赋初值”这个问题,与自己近期对Verilog reg的进一步学习相契合,此文对这个问题进行总结。 二、reg的初值赋值方式 就语法意义赋初值而言,就是在声明reg时对其赋值。在工程中,对于数字系统的初始化一般是在上电后使用全局复位变量来实现的,也即利用复位信号来赋初值。 三、reg是否有必要全部赋初值 由于verilog不仅用于ASIC,还用于F

FL Studio v21.2.3.4004 中文永久版网盘下载(含Key.reg注册表补丁)

软件介绍 FL Studio21水果编曲软件汉化版是一款专业的音乐制作软件,被广泛地应用于电子音乐、hip-hop、流行乐等多种音乐类型的制作。该软件提供了丰富的音频编曲工具和音乐效果器,让用户可以轻松地创作出高品质的音乐作品。同时,这也是一款非常易于上手的软件,即使是对音乐制作不熟悉的用户也可以通过该软件来创作出自己的音乐作品。 FL Studio21水果编曲软件汉化版提供了多种音频工具,包

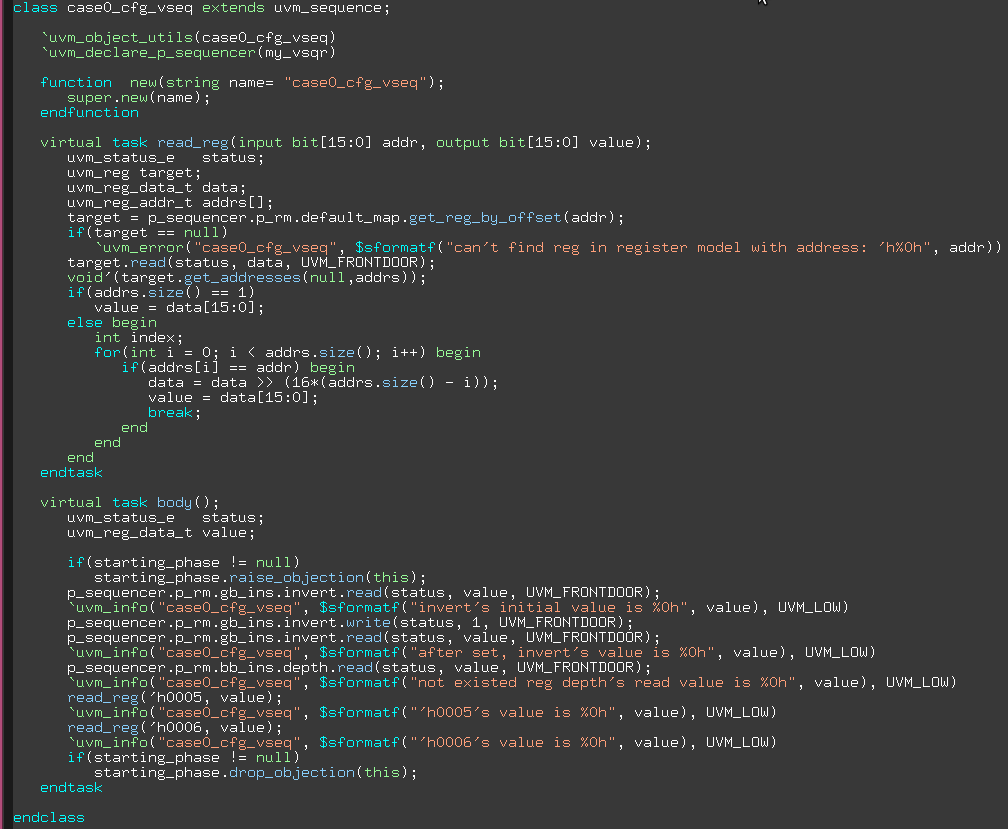

UVM:7.8.2 get_reg_by_offset 函数

1.建立寄存器模型后,可以直接通过层次引用访问寄存器: 2.还可以使用get_reg_by_offset 函数通过寄存器地址得到uvm_reg 指针,在调用此uvm_reg的read 或者write 进行读写操作: 1)如果像7.4.1 使用了寄寄存器模型,从最顶层的reg_block 的 get_reg_by_offset 也可以得到子reg_block 的寄存器。 2)假如b

变量(reg)未初始化的笔记

变量(reg)在全局reset时未初始化, 工作之后终于知道有专门一个名词叫作x propagation 仿真和实际上板跑有一个区别是仿真时未初始化的变量在波形里是红色的x,实际上板跑的时候是不会有这种信号。导致上板结果和仿真不一致。 在实际调试时发现未初始化的变量在全局reset时并不一定是低电平的0,原因是程序中很多代码不依赖reset就已经开始跑了, 最简单的例子 always

Data truncation: Incorrect string value: '\xE5\xB9\xB43\xE6\x9C...' for column 'reg_time' at row 1

Caused by: com.mysql.cj.jdbc.exceptions.MysqlDataTruncation: Data truncation: Incorrect string value: ‘\xE5\xB9\xB43\xE6\x9C…’ for column ‘reg_time’ at row 1 at com.mysql.cj.jdbc.exceptions.SQLExcepti

导入*.reg文件,手动增删注册表项(UE32绿色版)

导入*.reg文件,手动增删注册表项,下载到一个UltraEdit-32免安装的绿色版,想把它加到windows右键菜单中: 1、添加: REGEDIT4 [HKEY_LOCAL_MACHINE/SOFTWARE/Classes/*/shellex/ContextMenuHandlers/UltraEdit-32] @="{b5eedee0-c06e-11cf-8c56-4445535400

CVE-2021-31440:eBPF verifier __reg_combine_64_into_32 边界更新错误

文章目录 前言漏洞分析构造 vuln reg 漏洞利用漏洞修复参考 前言 影响版本:Linux 5.7 ~ 5.11.20 8.8 编译选项:CONFIG_BPF_SYSCALL,config 所有带 BPF 字样的编译选项。General setup —> Choose SLAB allocator (SLUB (Unqueued Allocator)) —> SLAB。CON

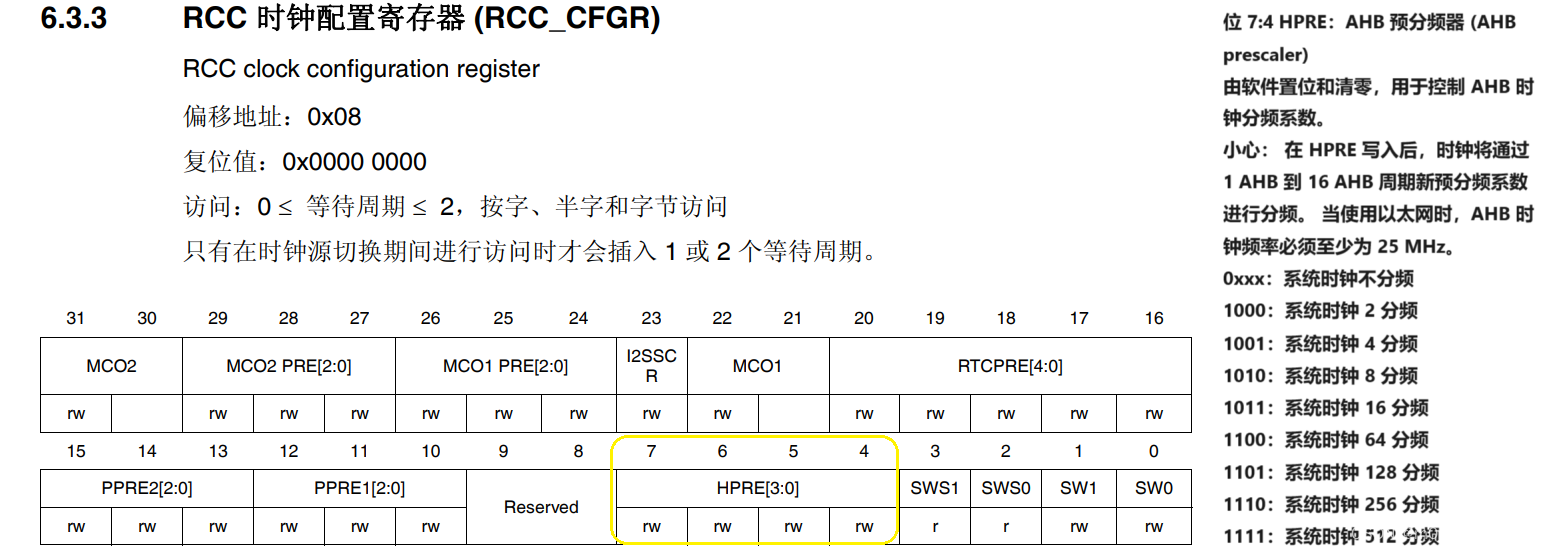

#define MODIFY_REG(REG, CLEARMASK, SETMASK)

#define MODIFY_REG(REG, CLEARMASK, SETMASK) WRITE_REG((REG), (((READ_REG(REG)) & (~(CLEARMASK))) | (SETMASK))) 这个宏 MODIFY_REG 是在嵌入式编程中,它用于修改一个寄存器的特定位,而不影响其他位。这个宏接受三个参数: REG:要修改的寄存器的地址

reg.exe操作注册表

reg add HKEY_LOCAL_MACHINE\SOFTWARE\Microsoft\Windows\CurrentVersion\Run /v testvalue /t REG_SZ /d "testdata "/f

verilog reg 初值问题

虽然没有写初值 但是硬件电路肯定有逻辑电平的如果是用fpga实现的 缺省值为全0 也可以在信号声明时指定初始值如果是asic实现 初始值是随机的(但也是某个电平) 声明时指定初值会被忽略rtl仿真时不给定初始值 自然一直是x不定态 追问 你这说用fpga实现是什么意思,我是用quartus烧写去alter fpga芯片上,不过缺省的不是0。 追答 不是0也是可能的比如你写alw

Exchange.server续订证书时REG文件乱码问题解决

在Exchange的管理员界面中申请续订证书时,REG文件会出现乱码。 这个问题可通过以下办法解决 Step1. 首先新见一个文件夹,将申请好的REG文件和脚本程序convert.ps1都放进去 Step2. 然后打开Exchange的POWERSHELL命令提示符 Step3. 将路径切换到那个新建的文件夹下 Step4.

关于Web_reg_save_param的一个BUG说明

土匪太懒了,于是我又有机会出来说点东西了,情况是这样的。 在土匪某一次上课中遇到一个奇怪的问题,通过关联函数web_reg_save_param关联内容,当使用ord=all时可以看到匹配的内容有2条记录,但是当修改ord=2时,脚本关联提示没有匹配的记录条数,然后这个问题就让人崩溃了,完全不符合以前的理解概念啊。于是在土匪孜孜不倦、春风吹战鼓擂、天热不怕光脚等等下,终于找到了问题之所在。

Elastic-job报错:com.dangdang.ddframe.job.reg.exception.RegException...KeeperErrorCode=OperationTimeout

zookeeper作为注册中心 1.配置如下: <?xml version="1.0" encoding="UTF-8"?><beans xmlns="http://www.springframework.org/schema/beans"xmlns:xsi="http://www.w3.org/2001/XMLSchema-instance" xmlns:reg="http://www

Verilog 之 wire与reg 类型的变量

文章目录 `reg` 类型`wire` 类型总结默认情况下的input ,output 变量 在 Verilog 中,reg 和 wire 是用来声明变量或信号的关键字,它们有不同的特征和用途。 reg 类型 reg 类型用于表示寄存器变量。在 Verilog 中,reg 用于存储状态或时序逻辑,通常在 always 块或时钟触发的过程中使用。它可以存储值并在时钟信号触

【LTE】LTE 基础之RB和RE、REG、CCE的定义

文章目录 前言1. LTE 相关名词定义2. RB与占用带宽计算3. LTE TDD时隙配比方案介绍总结 前言 本文参考3GPP 36.141/36.211, 部分描述及截图来源于baidu等网络,如有侵权请联系删除。 1. LTE 相关名词定义 RB(Resource Block): 频率上连续12个子载波,时域上一个slot(7 symbol / 0.5ms),