pci专题

如何编写Linux PCI设备驱动器 之一

如何编写Linux PCI设备驱动器 之一 PCI寻址PCI驱动器使用的APIpci_register_driver()pci_driver结构pci_device_id结构 如何查找PCI设备存取PCI配置空间读配置空间APIs写配置空间APIswhere的常量值共用部分类型0类型1 PCI总线通过使用比ISA更高的时钟速率来实现更好的性能;它是时钟运行在 25 或 33 M

PCI Express 体系结构导读摘录(二)

系列文章目录 PCI Express 体系结构导读摘录(一) PCI Express 体系结构导读摘录(二) 文章目录 系列文章目录第Ⅱ篇 PCI Express 体系结构概述第 4 章 PCIe 总线概述4. 1 PCIe 总线的基础知识4. 1. 1 端到端的数据传递4. 1. 2 PCIe 总线使用的信号4. 1. 3 PCIe 总线的层次结构4. 1. 4

13. PCI PIN

PIN是啥? PIN就是我们刷卡时,输入的密码。银联卡基本都有,海外也开始慢慢普及,尤其是mastercard已经在一些国家和地区强制执行,新POS机如果不支持Online PIN已经不允许出新机器了。所以PIN显得格外重要。 PIN的重要性 上篇文章已经讲过,PIN是最敏感数据里面的一种,其实PIN是最敏感里面的最敏感,因为谁也不想自己的取款密码被泄露出去。带PIN的交易,发卡行一般都

12. PCI DSS

支付行业,如果明文的卡信息通过了你的后台,那后台必须有PCI DSS的安全认证。这个认证是做支付系统的敲门砖,如果没有这个证书,基本到哪里都行不通。具体的认证过程和项目可以查看PCI 官网介绍。本篇着重在技术层面讲解需要满足的要求。 敏感数据 卡片交易时,敏感数据分2类,一类是可存储的数据,一类是不可存储的 可存储数据 卡号(PAN)有效期 卡号需要加密存储,有效期可以明文存储 不可存

《PCI Express体系结构导读》随记 —— 第II篇 第7章 PCIe总线的数据链路层与物理层(7)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第II篇 第7章 PCIe总线的数据链路层与物理层(6) 7.1 数据链路层的组成结构 7.1.1 数据链路层的状态 3. DL_Active状态 当数据链路层处于DL_Active状态时,PCIe链路可以正常工作。此时数据链路层可以从事务层和物理层正常接收和发送TLP、并处理DLLP,此时数据链路

PCI Device Class Codes

目录 Class Code 0: Pre 2.0 Class Code 1: Mass Storage Controllers Class Code 2: Network Controllers Class Code 3: Display Controllers Class Code 4: Multimedia Devices Class Code 5: Memory Co

Linux源码阅读——PCI总线驱动代码(二)配置空间访问设置

目录 1.什么是配置空间 2.对配置空间的访问 3.PCI驱动中对配置空间的访问的实现 3.1 pci_direct_probe 3.2 pci_mmcfg_early_init 3.3 pci_direct_init 3.4 上述函数总结 3.5 pci_mmcfg_late_init 4.总结 1.什么是配置空间 PCI设备有三个相互独立的物理空间

驱动开发系列17 - PCI总线

一:概述 PCI(外设计算机互连)或PCIe总线是现代计算机的主要组成部分,了解它的工作原理对于理解许多Linux设备驱动程序非常重要。 关于PCI总线本身有很多好的信息(在维基百科和其他地方),而Linux内核中也有关于PCI处理子系统实际实现的文档。然而,这两种现有来源之间存在一个空白,本文希望填补这个空白。 虽然我在这里的重点是理解x86环境

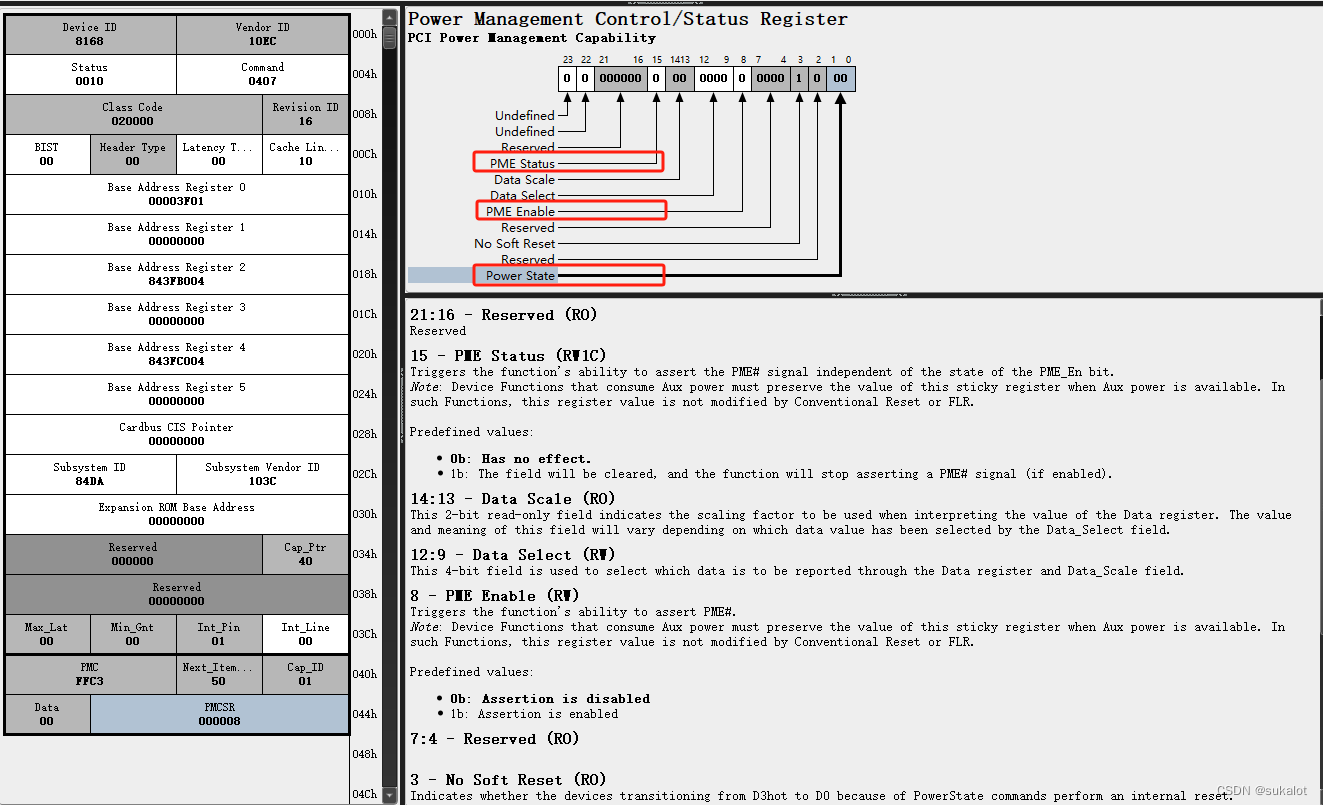

第三十一篇:!pci of WinDbg

刚刚在看WinDbg在硬件调试方面有哪些扩展命令的时候,让我回想起一个工作中的实际事务。 在xHCI USB3.0/3.1 IP项目开发过程中,需要得到类似实际产品的PCIe配置空间信息,以作对比参考。 当时的做法是,将类似产品的xHCI host controller通过PCIe口接到SoC系统中, 通过编写ARM SoC的Bare metal代码来读取每一个产口的PCIe配置空间。

第二十七篇:Windows驱动中的PCI, DMA, ISR, DPC, ScatterGater, MapRegsiter, CommonBuffer, ConfigSpace

最近有些人问我PCI设备驱动的问题, 和他们交流过后, 我建议他们先看一看<<The Windows NT Device Driver Book>>这本书, 个人感觉, 这本书写得非常连贯流畅. PCI设备驱动基本包括了PCI的资源获取, 配置空间的读写, 中断的处理, 中断后半部在DPC中的处理. 同时, 也必须了解DMA, ScatterGater, MapRegister, Com

QEMU/KVM 虚拟机显卡透传 (vfio-pci)

首发日期 2024-08-22, 以下为原文内容: 本文介绍将 PCIE 设备 (显卡) 透传给 QEMU/KVM 虚拟机的一种方法, 基于 Linux 内核的 vfio-pci 功能. 透传 (pass through) 之后, 虚拟机内可以直接操作 (使用) 显卡硬件, 就像物理机那样, 几乎没有虚拟化的性能损失. 这里是 穷人小水滴, 专注于 穷人友好型 低成本技术. 相关文章

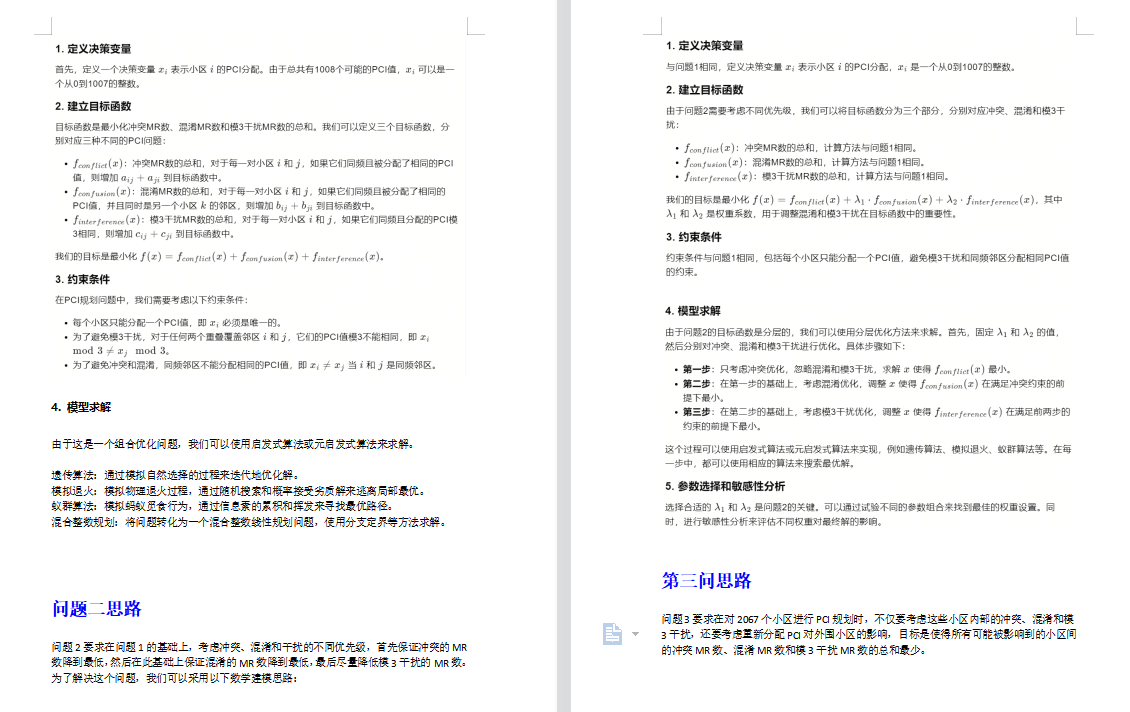

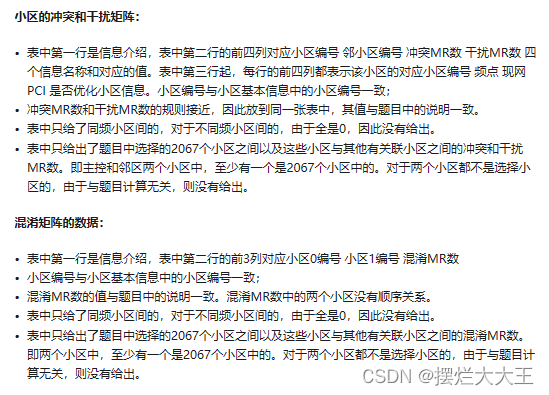

2024MathorCup A题 赛后思路代码分享(分赛区一等奖)移动通信网络中 PCI 规划问题

今年突然变成分赛区 (10%) 推国,国奖结果还没出,感觉一等(2%)有点悬,论文写的太一般了我没时间去修。 碎碎念:4 月又被拉着不务正业打了次比赛,刚好这几天有闲暇,传一下之前写的解题思路,不过时间太久了,就不重新花时间整理完整代码了,只分享核心代码。这题的解题难点不在代码部分,理清思路使用简单的启发式算法应该就可以获得靠前的奖项。 以下部分是我写给队友的思路的修改版本,在看的时候可以将自己

支付卡产业最新发布PCI DSS v4.0.1

自2022年3月PCI DSS v4.0发布以来,受到全球支付产业高度关注,为了解决来自所有产业相关者的反馈和问题,PCI安全标准委员会(PCI SSC)发布了该标准的修订版PCI DSS v4.0.1。其中包括对格式和印刷错误的更正,也澄清了一些要求和指南的重点和意图。本修订版中没有附加或删除的要求内容。 为了确保变更、澄清和额外的指导能够有效地支持产业采用PCI DSS v4,PCI S

DIO控制卡,IRIG-B码卡,PCI-E总线接口卡,百兆数据采集卡

DIO控制卡 ● 4路继电器输出(5A@250VAC) ● 4路开关量输入(24VDC) ● 1路IDE接口 ● 端口浪涌保护 IRIG-B码卡 ● 1路IRIG-B对时接口(RS485/光纤) ● 1路IEEE1588 V2对时接口(RJ45/光纤) ● PTP模式对时精度:±100nS ● ETE模式对时精度:±250nS ● IRIG-B对时精度:±250nS ● 自守时精度最高±50

BIOS实战之PCI设备枚举二

上次说到了除了IO枚举PCI设备,还有另一种方式枚举PCI设备,那就是通过pciio,这也是UEFI代码中的常规操作(当然还有MMIO,不过不写了) UEFI BIOS 提供了两个主要的模块来支持PCI 总线,一个是PCI Host Bridge 控制器驱动,另一个是PCI 总线驱动。 PCI Host Bridge 控制器驱动是跟特定的平台硬件绑定的,根据系统实际IO 空间和memory m

lspci 显示当前设备的PCI总线信息

lspci 显示当前设备的PCI总线信息 lspci 显示当前设备的PCI总线信息显示当前主机的所有PCI总线信息:以数字方式显示PCI厂商和设备代码同时显示数字方式还有设备代码信息以树状结构显示PCI设备的层次关系:更多信息 lspci 显示当前设备的PCI总线信息 lspci命令用于显示PCI总线的信息,以及所有已连接的PCI设备信息。 官方定义为: lspci -

windows驱动开发-PCI讨论(一)

前面描述中断的时候,我们曾经多次体积PCI,甚至提供了一些PCI的相关知识,但是整个PCI是一个很大的体系,专门记录这个体系超出了这个系列的范畴,有兴趣的可以到PCI官网了解详细的情况。 但是还是会花费一些时间讨论PCI技术,接下来我们从WDM的角度讨论PCI协议。 先正式的介绍一下PCIe: PCI Express (PCIe) 是一种 I/O 总线技术,旨在 PCI、PCI-X 和加速图形

windows驱动开发-PCI和中断(三)

在前面我们用一个实际的案例来说明了INTx中断是如何编程的,但是现在几乎已经很少遇到INTx中断了,基本上都是MSI和MSIX中断。 MSI和MSIX PCI 2.2 规范中引入了 (MSI) 的消息信号中断,作为基于线路的中断的替代方法。 使用 MSI 的设备通过将值写入特定内存地址来触发中断,而不是使用专用引脚触发中断。 PCI 3.0 定义了一种扩展形式的 MSI,称为 MSI-X,可实

PCI-8134A.dll 入门级4轴伺服和步进运动控制卡与PCI-DASK.DLL

PCI-8134A 入门级4轴伺服和步进运动控制卡 8134A.dll(ADLINK—凌华科技) PCI-DASK.DLL //DASK Data Types typedef unsigned char U8; typedef short I16; typedef unsigned short U16; typedef long I32; ty

了解PCI Express的Posted传输与Non-Posted传输

0.写在前面 本文首发于公众号【两猿社】,后续将在公众号内持续更新~ 其实算下来接触PCIe很久了,但是由于之前换工作,一直没有系统的学习和练手项目,现在新项目买了Synopsys的PCIe IP,总算是有机会和时间来整理学习了~~~ 目前PCI Express总线取代PCI总线成为PC局部总线的主流,且PCIe在很大程度上继承了PCI的设计思想,可以说PCI是PCIe的基础,本文

通用嵌入式系统测试平台PCI架构介绍

3、 ETest-PCI架构产品 3.1 产品简介 PCI总线架构产品的硬件部分由工控机箱、CPU卡式工业主板、工控底板、与各类PCI接口板卡组成。工控机箱中安装CPU卡式工业主板、底板与各类PCI接口板卡,其中PCI接口板卡包括了RS232、RS422、RS485、CAN、1553B、AD采集、DA转换、DI/DO等常见接口。 PCI总线架构产品的软件部分与USB架构产品的软件部分类似

装备软件通用嵌入式系统自动化测试平台PCI架构特点

通用嵌入式系统自动化测试平台 通用嵌入式系统测试平台(Embedded System Interface Test Studio,简称: ETest)是针对嵌入式系统进行实时、闭环、非侵入式测试的自动化测试平台,适用于嵌入式系统在设计、仿真、开发、调试、测试、集成验证和维护等各阶段配置项级别和系统级别的动态测试与验证。 ETest提供了针对嵌入式系统的半实物硬件在环仿真测试环境,通过模拟

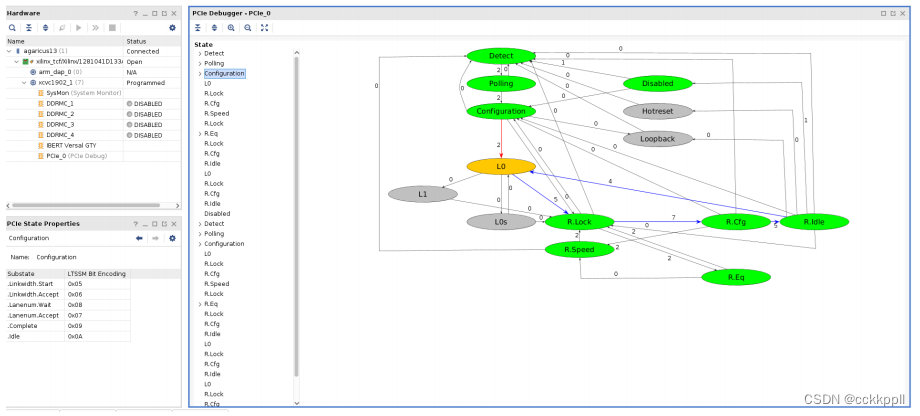

vivado 高带宽存储器 (HBM) 监控器、PCI Express 链路调试

高带宽存储器 (HBM) 监控器 某些 Virtex ® UltraScale+ FPGA 包含集成高带宽存储器 (HBM) 控制器和存储器堆栈。集成 HBM 控制器和存储器堆栈 包含性能计数器和温度传感器。 HBM 监控器可随时用于实时访问、采集和导出 HBM 裸片上的性能监控和温度传感器 数据。 HBM 监控器中的 GUI

2024妈妈杯数学建模A 题思路分析-移动通信网络中 PCI 规划问题

# 1 赛题 A 题 移动通信网络中 PCI 规划问题 物理小区识别码(PCI)规划是移动通信网络中下行链路层上,对各覆盖 小区编号进行合理配置,以避免 PCI 冲突、 PCI 混淆以及 PCI 模 3 干扰等 现象。 PCI 规划对于减少物理层的小区间互相干扰(ICI),增加物理下行控 制信道(PDCCH)的吞吐量有着重要的作用,尤其是对基站小区覆盖边缘的用户和发生信号切换的用户, 能有效地降低

2024年MathorCup数学建模A题移动通信网络中PCI规划问题解题文档与程序

2024年第十四届MathorCup高校数学建模挑战赛 A题 移动通信网络中PCI规划问题 原题再现: 物理小区识别码(PCI)规划是移动通信网络中下行链路层上,对各覆盖小区编号进行合理配置,以避免 PCI 冲突、PCI 混淆以及 PCI 模3 千扰等现象。PCI 规划对于减少物理层的小区间互相干扰(ICI),增加物理下行控制信道(PDCCH)的吞吐量有着重要的作用,尤其是对于基站小区覆