mesi专题

Cache多核之间的一致性MESI

快速链接: 【精选】ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈 思考: 1、为什么要学习MESI协议? 哪里用到了?你确定真的用到了? 2、MESI只是一个协议,总得依赖一个硬件去执行该协议吧,那么是谁来维护或执行的呢? 3、你不理解的真的是MESI吗,真的需要学习MESI吗? 应该是cache架构吧 4、core0和core1之间的一致性是MESI? 那cluste

MESI与Volatile(二)

MESI缓存一致性协议 定义: 多核CPU的情况下有多个一级缓存,一致性协议MESI保证缓存内部数据的一致,不让系统数据混乱。 缓存行(Cache line):缓存存储数据的单元 缓存行状态: 状态描述监听任务M 修改 (Modified)该Cache line有效,数据被修改了,和内存中的数据不一致,数据只存在于本Cache中。缓存行必须时刻监听所有试图读该缓存行相对于主存的操作

并发、原子、可见有序性在MESI协议、内存屏障的硬件原理

众所周知的几个知识点 volatile保证了可见性和有序性,仅在32位long、double类型保证原子性;synchronized保障了原子、有序、可见性,实际上是内部锁;显式的可重入锁ReentrantLock或者一些工具类如Semaphore, CountDownLatch保障原子、有序、可见性,基于AQS,即AbstractQueuedSynchronizer实现; 那么它们的硬件级别原

Java——》MESI

推荐链接: 总结——》【Java】 总结——》【Mysql】 总结——》【Redis】 总结——》【Kafka】 总结——》【Spring】 总结——》【SpringBoot】 总结——》【MyBatis、MyBatis-Plus】 总结——》【Linux】 总结——》【MongoDB】 总结——》【Elastics

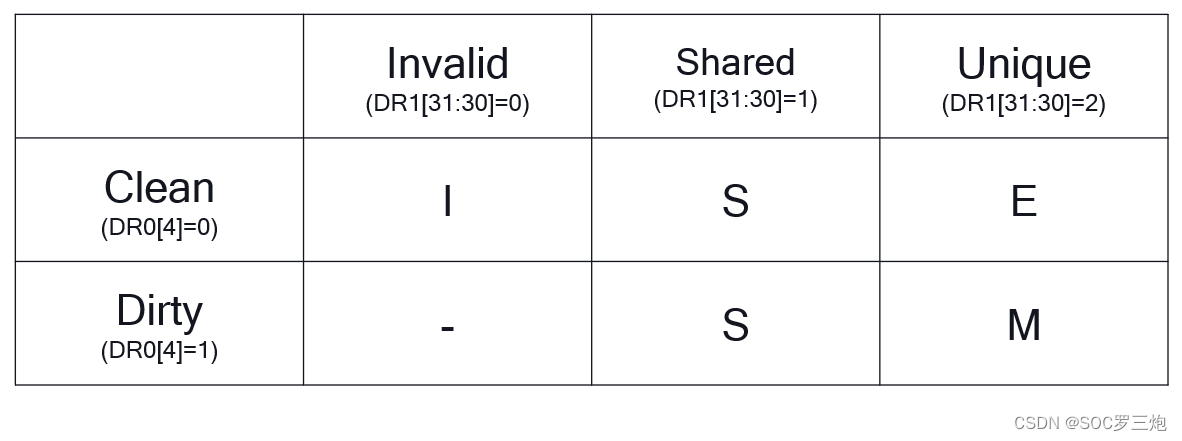

ARMv8如何读取cache line中MESI 状态以及Tag信息(tag RAM dirty RAM)并以Cortex-A55示例

Cortex-A55 MESI 状态获取 一,系统寄存器以及读写指令二,Cortex-A55 Data cache的MESI信息获取(AARCH 64)2.1 将Set/way信息写入Data Cache Tag Read Operation Register2.2 读取Data Register 1和Data Register 0数据并解码 参考文章: 一,系统寄存器以及读写指令