iodelay专题

UltraScale 架构 SelectIO 资源之IODELAY与IOSERDES仿真与使用

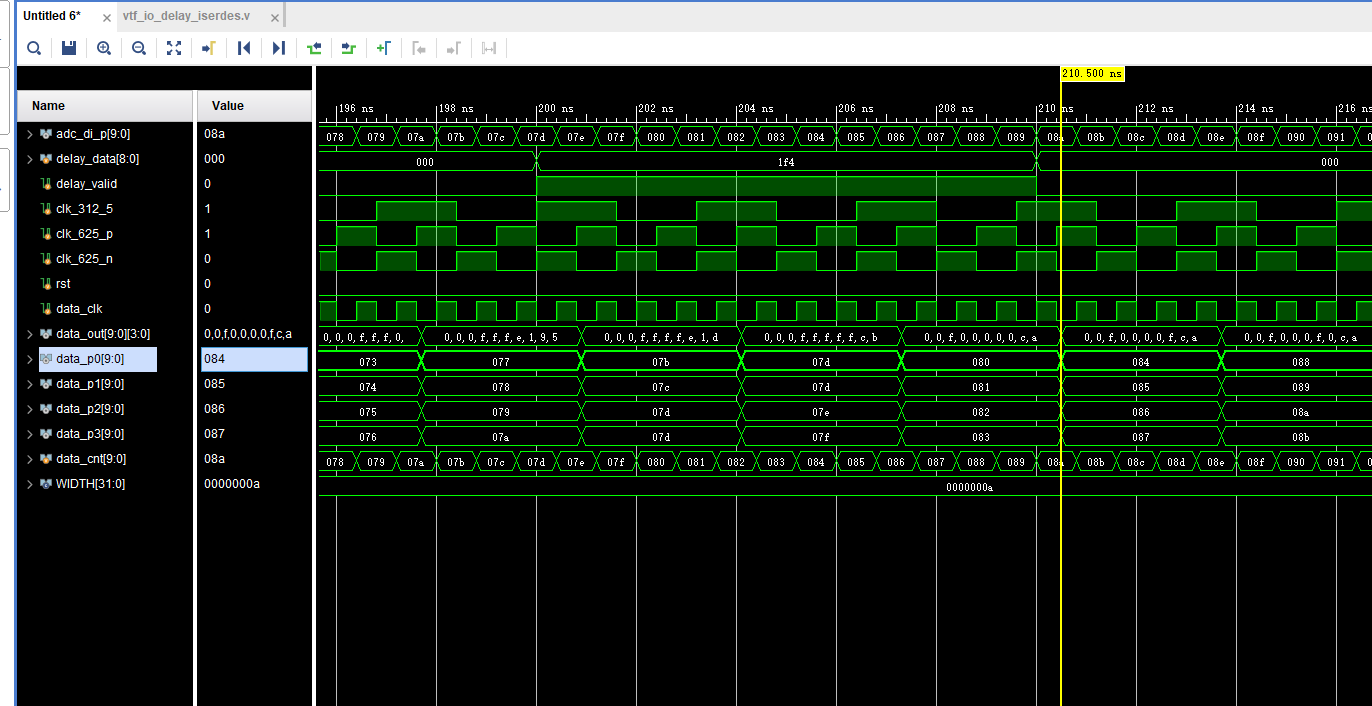

平台:vivado2018.3 具体内容见ug571-ultrascale-selectio IDELAYE3 在调试超高速信号的时候,需要使用iodelay+iserdes来调试校准输入信号。例如外部某ADC采样率为5GHZ,外部ADC使用2.5GHZ的时钟去采集输入信号。为了实现采集,adc芯片使用了4个1.25ghz采样率的小ADC来采集。但是由于FPGA的工艺,在FPGA内部无法

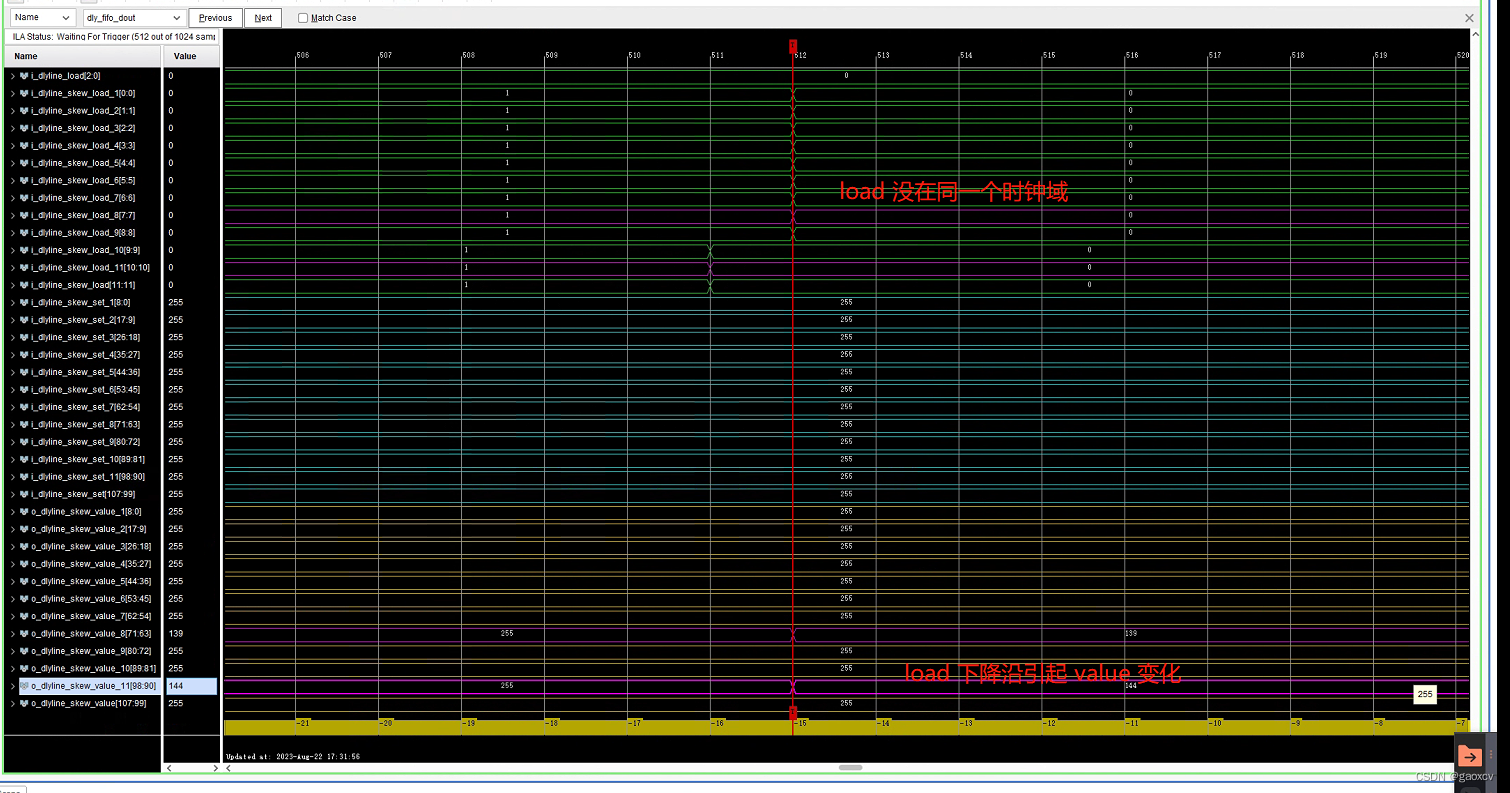

iodelay 使用总结

1 ku040 的 每个delay单元(1 tap)大概在2.5ps-15ps之间,共有512级delay,ku040后仿真中每级延时 4.7ps左右,实测下来每级4.4ps 2 纯内部逻辑延时要用 idelay,不能用odelay 3 参考时钟ref_clk要求200-2667M,100M有时会报错,有时会警告⚠,但是只要生成bit留就可以正常使用