本文主要是介绍iodelay 使用总结,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1 ku040 的 每个delay单元(1 tap)大概在2.5ps-15ps之间,共有512级delay,ku040后仿真中每级延时 4.7ps左右,实测下来每级4.4ps

2 纯内部逻辑延时要用 idelay,不能用odelay

3 参考时钟ref_clk要求200-2667M,100M有时会报错,有时会警告⚠,但是只要生成bit留就可以正常使用

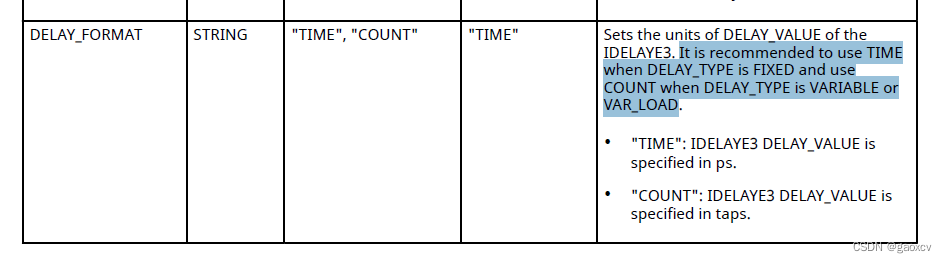

4 fixed 时推荐用 TIME模式, load/varible 时推荐用 count 模式,

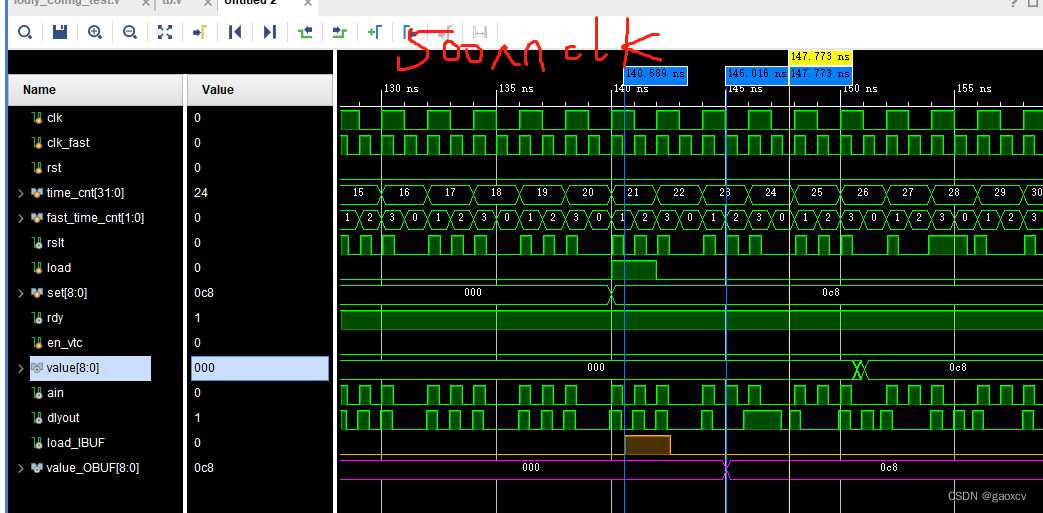

time模式一定要使用 idelayctrl 元件,等 idelayctrl 的 rdy 拉高时显示的value_out值即为设定的delay时间,count模式可以不用 idelayctrl 元件

idelayctrl 的 rdy 管脚不可作为 idelaye3 的 ~rst来使用,否则会导致calculate 无法完成,rdy管脚一直无法拉高,在 calculate时, idelayctrl 和 idelaye3 都不能 rst

TIME模式下只有 en_vtc = 1时 indeye3 可以 rdy odelaye3 不受此限制

load/varible 模式下如果想配置准确的 延时时间,

方式一 : 需要将其中一个delaye3 配置为TIME & FIXED 模式,然后在rdy & en_vtc 后读出 value_out 值,此时idelaye3每级 tap 延时 = 设定延时值/(value_out - 54), odelaye3每级tap延时 = 设定延时值/value_out ,然后在其他的 delaye3 中load 对应级数。

其中 54 是rx/idelaye3 特有的 align_dly ,即延时值设置为0时value_out的值(不是定值,50-60之间,平均为54,即 data和clk 到达 tx_rx_bitslice 的时间差,

参考: Xilinx Customer Community

方式二: 如果外部有方法可以测出 load 后延时变化的值,则可以直接用 y = kx + b 的方式,分别测出1级和500级的延时,相减,可得到 每级的延时 x 和 初始误差 b 的值

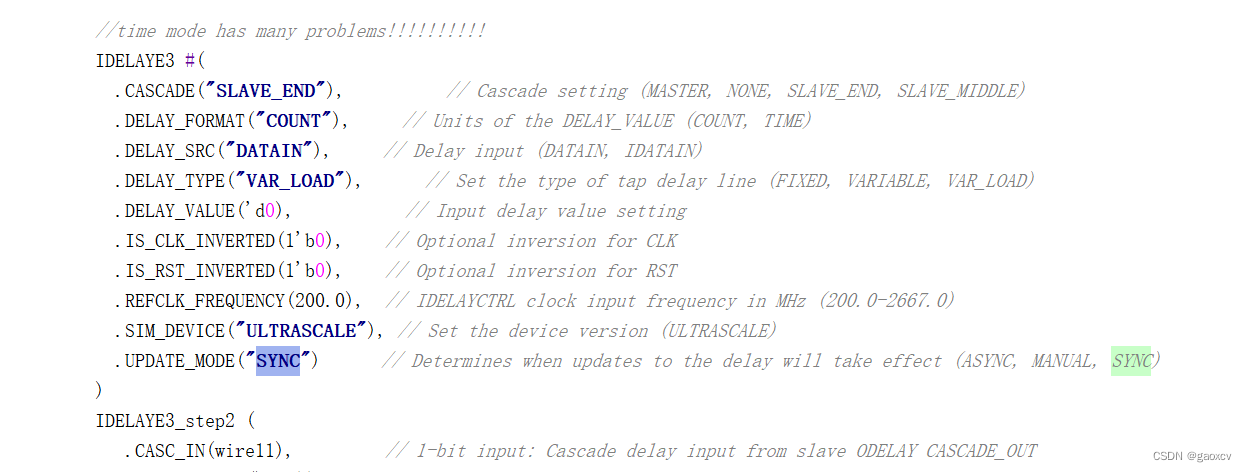

5 使用cascade模式要按照如下方案ug571 p176

级数没有限制,1,2,3. 4,,,,,n 级 级联都可以,每个单端pin都有 1个 idly + 1个odly

级联只能device 界面中 向下,不能超过bank 的边界或中点

wire wire10,wire11,wire12,wire13;IDELAYE3 #(.CASCADE("MASTER"), // Cascade setting (MASTER, NONE, SLAVE_END, SLAVE_MIDDLE).DELAY_FORMAT("COUNT"), // Units of the DELAY_VALUE (COUNT, TIME).DELAY_SRC("DATAIN"), // Delay input (DATAIN, IDATAIN).DELAY_TYPE("VAR_LOAD"), // Set the type of tap delay line (FIXED, VARIABLE, VAR_LOAD).DELAY_VALUE('d1), // Input delay value setting.IS_CLK_INVERTED(1'b0), // Optional inversion for CLK.IS_RST_INVERTED(1'b0), // Optional inversion for RST.REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (200.0-2667.0).SIM_DEVICE("ULTRASCALE"), // Set the device version (ULTRASCALE).UPDATE_MODE("ASYNC") // Determines when updates to the delay will take effect (ASYNC, MANUAL, SYNC)

)

IDELAYE3_sys_inst10 (.CASC_IN(), // 1-bit input: Cascade delay input from slave ODELAY CASCADE_OUT .CASC_RETURN(wire13), // 1-bit input: Cascade delay returning from slave ODELAY DATAOUT.CASC_OUT(wire10), // 1-bit output: Cascade delay output to ODELAY input cascade.CE(1'b0), // 1-bit input: Active high enable increment/decrement input.CLK(clk_in0), // 1-bit input: Clock input.EN_VTC(1'b0), // 1-bit input: Keep delay constant over VT.INC(1'b0), // 1-bit input: Increment / Decrement tap delay input.CNTVALUEIN(i_sysclk_iodly_set[26:18]), // 9-bit input: Counter value input .CNTVALUEOUT(o_sysclk_iodly_value[26:18]), // 9-bit output: Counter value output .LOAD(i_rate_load_en[2]), // 1-bit input: Load DELAY_VALUE input.IDATAIN(), // 1-bit input: Data input from the IOBUF .DATAIN(t_edge_n[1]), // 1-bit input: Data input from the logic .DATAOUT(t_edge1_n_iodly), // 1-bit output: Delayed data output .RST(rst) // 1-bit input: Asynchronous Reset to the DELAY_VALUE

);ODELAYE3 #(.CASCADE("SLAVE_MIDDLE"), // Cascade setting (MASTER, NONE, SLAVE_END, SLAVE_MIDDLE).DELAY_FORMAT("COUNT"), // (COUNT, TIME).DELAY_TYPE("VAR_LOAD"), // Set the type of tap delay line (FIXED, VARIABLE, VAR_LOAD).DELAY_VALUE('d100), // Output delay tap setting.IS_CLK_INVERTED(1'b0), // Optional inversion for CLK.IS_RST_INVERTED(1'b0), // Optional inversion for RST.REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (200.0-2667.0)..SIM_DEVICE("ULTRASCALE"), // Set the device version (ULTRASCALE, ULTRASCALE_PLUS,// ULTRASCALE_PLUS_ES1, ULTRASCALE_PLUS_ES2).UPDATE_MODE("ASYNC") // Determines when updates to the delay will take effect (ASYNC, MANUAL,// SYNC))ODELAYE3_inst10 (.CASC_OUT(wire11), // 1-bit output: Cascade delay output to IDELAY input cascade.CASC_IN(wire10), // 1-bit input: Cascade delay input from slave IDELAY CASCADE_OUT.CASC_RETURN(wire12), // 1-bit input: Cascade delay returning from slave IDELAY DATAOUT.CE(1'b0), // 1-bit input: Active high enable increment/decrement input.CLK(clk_in0), // 1-bit input: Clock input .EN_VTC(1'b0), // 1-bit input: Keep delay constant over VT.INC(1'b0), // 1-bit input: Increment/Decrement tap delay input.LOAD(i_rate_load_en[2]), // 1-bit input: Load DELAY_VALUE input.CNTVALUEIN(i_sysclk_iodly_set[26:18]), // 9-bit input: Counter value input.CNTVALUEOUT(), // 9-bit output: Counter value output .ODATAIN(), // 1-bit input: Data input.DATAOUT(wire13), // 1-bit output: Delayed data from ODATAIN input port .RST(rst) // 1-bit input: Asynchronous Reset to the DELAY_VALUE); IDELAYE3 #(.CASCADE("SLAVE_END"), // Cascade setting (MASTER, NONE, SLAVE_END, SLAVE_MIDDLE).DELAY_FORMAT("COUNT"), // Units of the DELAY_VALUE (COUNT, TIME).DELAY_SRC("DATAIN"), // Delay input (DATAIN, IDATAIN).DELAY_TYPE("VAR_LOAD"), // Set the type of tap delay line (FIXED, VARIABLE, VAR_LOAD).DELAY_VALUE('d100), // Input delay value setting.IS_CLK_INVERTED(1'b0), // Optional inversion for CLK.IS_RST_INVERTED(1'b0), // Optional inversion for RST.REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (200.0-2667.0).SIM_DEVICE("ULTRASCALE"), // Set the device version (ULTRASCALE).UPDATE_MODE("ASYNC") // Determines when updates to the delay will take effect (ASYNC, MANUAL, SYNC)

)

IDELAYE3_sys_inst11 (.CASC_IN(wire11), // 1-bit input: Cascade delay input from slave ODELAY CASCADE_OUT .CASC_RETURN(), // 1-bit input: Cascade delay returning from slave ODELAY DATAOUT.CASC_OUT(), // 1-bit output: Cascade delay output to ODELAY input cascade.CE(1'b0), // 1-bit input: Active high enable increment/decrement input.CLK(clk_in0), // 1-bit input: Clock input.EN_VTC(1'b0), // 1-bit input: Keep delay constant over VT.INC(1'b0), // 1-bit input: Increment / Decrement tap delay input.CNTVALUEIN(i_sysclk_iodly_set[26:18]), // 9-bit input: Counter value input .CNTVALUEOUT(), // 9-bit output: Counter value output .LOAD(i_rate_load_en[2]), // 1-bit input: Load DELAY_VALUE input.IDATAIN(), // 1-bit input: Data input from the IOBUF .DATAIN(), // 1-bit input: Data input from the logic .DATAOUT(wire12), // 1-bit output: Delayed data output .RST(rst) // 1-bit input: Asynchronous Reset to the DELAY_VALUE

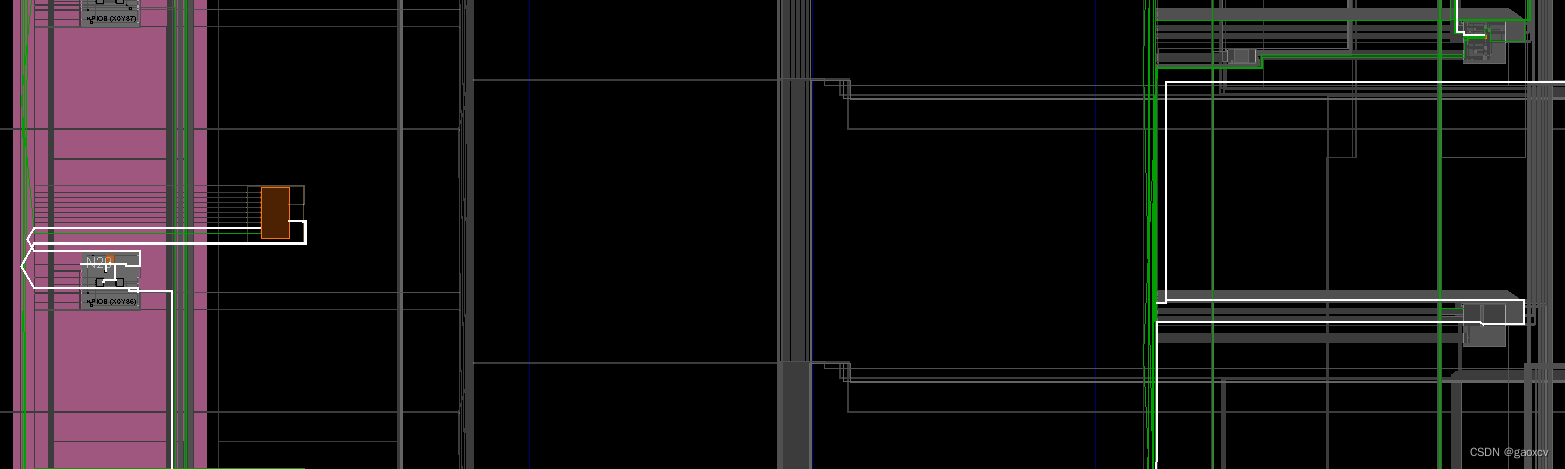

);6 每一个管脚都对应一个 BITSLICE_RX_TX ,在输入时,进入的信号会先进入对应的 BITSLICE_RX_TX ,(如果是差分 则会进入p管脚对应的BITSLICE_RX_TX),此BITSLICE_RX_TX 被占用,

如果要加 indly/oupdly 单元,如果入口是 IDATAIN(Data input from the IOBUF)则会将 indly

例化在当前被占用的 bitslice_rx_tx, 如果入口是 DATAIN(Data input from the logic),则穿过当前 BITSLICE_RX_TX 出来后进入其他的 BITSLICE_RX_TX(被例化成了indly),如下图

同理,输出时,若是最终输出 不是 outdly,则输出走线也要穿过对应的 bitslice_rx_tx,从而造成占用

可以用 set_property LOC BITSLICE_RX_TX_X0Y191 [get_cells {trig_cdc_inst/pin_gen[0].IDELAYE3_cmph} ] 的方式强制约束到对应位置,已经占用的除外

7 idelay 不能延迟clk,要精确延迟 clk 只能使用 mmcm或者pll 的 fine phase 功能

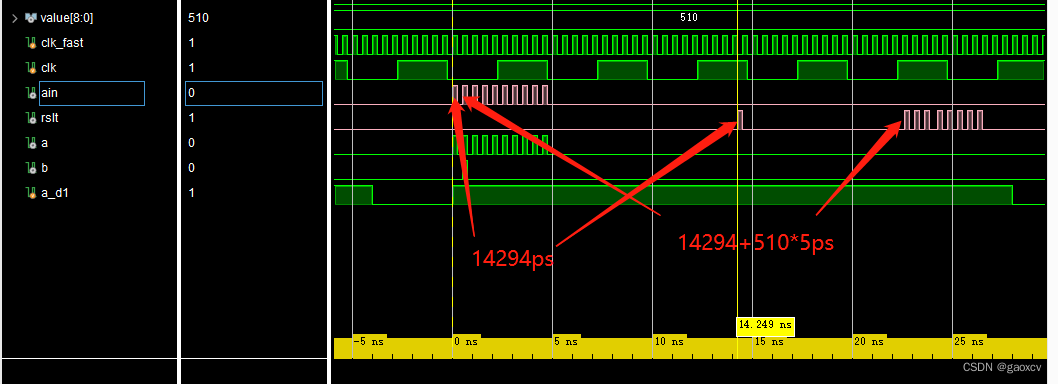

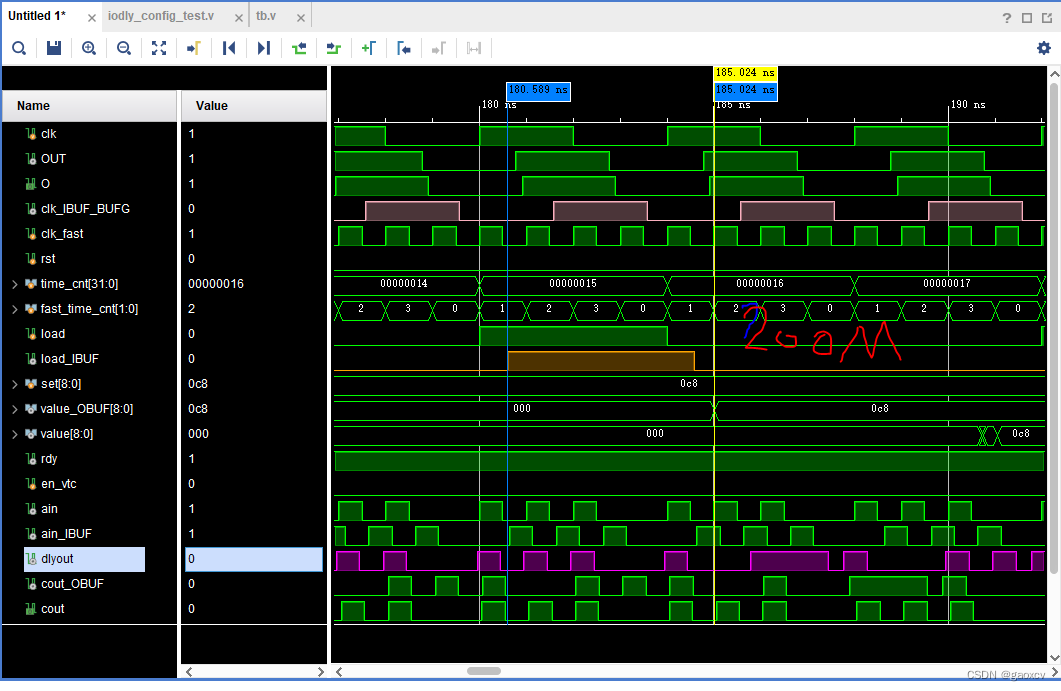

8 如果updata_mode 选了sync,则 新load 的 delay 会在 data数据 通过一个脉冲后再生效(如下图),

如果选 async, 则会在 上升沿 固定的时间(5-9ns左右)后生效

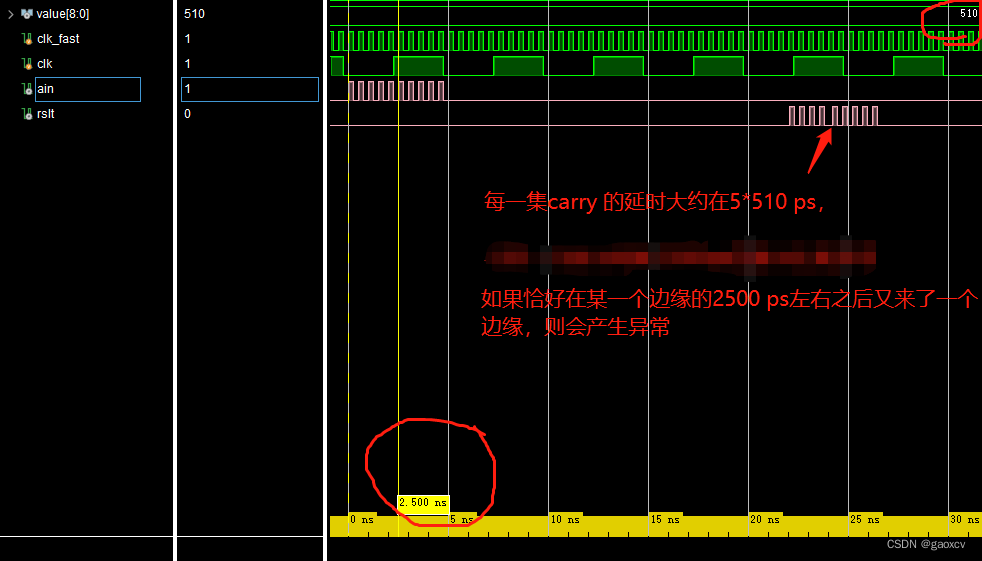

9 如果有级联,每一级的 iodlye3 延时值为 X,则 发送一个边缘 后 间隔 X之内不能再发边缘,否则会有异常latch, 导致 延时后的波形与 延时前不一致,并且异常的时间不可预测

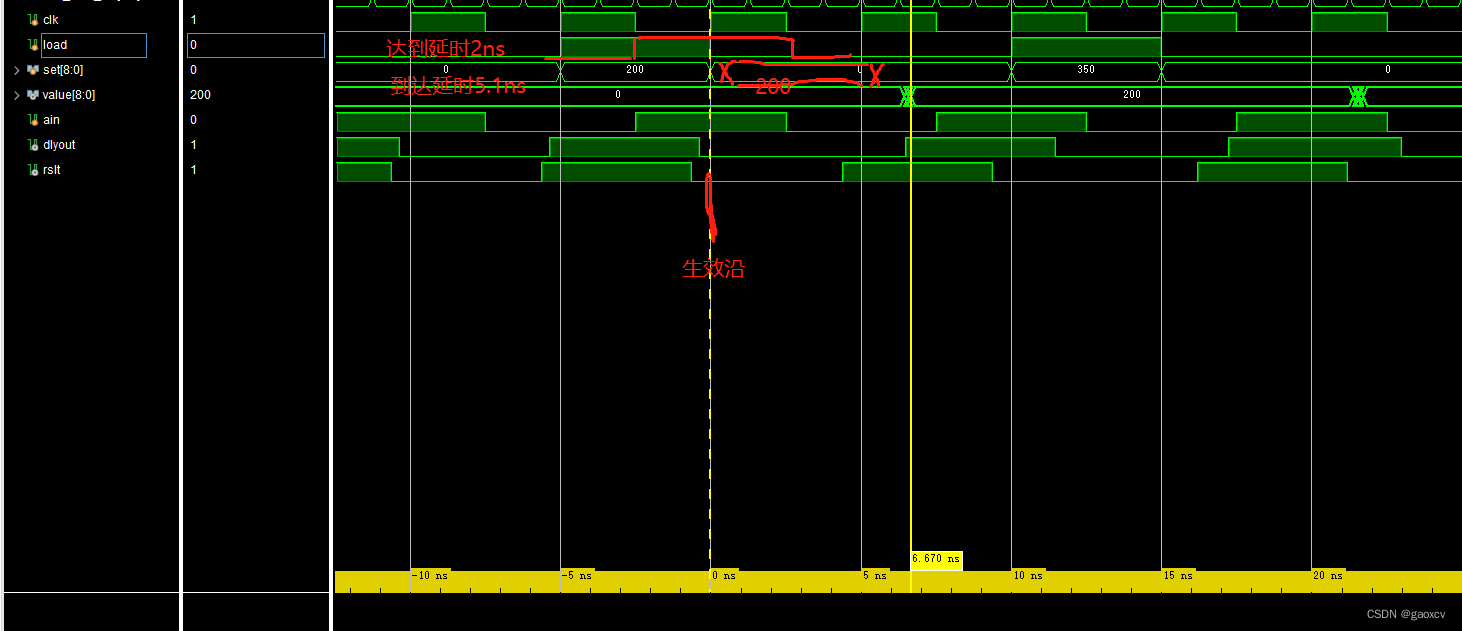

10 在配置生效的 clk上升沿时,如果延时链的 set 值经过路径延时,刚好在此位置附近到达,会导致此次边缘延时不确定

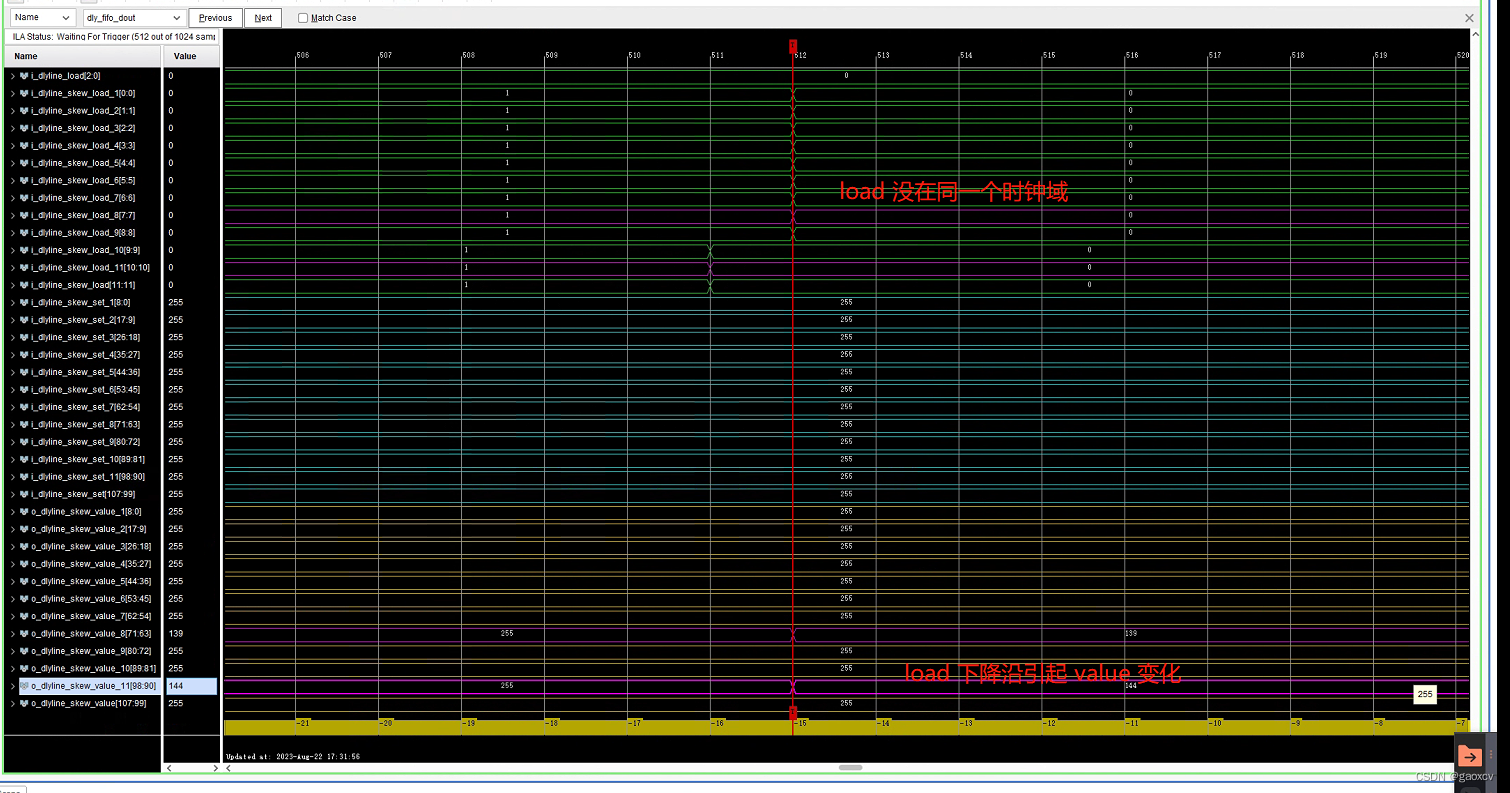

11 注意,配置的 load 一定要在 clk 对应的时钟域 内,否则 load 结束时可能会引起亚稳态

这篇关于iodelay 使用总结的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!