gmii专题

FPGA——三速自适应以太网设计(2)GMII与RGMII接口

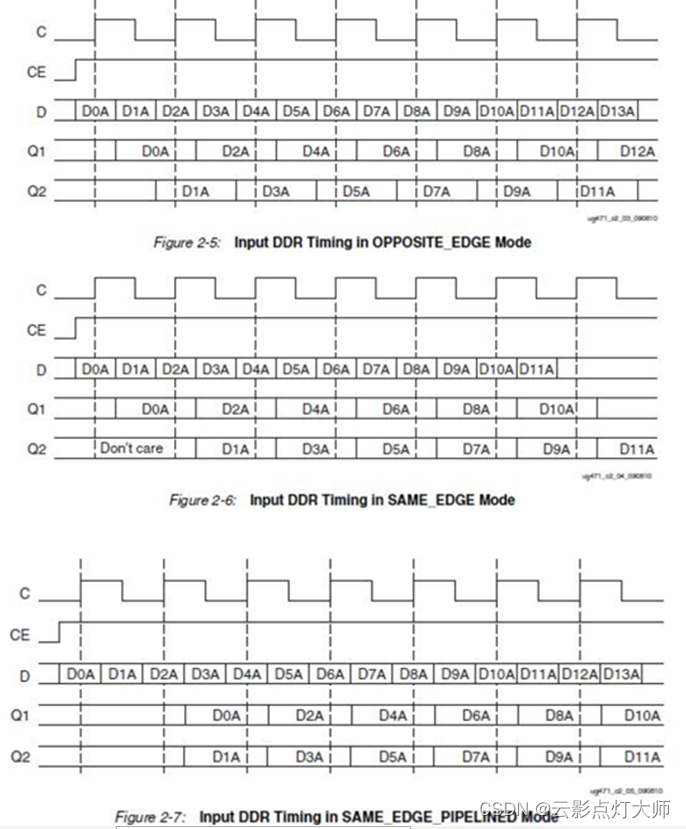

FPGA——以太网设计(2)GMII与RGMII 基础知识(1)GMII(2)RGMII(3)IDDR GMII设计转RGMII接口跨时钟传输模块 基础知识 (1)GMII GMII:发送端时钟由MAC端提供 下降沿变化数据,上升沿采集数据 (2)RGMII 时钟是双沿采样 RGMII:ETH_RXCTL线同时表示有效和错误,有效和错误位相异或得到。 时钟偏移,方便

FPGA UDP协议栈:基于88E1111,支持RGMII、GMII、SGMII三种模式,提供3套工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐我这里已有的以太网方案本协议栈的 1G-UDP版本本协议栈的 10G-UDP版本本协议栈的 25G-UDP版本1G 千兆网 TCP-->服务器 方案1G 千兆网 TCP-->客户端 方案10G 万兆网 TCP-->服务器+客户端 方案 3、该UDP协议栈性能4、详细设计方案设计架构框图网络调试助手网络PHYIDELAYE源语1G/2.5G Ethern

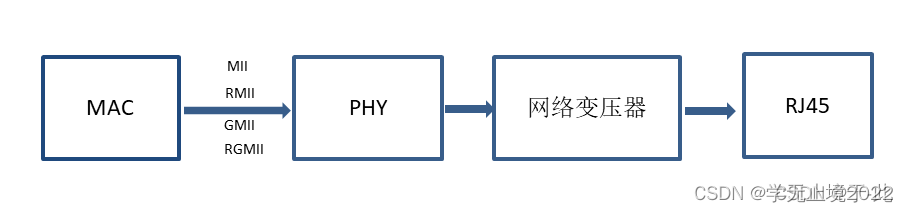

MII、RMII、GMII、RGMII接口是什么 用在什么地方

mac芯片和phy芯片之间的通信接口 MII(Media Independent interface):媒体独立接口,也叫介质无关接口。它是MAC和PHY之间的通信接口。MII数据接口有2根控制线和16根数据线组成。当CLK信号为25MHz(对应100Mb/s)或2.5MHz(对应10Mb/s)。 RMII(Reduced Media Independent Interface):独立于介质接

MII、RMII、 SMII、GMII、RGMII、SMI接口介绍

简要介绍 这几种接口是我们常说的网卡中应用的接口,应用于MAC和PHY直接的通信接口,符合IEEE定义的标准,不同厂家生产的网卡也都是按照标准生产的,所以我们能直接换网卡使用。 接口说明 SMI接口是MAC对PHY的控制接口,叫做站管理接口,总共两根线,一根时钟线,一根数据线。 MII接口是MAC与PHY之间的数据通信接口,叫做介质独立接口。 而RMII、 SMII是对MII的简化,缩减了