cyclone专题

Quartus Cyclone I II III IVE 器件型号

玩耍了一个 EP2 型号的开发板,发现 安装的quartus13 没有Cyclone II 型号,经过探索发现了是版本不对。 https://www.intel.com/content/www/us/en/software-kit/711920/intel-quartus-ii-subscription-edition-design-software-version-13-0sp1-for-wi

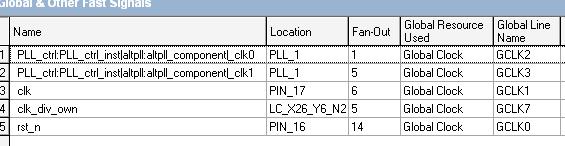

Cyclone器件全局时钟尽在掌控

转自:http://www.eefocus.com/ilove314/blog/11-09/231455_b9d40.html Cyclone器件全局时钟尽在掌控 首先感谢wind330兄的《掌控全局时钟网络资源》一文对于我的帮助。本文结合cyclone器件(因为特权最近正在使用这个系列的器件)对FPGA的时钟资源进行一些探讨,或者说是特权同学的一点认识和大家分享一下

Cyclone REGISTER360处理徕卡BLK360点云数据的流程(二、下载篇)

Cyclone REGISTER360处理徕卡BLK360点云数据的流程 一、软件安装 直接点击安装包安装、所有流程全部点下一步进行完成 二、下载扫描的点云数据 1、打开仪器、利用电脑连接仪器开放的无线网,无线网密码一般在安装电池的后盖上 2、在安装的软件后台文件夹中找到BLKDataManager 3、点击搜索并连接设备

Quartus FPGA JTAG配置芯片固化(Cyclone IV)

Cyclone IV配置芯片固化 FPGA有三种配置下载方式:主动配置方式(AS),被动配置方式(PS)和最常用的基于JTAG的配置方式。AS和PS模式主要是将比特流下载到配置芯片中(即一次烧录后,断电后代码不会消失),而JTAG模式既能将代码下载到FPGA中直接在线运行(速度快,调试时优选),也能通过FPGA将比特流下载到配置芯片中。 这里介绍在Quartus中如何使用JTAG固化配置芯片。

intel®Cyclone®10 LP设备家族引脚连接准则

1.英特尔®Cyclone®10 LP设备家族引脚连接准则 1.1 Clock and PLL Pins 1.2 Configuration/JTAG Pins 1.3 Differential I/O Pins 1.4 Reference Pins 1.5 Supply Pins 2. 英特尔Cyclone 10 LP引脚连接准则说明 1.除E144封

Cyclone器件全局时钟尽在掌控

http://bbs.ednchina.com/BLOG_ARTICLE_211992.HTM 首先感谢wind330兄的《掌控全局时钟网络资源》一文对于我的帮助。本文结合cyclone器件(因为特权最近正在使用这个系列的器件)对FPGA的时钟资源进行一些探讨,或者说是特权同学的一点认识和大家分享一下,有不对的欢迎指正。 翻开cyclon

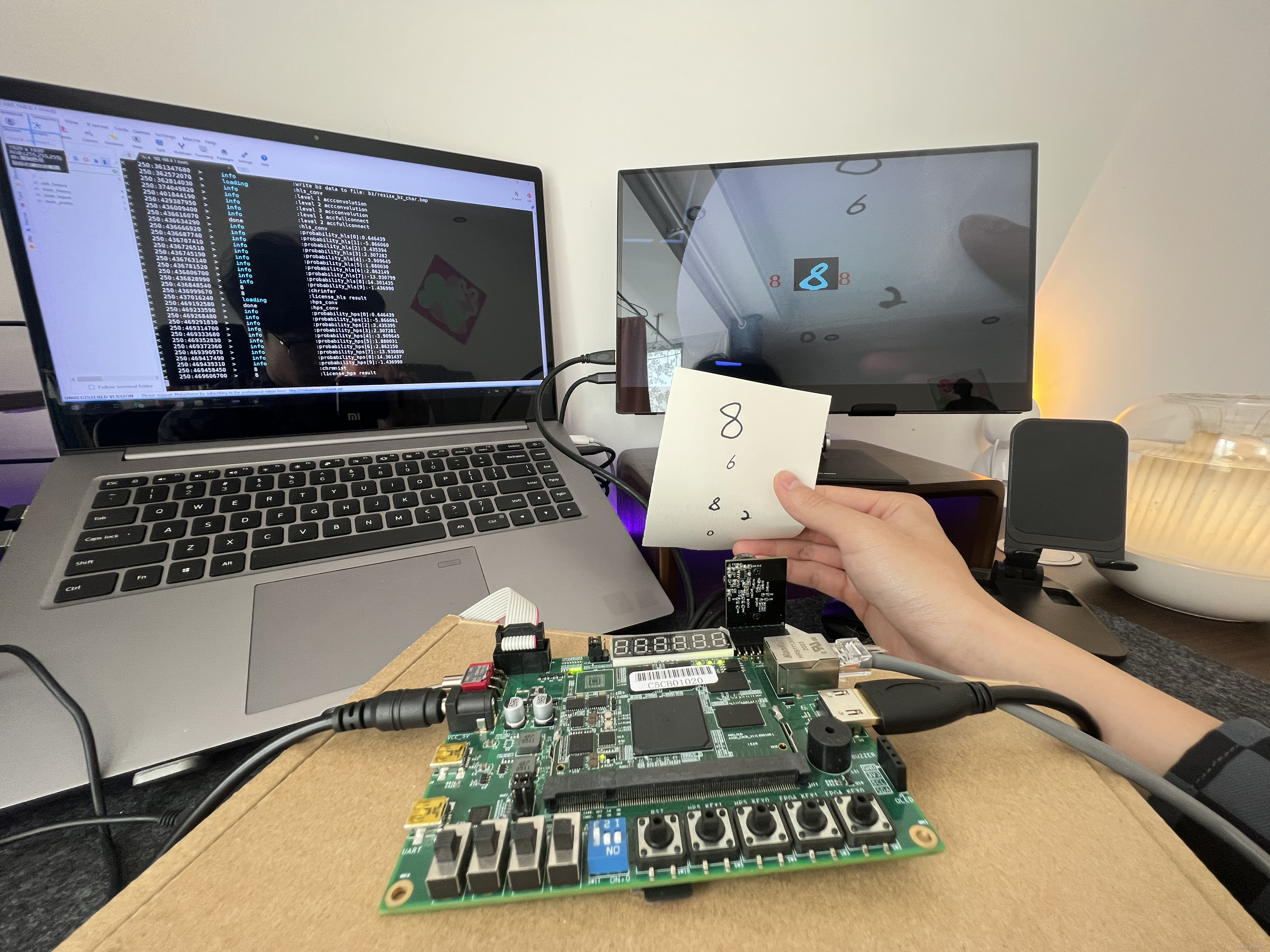

基于Cyclone V SoC利用HLS实现卷积手写体数字识别设计

引文 本文是基于英特尔Cyclone V SoC开发板,利用HLS技术实现三层卷积两层池化两层全连接推理运算的手写体数字识别设计。 硬件环境: Cyclone V SoC开发板OV5640 摄像头15.6寸 HDMI显示屏SD卡电脑 软件环境: Windows 10Quartus primeEclipse DS-5MobaXtermi++编译环境HLS工具 语言: CVerilog

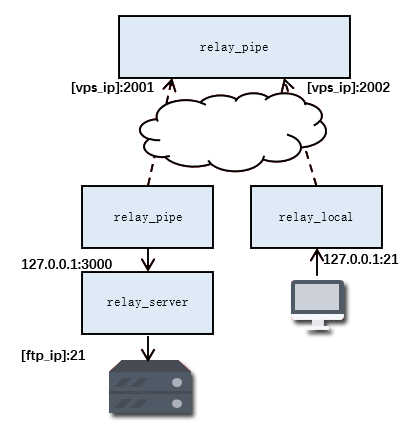

跨平台网络库Cyclone

转自:https://thecodeway.com/blog/?p=1472 非常好用,源码:https://github.com/thejinchao/cyclone 跨平台网络库Cyclone发布 Posted on 2017年5月11日 by jinchao 我在畅游工作时,曾经维护一个名为Cyclone的基础库,包括天龙八部在内的大部分端