cml专题

ECL、LVDS和CML电平

芯片间互连通常有三种接口:PECL(Positive Emitter-Coupled Logic)、LVDS(Low-Voltage Differential Signals)、CML(Current Mode Logic)。 各接口电平规范 ECL、PECL、LVPECL使用注意:不同电平不能直接驱动。中间可用交流耦合、电阻网络或专用芯片进行转换。以上三种均为射随输出结构,必须有电阻

差分逻辑电平 — LVDS、CML、LVPECL、HCSL互连

前言 首先了解差分逻辑电平、单端逻辑电平的基础知识 地址:常见的逻辑电平_常用的逻辑电平-CSDN博客 注: ECL >> PECL >> LVPECL演变; ECL速度快,驱动能力强,噪声小,但是功耗大,使用中需要负电源。为了简化电源,出现了PECL和LVPECL的输出模式。PECL电路速度快,驱动能力小,噪声小,高频。高功耗是PECL输出的主要缺点,且不同电平不能驱动

CML完成对MwT的收购

公司将毫米波 MMIC、分立器件和混合放大器方面的半导体专业知识相结合 总部位于英国的 CML Microsystems 已完成对总部位于加利福尼亚州弗里蒙特的 MicroWave Technology (MwT) 的收购。 MwT 成立于 1982 年,为商业无线通信、国防、太空和医疗 (MRI) 应用开发基于 GaAs 和 GaN 的 MMIC、分立器件和混合放大器产品。 MwT 总

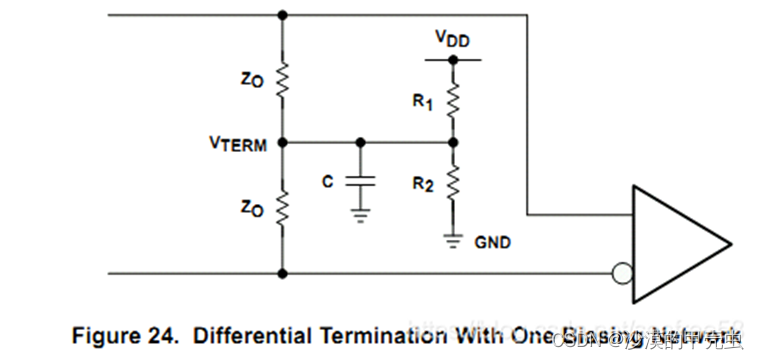

高速电路设计----第三章(3)LVPECL、CML逻辑电平详解

一、LVPECL介绍 LVPECL是ECL电平的正电源、低电压版本。 ECL电平是指发射极耦合逻辑(Emitter Coupled Logic),与TTL相同,ECL的主体结构由三极管组成,不同的是 ECL内部的三极管工作在非饱和状态(即截止或者放大状态),符合高速信号逻辑状态迅速变化的要求。从这点上来说,ECL速率的提升是以功耗的增大为代价的。

【科普】PECL/CML/LVDS高速差分接口原理

【摘要】 PECL/CML/LVDS这几种高速差分接口是我们工程中常用接口,本文将从接口起源、输出内部结构、输入内部接口三方面分别阐述各自原理。下一篇文章将重点阐述这几种高速接口之间的互联硬件设计。 1. 差分信号接口介绍 1.1 PECL 接口 PEL 是有 ECL 标准发展而来,在 PECL 电路中省去了负电源,较 ECL 电路更方便使用。PECL 信号的摆幅相对 ECL 要小