clk专题

linux驱动-CCF-2 of_clk_provider

CCF: common clock frameword of_clk_provider 总结 1. provider 注册时钟 hws[i] = desc->clk_register(cprman, desc->data); 参考https://mp.csdn.net/mp_blog/creation/editor/138153040 2. prov

Linux 内核clk 添加clk provider

内核把所有的clk provider管理维护起来,这些存放在of_clk_providers链表当中, 这个provider定义如下: struct of_clk_provider {struct list_head link; struct device_node *node;struct clk *(*get)(struct of_phandle_args *clkspec, void

stm8s003使用心得_时钟(CLK)

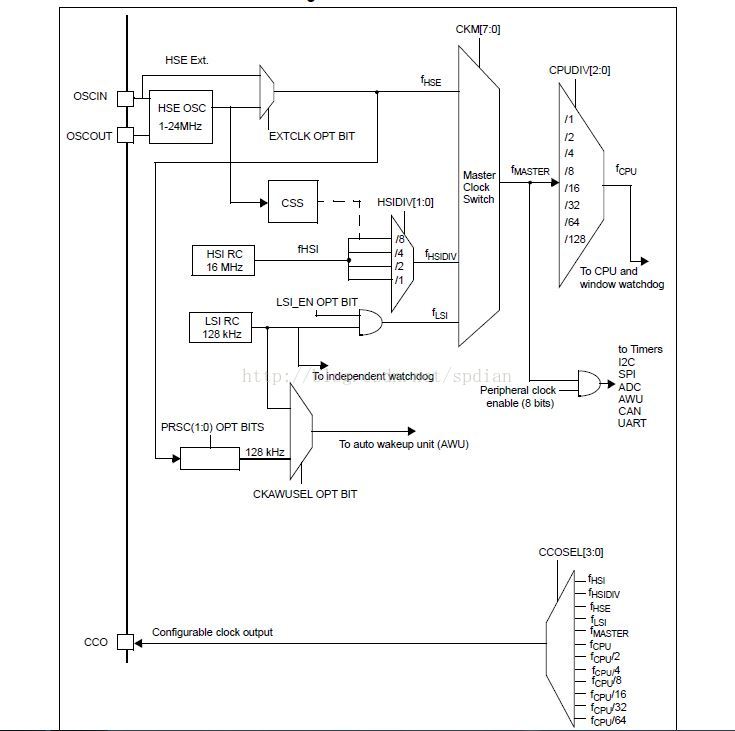

本文介绍stm8s003MCU的时钟(CLK)。前几天直接使用官方的库开发的程序,直接利用了库函数进行的时钟及TIMER的配置,其中有一些不太明白的地方,今天又仔细看了datasheet,有了更多的了解。 由于产品要控制成本,我选择使用的是MCU的内部时钟HSI 16MHz RC。通过下图1,可以更直观的了解MCU的整个时钟情况。

imx6 i2c clk频率修改

做个记录,以防自己忘记,默认i2c的频率为100k,只需修改board.c文件即可: static struct imxi2c_platform_data mx6q_i2c_data = {.bitrate = 100000, //修改为400K};产品一般需高速时钟通信,实时性需要非常的高,需结合实际情况修改,从机的频率高于主机的话是没有影响,但从机低于主机,则会读取错误的值。

do{ __HAL_RCC_GPIOH_CLK_ENABLE(); }while(0);

使用STM32 HAL库,专门用于在STM32微控制器上启用GPIOH (GPIO端口H)时钟。在此代码片段中,宏__HAL_RCC_GPIOH_CLK_ENABLE()用于启用GPIOH的时钟。do-while(0)结构通常用作为宏定义创建单行代码块的技巧。以这种方式使用do-while(0)结构允许宏像函数调用一样使用,并在控制语句中具有适当的作用域。它确保宏可以安全地用于if-else语句、

FPGA状态机 clk_divider_3_fsm

此图仅供参考,程序中3个always@语句,分别完成激励方程、转换方程和输出方程的功能。 Verilog程序 module clk_divider_3_fsm ( input sys_clk, input sys_rst_n, output reg

AD9371 官方例程HDL详解之JESD204B TX_CLK生成 (一)

AD9371 系列快速入口 AD9371+ZCU102 移植到 ZCU106 : AD9371 官方例程构建及单音信号收发 ad9371_tx_jesd -->util_ad9371_xcvr接口映射: AD9371 官方例程之 tx_jesd 与 xcvr接口映射 参考资料: UltraScale Architecture GTH Transceivers User Guide UG576

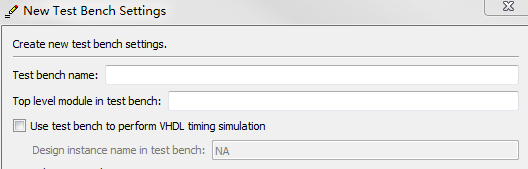

modelsim 仿真clk,rst_n时出现Hiz

1.在使用quartus ii联合modelsim仿真时出现了clk、rst_n为Hiz; 2.在出错的仿真时发现modelsim界面没有i1,正确的应该有,如图 1 所示; 图 1 3.我的问题出现在quartus ii调用testbench上,将Top Level Modul

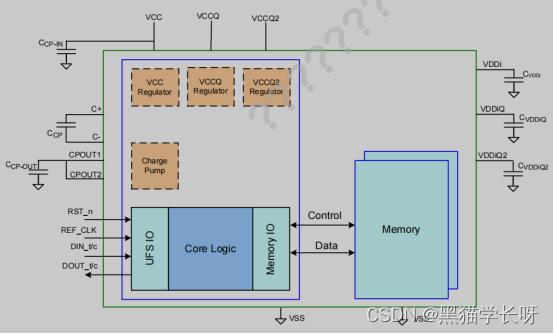

黑猫带你学UFS协议第9篇:UFS电气特性详解(Power、CLK、Reset等)

本文依据UFS3.1 JEDEC协议及个人工作经验整理而成,如有错误请留言。 文章为个人辛苦整理,付费内容,已加入原创维权,禁止私自转载。 文章所在专栏:《黑猫带你学:UFS协议详解》 1 概述 1.1 引脚系统框图 UFS强制支持secure mode。 图中有几个点进行解释一下: 1、charge pump电荷泵 一直不知道这种东西干什么的,网上解释也太过于专业,有些看不懂,对

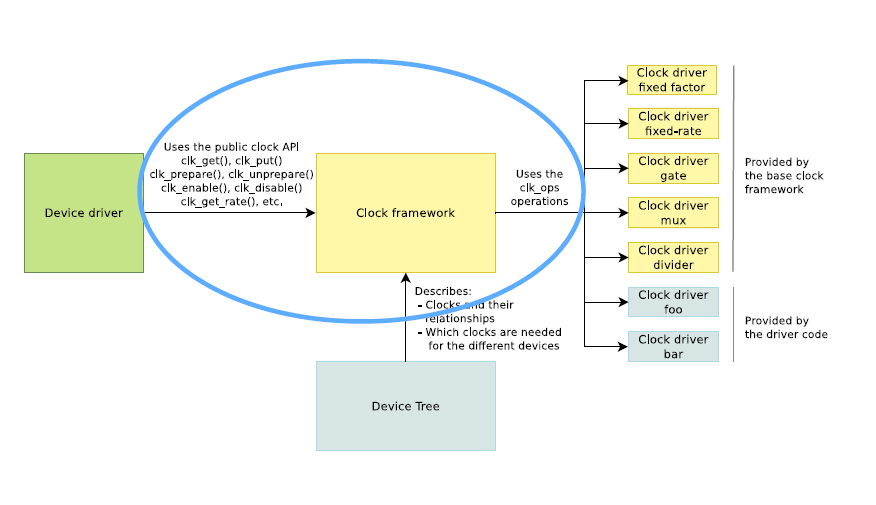

linux clk驱动框架

内核中提供了clk common framework子系统,用来完成对clock的统一管理。 我们将从如下几个方面来介绍clk子系统的内容: 1. clk framework简介2. clk framework的实现3. clk和device tree4. 如何添加自己的clock 一、 clk framework简介 clk framework是内核中用来统一管理clock