aurora8b10b专题

xilinx的Aurora8B10B的IP仿真及上板测试(高速收发器十七)

前文讲解了Aurora8B10B协议原理及xilinx相关IP,本文讲解如何设置该IP,并且通过示例工程完成该IP的仿真和上板。 1、生成Aurora8B10B IP 如下图所示,首先在vivado的IP catalog中输入Aurora 8B10B,双击该IP。 图1 查找Aurora 8B10B IP Aurora 8B10B相对GTX的配置相对简单,主要配置如下

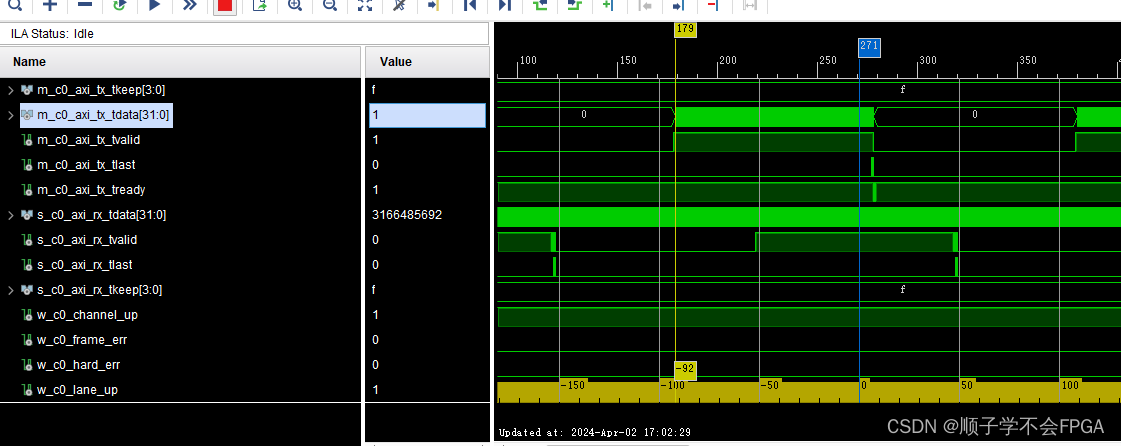

Aurora8b10b(2)上板验证

文章目录 前言一、AXI_Stream数据产生模块二、上板效果总结 前言 上一篇内容我们已经详细介绍了基于aurora8b10b IP核的设计,本文将基于此进一步完善并且进行上板验证。 设计思路及代码思路参考FPGA奇哥系列网课 一、AXI_Stream数据产生模块 AXIS协议是非常简单的,看过之前的AXI_FULL协议应该会很容易理解。 该模块有以下需要注意的点:

Aurora8B10B IP使用

Aurora 64B/66B IP概述 介绍 Aurora 8B/10B 内核支持 AMBA协议、AXI4-Stream 用户接口。 该内核使用 Zynq、Artix-7、Kintex-7 和 Virtex-7 系列、UltraScale和 UltraScale+系列上的高速串行收发器实现 Aurora 8B/10B 协议。 特点 吞吐量范围为 480 Mb/s 至 84.48 Gb/s