本文主要是介绍瑞萨RH850 SPI的异步传输,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

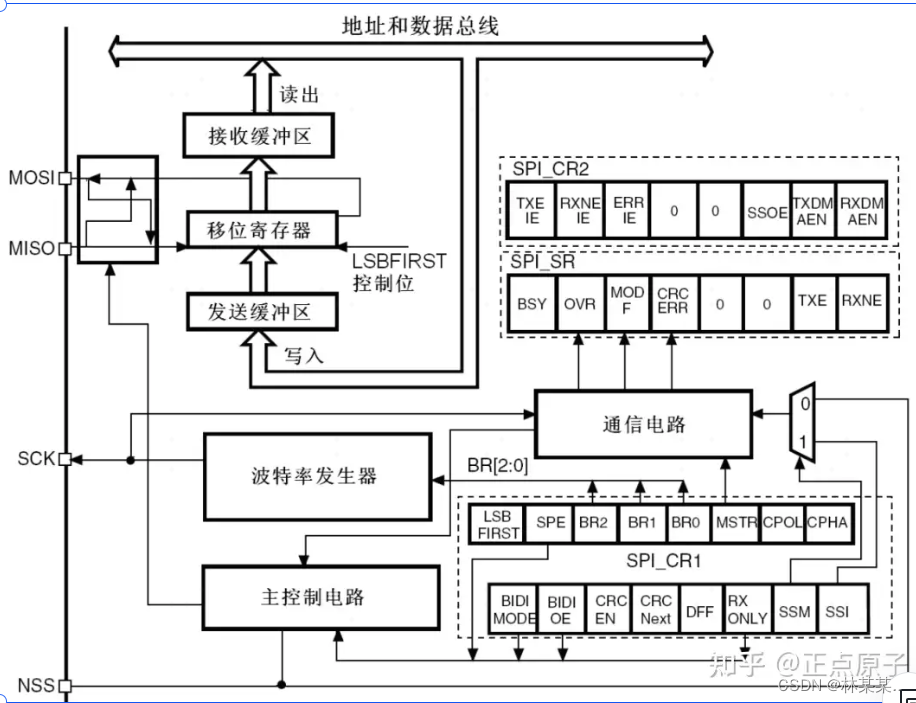

一、SPI工作原理

SPI (Serial Peripheralinterface),顾名思义就是串行外围设备接口。SPI是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,主要应用在EEPROM,FLASH,实时时钟,AD转换器

关于SPI协议,那么我们理解一句话即可。SPI的写操作和读操作是同步完成的。如果只进行写操作,主机只需忽略接收到的字节;反之,若主机要读取从机的一个字节,就必须发送一个空字节来引发从机的传输。

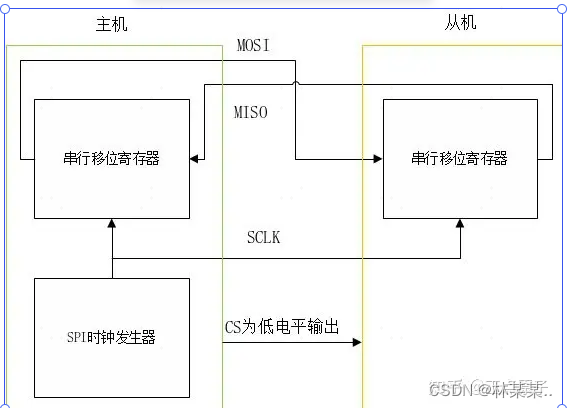

主机与从机连接关系图

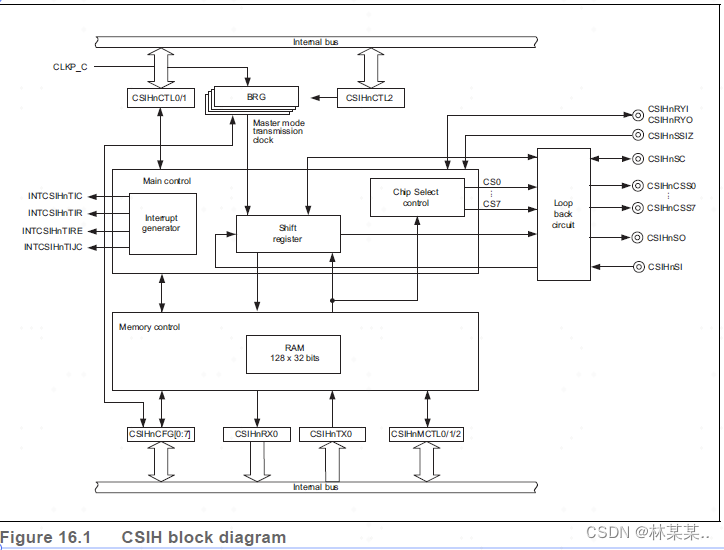

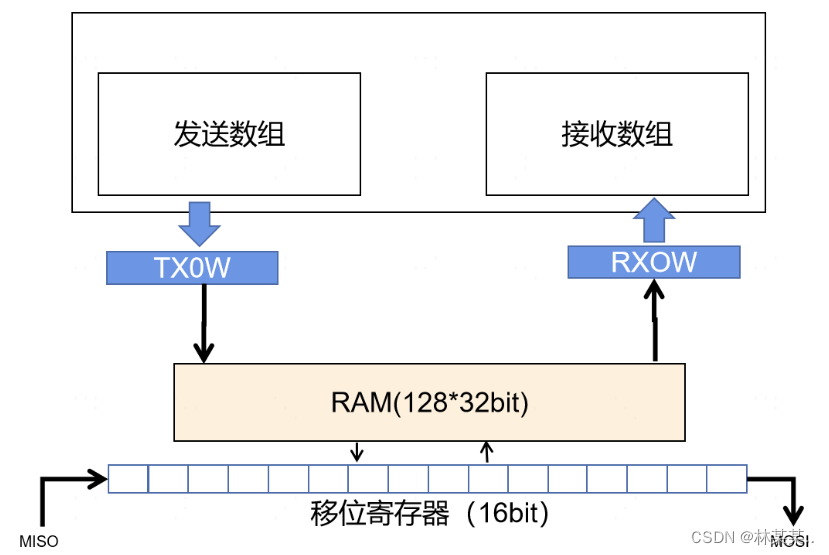

RH850/P1x-C SPI组成

RAM数据通过内部数据总线P_Bus向CSIH模块传输数据

-

CSIHnTX0W寄存器写数据接口

-

CSIHnRX0W寄存器读数据接口

-

CSIHnCFGx配置CSIH接口(波特率,奇偶校验,数据方向,数据长度,时间参数等)

-

CTL0/1/2 MCTL0/1/2控制寄存器

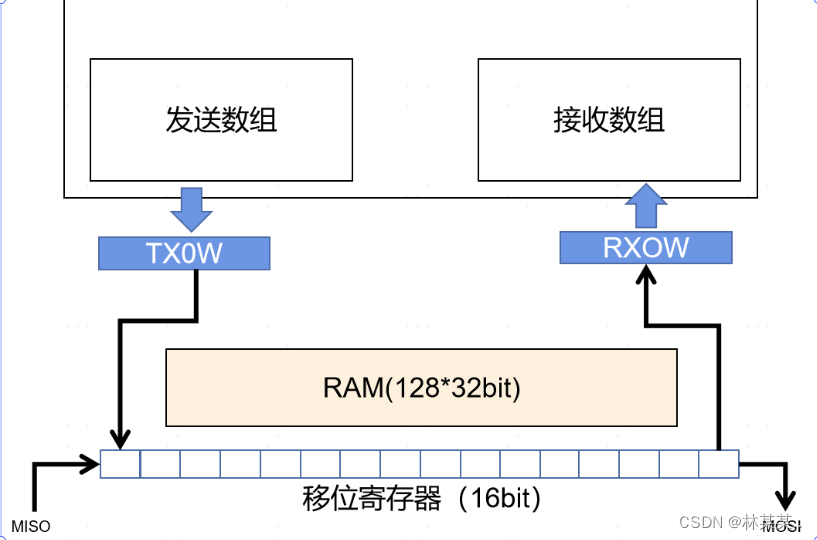

配置好CSIH后,RAM向TX0W中写入数据,CSIH自动将数据加载到移位寄存器中,并根据配置好的时钟,波特率,向MOSI上发送数据

同时,MISO将接收到的数据放到移位寄存器后面,当发送完16bit数据后也接收到了16bit数据,这时CSIH将移位寄存器的值复制到RX0W中,RAM可通过RX0W读取接收到的数据

-

CSIH提供一个128 words的RAM空间,4路SPI通道共用(1word = 32bit+7bit ECC)

-

二、SPI工作模式

1.Direct access mode直接访问

直接绕过CSIH提供的RAM区,当数据写入TX0W寄存器时,数据直接复制到移位寄存器中

-

2.Memory Mode

使用CSIH提供的RAM空间

根据操作方式不同又可分为3种

-

FIFO Mode

-

将数据写入CSIHnTX0W不用等待数据发送完成,可立即写入下一个数据,可以一直把FIFO写满

-

当接收到一帧数据后,会用接收到的数据覆盖原来发送数据位置

-

可通过CSIHnRX0W读取数据,读取一次后,FIFO指针自动移动到下一个数据,可以一直读完

-

Dual buffer mode

-

把128words的RAM空间氛围两份,一份64words

-

一份只负责存放发送数据,一份只负责存放接收数据

-

Transmit-only buffer mode

-

RAM空间只存放发送数据,接收数据不放到RAM中,只能从CSIHnRX0W读取

三、SPI发送数据长度

-

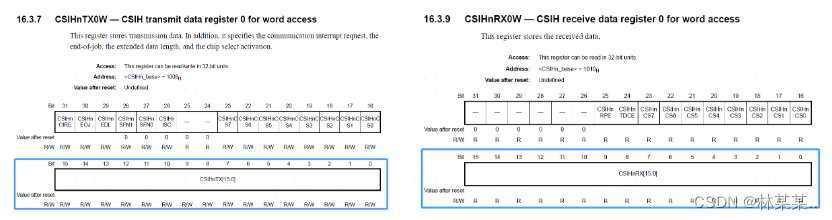

由于CSIHnTX0W / CSIHnRX0W和移位寄存器的数据长度只有16bit所以一次性最多只能发送16位数据

-

2~16bit Data length

当数据长度在2~16bit时,在发送过程中不需要修改配置,只要将数据发送到CSIHnTX0W 即可

-

Data length greater than 16 bits

-

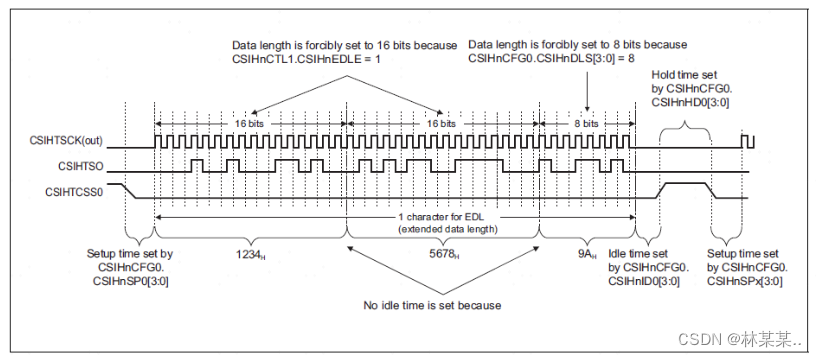

需要使能扩展数据长度位EDL is enabled by setting bit CSIHnCTL1.CSIHnEDLE to 1

-

CSIHnTX0W寄存器CSIHnEDL为表示这一块数据后是否还有数据(1有/0无)

-

当CSIHnTX0W.CSIHnEDL= 1时发送16位数据,CS不变

-

当CSIHnTX0W.CSIHnEDL= 0时发送CSIHnCFG0.CSIHnDLS[3:0]配置的数据长度,发送完成后CS拉高

Example

Example for sending 40-bit data (123456789AH) to CS0:

40 bits are split 2 × 16 bits plus 8 bits.

• Initialize CSIHnCFG0.CSIHnDLS0[3:0] = 8.

• To send 123456789AH with MSB first, write the following sequence to CSIHnTX0W:

– 20FE 1234H (CSIHnTX0W.CSIHnEDL = 1)

– 20FE 5678H (CSIHnTX0W.CSIHnEDL = 1)

– 00FE 009AH (CSIHnTX0W.CSIHnEDL = 0)

The following figure illustrates the timing.

四、SPI传输数据格式(大小端,略过)

LSB

MSB

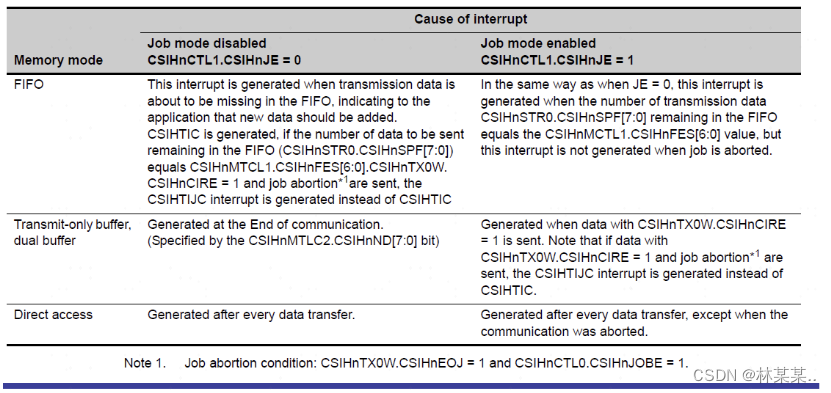

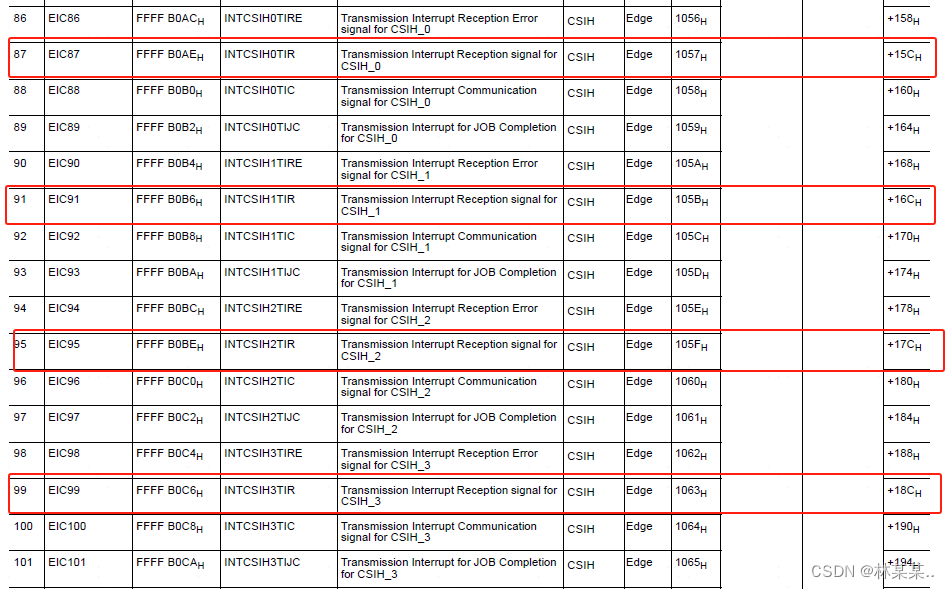

五、SPI中断

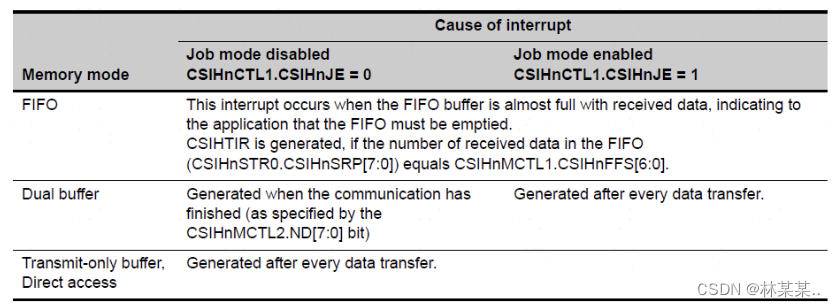

1. CSIHTIC (communication interrupt)发送数据中断

FIFO模块:发送指定数据的数据后产生中断

Direct access: 每一次数据发送完成后

2. CSIHTIR (communication interrupt)接收数据中断

FIFO模块:接收指定数据的数据后产生中断

Direct access: 每一次数据接收完成后

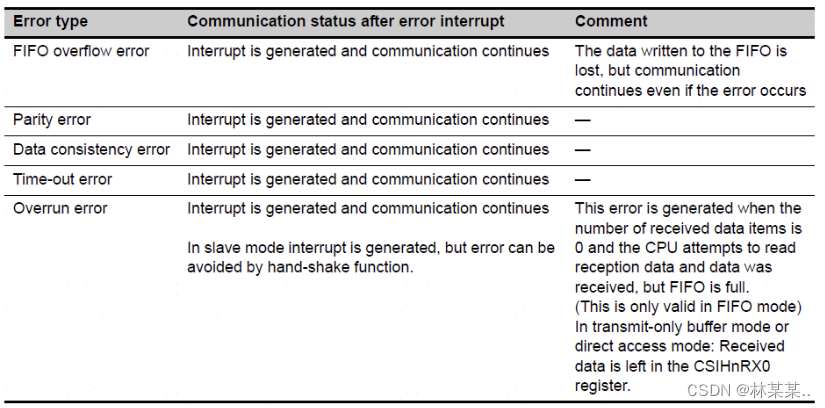

3. CSIHTIRE (error interrupt)错误中断

-

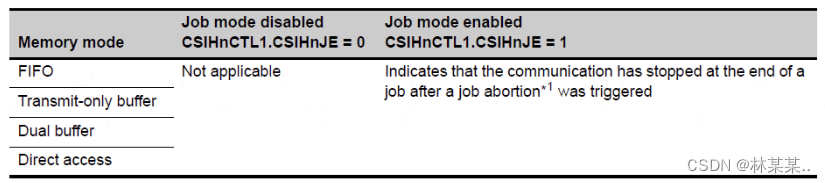

4.CSIHTIJC (job completion interrupt)job完成中断

JOB模式开启CSIHnCTL1.CSIHnJE

Job完成后产生中断CSIHnTX0W.CSIHnEOJ = 1

Job中断产生后会替代掉CSIHTIC 中断

六、SPI方案

六、SPI方案

-

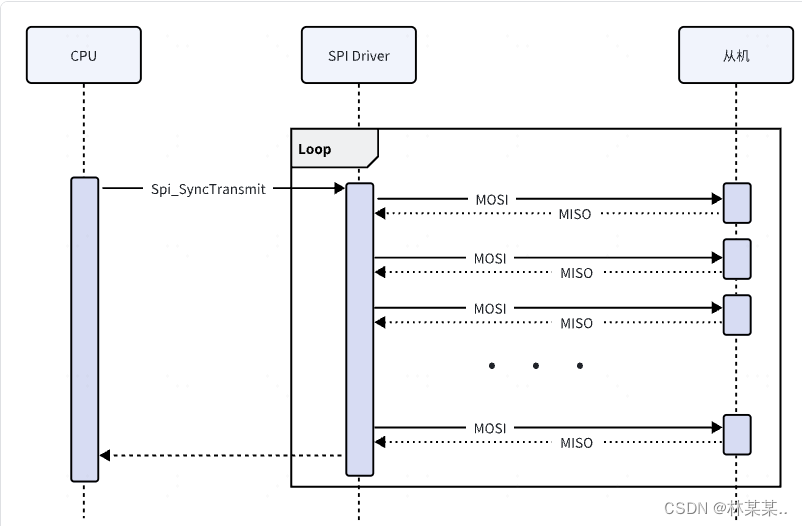

方案1:Direct access + 同步传输

-

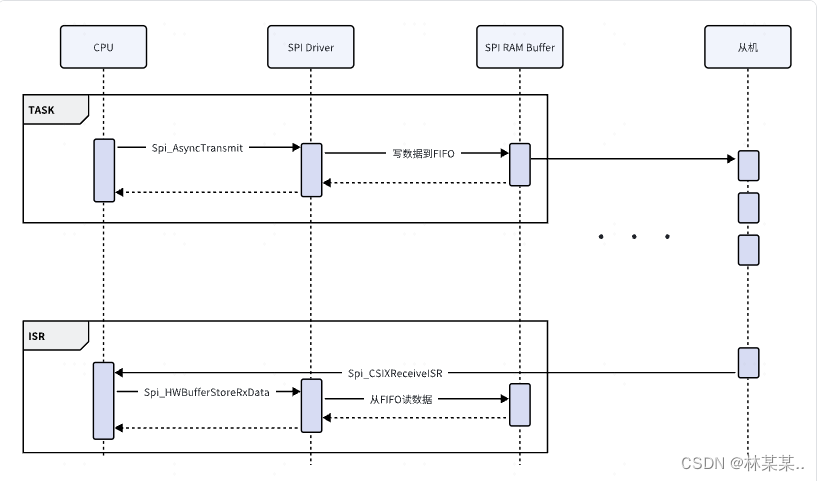

方案2:FIFO+异步传输+ISR

-

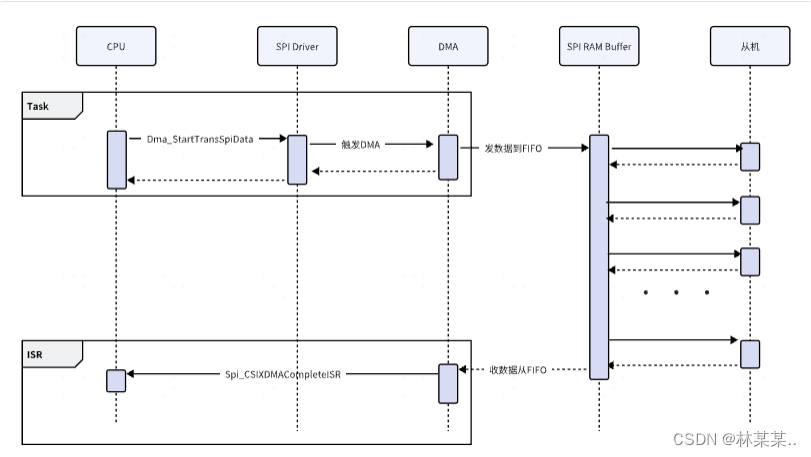

方案3:FIFO+异步传输+DMA+ISR

七、操作方法

1. Davinci SPI模块配置

SpiJobs: Hw Unit Synchronous配置为ASYNCHRONOUS

SpiMemoryMode:内存模式选择FIFO_MODE

SpiGeneral:使能异步通信

2. SPI接收中断注册

-

中断源选择INTCSIHnTIR,接收信号中断

3. 调用方式

在初始化中使用死等,异步的polling模式模拟同步进行通信

在周期化调用中,使用异步发送,中断接收的模式,节省CPU负载

这篇关于瑞萨RH850 SPI的异步传输的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!