本文主要是介绍FIFO Generate IP核使用——异步复位,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

FIFO Generator IP核提供了一个复位输入,当该输入被激活时,它会复位所有的计数器和输出寄存器。对于块RAM或分布式RAM实现,复位FIFO并不是必需的,可以在FIFO中禁用复位引脚。共有两种复位类型选项:异步复位和同步复位。

异步复位(rst)激活时,会异步地复位所有的计数器、输出寄存器和存储器。当实现复位时,它会在内部与每个相应的时钟域同步,以将FIFO的内部逻辑设置为已知状态。这种同步逻辑允许在IP核内部正确设置复位逻辑的定时,以避免闪烁和亚稳态行为。

在应用复位时,时钟必须可用。如果由于任何原因在复位时丢失了时钟,那么当时钟恢复时必须再次应用复位。违反这一要求可能会导致意外的行为。有时,忙碌信号可能会卡住,可能需要重新配置FPGA。

如果在异步复位时使用的是最慢时钟宽度的一个周期,并且断言发生在最慢时钟上升沿附近,那么复位检测可能无法正确进行,导致意外的行为。为了避免这种情况,总是建议将异步复位断言至少保持3个或C_SYNCHRONIZER_STAGE(以较大者为准)个最慢时钟周期。

1 使用RAM(BRAM)、分布式RAM(Distributed RAM)和移位RAM(Shift RAM)时钟时

当使用异步复位时,确保在两次连续复位之间有至少6个时钟周期(在独立时钟情况下为较慢的时钟)的间隔。以下是对这些类型FIFO在使用异步复位时的一些关键注意事项:

在使用块RAM(BRAM)的异步复位时,提供了一个额外的安全电路选项(如上图所示,Enable Safety Circuit),以确保BRAM输入信号的断言和去断言是同步发生的。如果使用安全电路选项,你需要在应用下一个重置或发起任何写操作之前,等待wr_rst_busy信号从1过渡到0。对于BRAM的DRC(Design Rule Check)警告,如果与异步复位和安全电路相关,可以视为误报。

如果选择了FIFO生成器的安全电路选项,需要确保复位(rst)信号在写/读时钟周期(以较慢者为准)中至少被断言为高(逻辑1)3个或C_SYNCHRONIZER_STAGE(以较大者为准)个周期。

对于AXI接口的异步复位,在IP核内部断言wr_rst_busy,在复位期间,AXI接口可能会暂时不可用,直到wr_rst_busy信号变为0,并且相关的*axi**valid/*axi**ready信号表明接口已准备好。

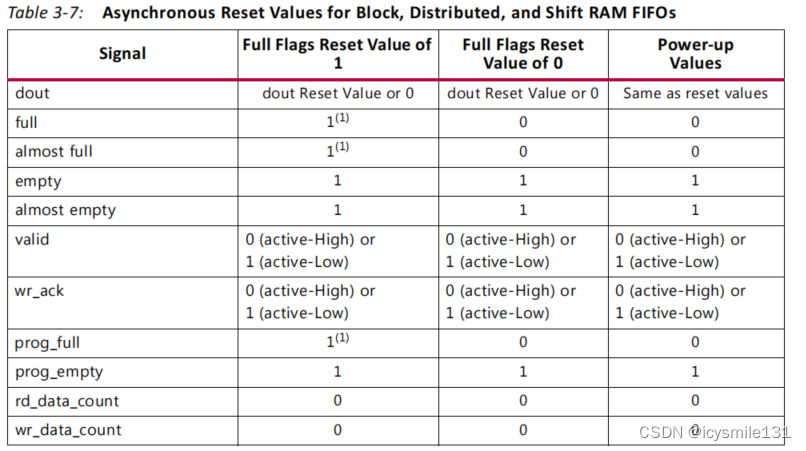

表3-7定义了块RAM、分布式RAM和移位RAM FIFO在加电和复位状态下输出端口的值。下溢信号(underflow)取决于rd_en(读使能)。如果rd_en被激活且FIFO为空,则下溢信号被激活。同样,溢出信号取决于wr_en(写使能)。如果wr_en被激活且FIFO已满,则溢出信号被激活。

对于这些FIFO配置,有两种可用的异步复位行为:满标志复位为1和满标志复位为0。根据所选的满标志复位值,复位要求和FIFO的行为是不同的。FIFO的复位需求和行为会根据所选择的满标志复位值(full flags reset value)的不同而有所差异。

复位是边沿触发的,而不是电平触发的。同步逻辑寻找rst的上升边沿,并为IP核创建一个内部复位。

请注意,异步复位的断言会立即导致IP 核进入预定的复位状态——这不依赖于任何时钟切换。

复位同步逻辑用于确保不同时钟域中的逻辑在同一时间退出复位模式——这是通过将异步复位的去断言同步到适当的时钟域来实现的。这样做可以避免闪烁和亚稳态。这种同步分别在读写时钟上检测到异步复位的上升边沿后,需要三个时钟周期(写或读)来完成。

为了避免意外行为,建议遵循复位时序要求,并在rst被断言/置高时不建议驱动/切换wr_en/rd_en。

满标志复位值为1

在这个配置中,FIFO需要至少一个写/读时钟周期的异步复位脉冲(以较慢者为准)。当在写时钟的上升沿检测到复位时,需要3个写时钟周期来完成适当的复位同步。在这段时间内,full、almost_full和prog_full标志会被复位(asserted)。当复位被撤销后,这些标志在五个时钟周期(wr_clk/clk,取决于使用的是写时钟还是公共时钟)后撤销(deasserted),然后FIFO可以接受写操作。

为了确保在FIFO IP核处于复位状态时不会发生写操作,full和almost_full标志会被复位(asserted)。当FIFO退出复位状态并准备好进行写操作时,full和almost_full标志会撤销(deassert)。这通常发生在异步复位撤销后的约五个时钟周期。

如图3-31所示,提供了复位期间FIFO行为的示例时序图。请注意,在这种配置下,上电(power-up)时的值与复位状态的值是不同的。

满标志复位值为0

在这个配置中,FIFO需要至少一个写/读时钟周期的异步复位脉冲(以较慢者为准)来完成适当的复位同步。在复位期间,full、almost_full和prog_full标志会被撤销(deasserted)。当FIFO退出复位同步状态后,它准备好进行写操作,这通常发生在异步复位断言后的约五个时钟周期。

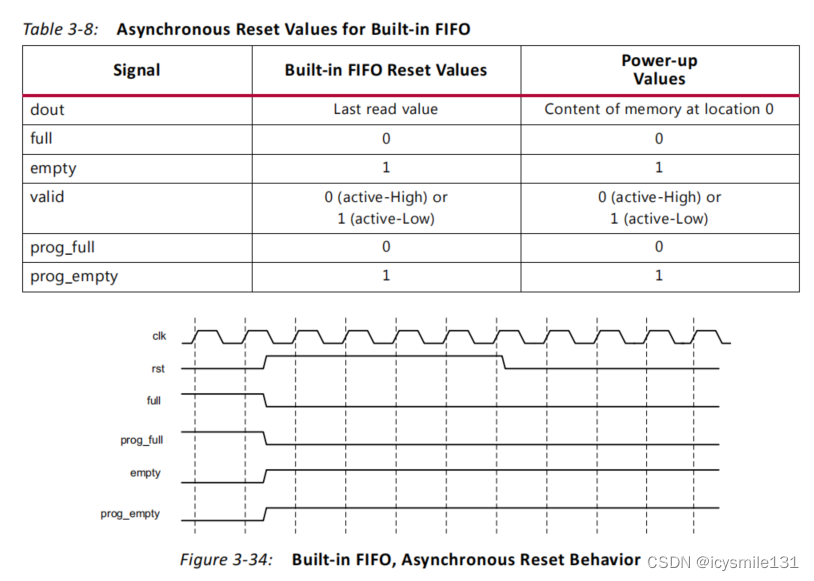

2 在7系列中内置FIFO的公共/独立时钟配置时

表3-8 定义了内置FIFO在电源上电和复位状态期间输出端口的值。dout复位值仅支持具有嵌入式寄存器选项的公共时钟内置FIFO。内置FIFO需要至少五个读和写时钟周期的异步复位脉冲。为了确保在所有内置FIFO配置中的一致性,建议为内置FIFO提供至少5个读和写时钟周期的异步复位脉冲。然而,FIFO生成器IP核具有一个内置机制,确保所有内置FIFO的复位脉冲至少持续五个读和写时钟周期。

在复位期间,rd_en(读使能)和wr_en(写使能)端口需要被撤销(即不允许进行读或写操作)。复位断言会导致full和prog_full标志撤销(即不指示FIFO已满或接近满),而empty和prog_empty标志置位(即指示FIFO为空或接近空)。当异步复位被释放后,IP核退出复位状态并准备好进行写操作。如图3-34所示。

FIFO(First-In, First-Out)的underflow(下溢)和overflow(上溢)信号的行为是依赖于读使能(rd_en)和写使能(wr_en)信号的。

Underflow(下溢)::当FIFO为空(即没有任何数据可读)时,如果读使能(rd_en)信号被断言(即设置为高电平或逻辑真),则FIFO的下溢信号会被触发(断言)。

Overflow(上溢):当FIFO已满(即没有空间写入新数据)时,如果写使能(wr_en)信号被断言(即设置为高电平或逻辑真),并且有一个写操作尝试将数据写入FIFO,则FIFO的上溢信号会被触发(断言)。

这篇关于FIFO Generate IP核使用——异步复位的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!