本文主要是介绍verilog中奇偶校验的代码实现,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

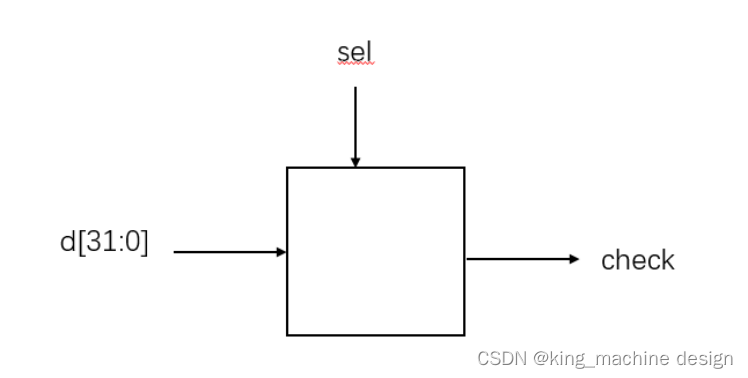

对输入的32位数据进行奇偶校验,根据sel输出校验结果(1输出奇校验,0输出偶校验)

信号示意图:

代码如下:

(CSDN代码块不支持Verilog,代码复制到notepad++编辑器中,语言选择Verilog,看得更清楚)

`timescale 1ns/1ns

module odd_sel(

input [31:0] bus,

input sel,

output check

);

//*************code***********//

assign check = sel ? (^bus) :~(^bus); //*************code***********//

endmodule这篇关于verilog中奇偶校验的代码实现的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!