本文主要是介绍stm32f103c8t6学习笔记(学习B站up江科大自化协)-PWR电源控制,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

PWR简介

·PVD可用在电池供电或安全要求比较高的设备,如果供电电压在逐渐下降,在电压过低的情况下可能会导致内外电路出现不确定的错误。为了避免不必要的错误,可以在电源电压过低的情况下,提前发出警告并关闭较为危险的设备

·PVD可用在电池供电或安全要求比较高的设备,如果供电电压在逐渐下降,在电压过低的情况下可能会导致内外电路出现不确定的错误。为了避免不必要的错误,可以在电源电压过低的情况下,提前发出警告并关闭较为危险的设备

·关闭的硬件越多越省电,不过唤醒就越麻烦

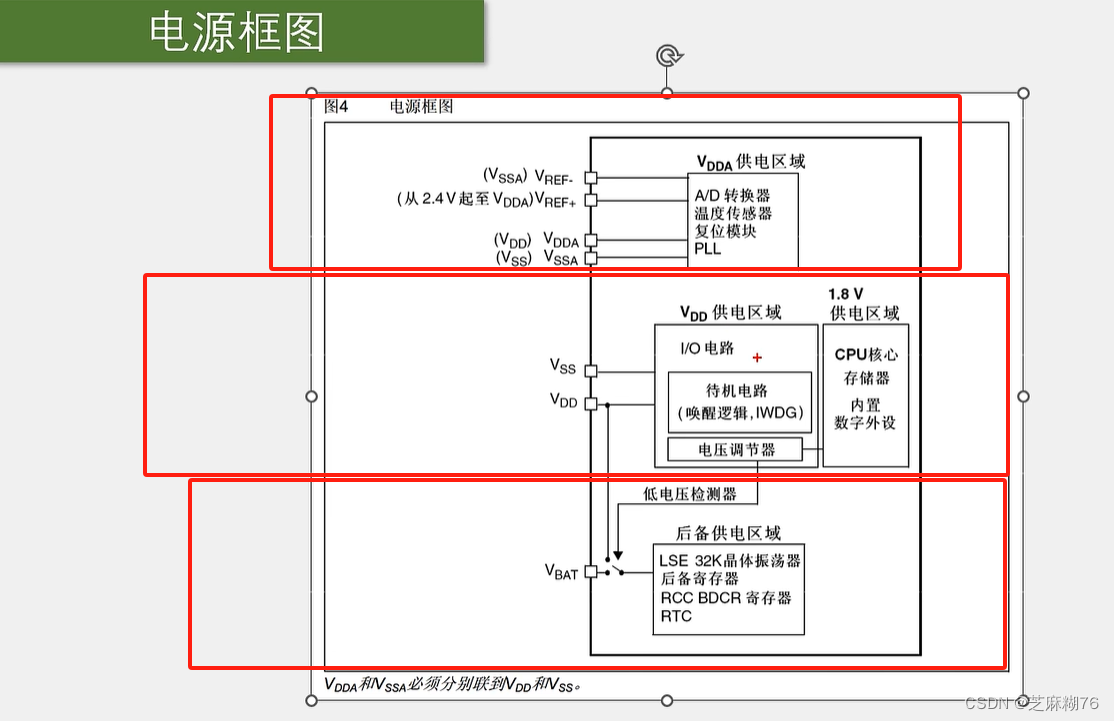

电源框图

可将STM32内部的供电方案大致分为3部分:

·第一部分(最上边的):模拟部分供电,VDDA(VDD Analog)

这部分电路供电的正极是VDDA,负极是VSSA,其中AD转换器还有两根参考电压的供电叫VREF+和VREF-,在引脚多的型号中会单独引出,在引脚少的设备(如c8t6)内部会接到VDDA和VSSA

·第二部分(中间的):数字部分供电,包括VDD供电区(左)和1.8V供电区(右)

VDD供电区域的电压调节器降压到1.8V之后,提供给后边的1.8V供电区。STM32内部的关键电路基本是以1.8V低压运行的,当这些电路需要与外界交流的时候才会通过IO转换成3.3V。其中使用低压运行的目的是降低功耗,电压越低内部电路运行的功耗就越低

·第三部分(最下边的):后备供电VBAT(V Battery)

RCC_BDCR是RCC寄存器,叫备份域控制寄存器,也是和后备区域有关的寄存器,可由VBAT供电。

第二三部分中间有一个低电压检测器可以控制VBAT开关,VDD有电的时候由VDD供电,VDD没电时由VBAT供电

上电复位和掉电复位

·当VDD或VDDA电压过低时,内部电路直接产生复位,让stm32复位住不会乱操作

·在复位和不复位的界限之间设置了一个40mV的迟滞电压,大于上限POR(Power On Reset)时解除复位,小于下限PDR(Power Down Reset)时复位,是一个典型的迟滞比较器。设置两个阈值的作用,是为了防止电压在某个阈值附近波动时造成输出也来回抖动,

·复位信号时低电平有效,在前边后边电压过低时是复位的,中间电压正常不复位。

·关于POR、PDR和滞后时间可以参考数据手册(如下)

下降沿PDR掉电复位的阈值下限典型值是1.88V,上升沿上电复位的阈值上限典型值是1.92V,1.92-1.88就是迟滞的阈值40mV。如果忽略迟滞的话,简单点说就是大于1.9上电,低于1.9掉电。

最后一行是复位持续时间,典型时间是2.5ms

可编程电压检测器

·简称PVD,也是用于检测VDD和VDDA的供电电压,和前边的区别在于PVD的阈值是可以程序指定的,可以自定义调节,根据手册,可选范围是2.2-2.9V左右,PVD上限和下限的迟滞电压是100mV,PVD的电压比上电掉电复位的电压高

·PVD触发后芯片还是能正常工作的,只不过是电源电压过低,可以对用户进行提醒。PVD的输出是正逻辑,电压过低时为1,电压正常时为0,这个信号可以去申请中断,在上升沿或下降沿时触发中断,PVD的中断申请是通过外部中断实现的,如果要使用PVD的话需要记得配置外部中断

·接到外部中断的还有RTC,RTC自己是由中断的,但是为什么还需要接到外部中断?由于低功耗模式设计的是只有外部中断可以唤醒停止模式,其他设备(USB、ETH等等,将其wakeup信号线接过来)也想唤醒停止模式的话都可以通过借道外部中断实现

低功耗模式

·在这个图中,从上到下的模式关闭的电路越来越多,也越来省电,也是越来越难唤醒

·关闭电路通常由两个做法,一个是关闭时钟,另一个是关闭电源,

关闭时钟所有的运算和涉及时序的操作都会暂停,但是寄存器和存储器里保存的数据还可以维持不会丢失

关闭电源就是电路直接断电,电路的操作和数据都会直接丢失,关闭电源会比关闭时钟更省电。图中电压调节器关就代表1.8V区域断电

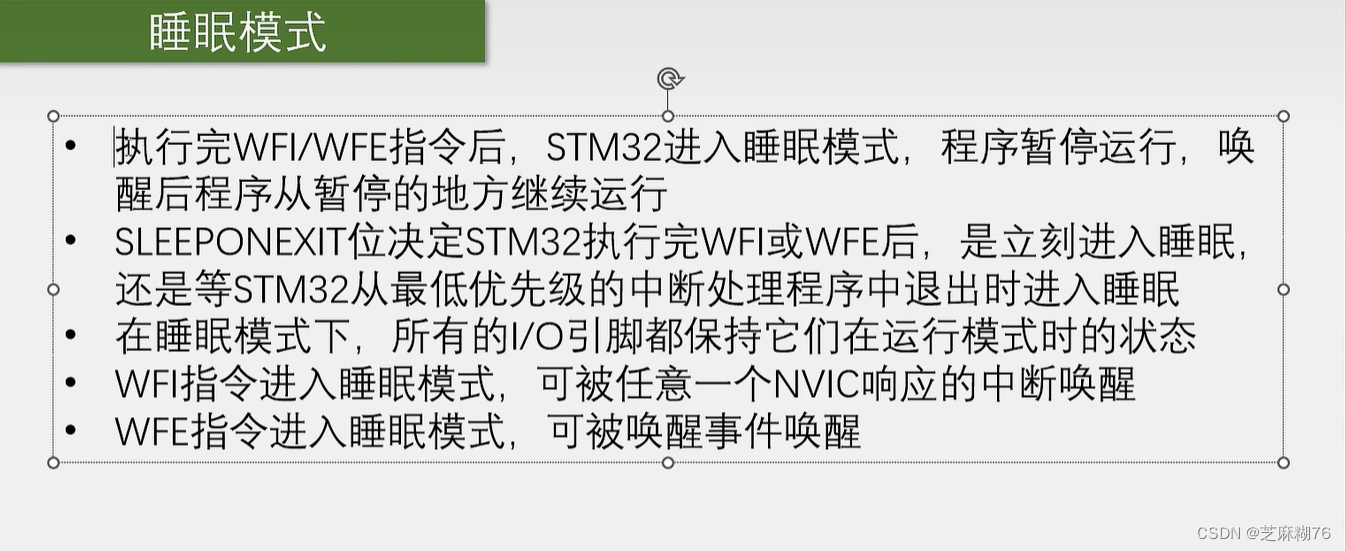

睡眠模式:

·直接调用WFI或WFE即可进入,这两个是内核的指令,使用可以直接调用库函数,WFI(Wait For Interrupt等待中断),唤醒条件是任意中断,仍和外设发生任何中断时芯片都会立刻醒来,醒来一般第一时间处理中断函数。WFE(Wait For Event等待事件),这个事件可以是外部中断配置为事件模式,也可以是使能了中断但是没有配置NVIC,WFE唤醒醒来之后一般不需要进中断函数,直接从睡的地方继续运行

·睡眠模式对只讲CPU时钟关闭,程序不会继续运行,CPU不运行功耗就会降低,睡眠模式对其他电路没有任何操作

·一般可以在主循环的最后执行WFI、WFE,主循环执行一遍就睡眠,唤醒之后主循环会再执行一遍再睡眠,每唤醒一次主循环执行一遍

·如果在程序中执行点灯,灯点亮了进入睡眠,灯任然是亮的,GPIO引脚的电平在睡眠时是维持原样的

·唤醒事件可通过下述方式产生:

·在外设控制寄存器中使能一个中断,不在NVIC中使能,并且在内核的控制寄存器中SEVONPEND(Send Event On Pend)位,才能产生唤醒事件,在唤醒后要及时清除挂起位

·配置EXTI为事件模式

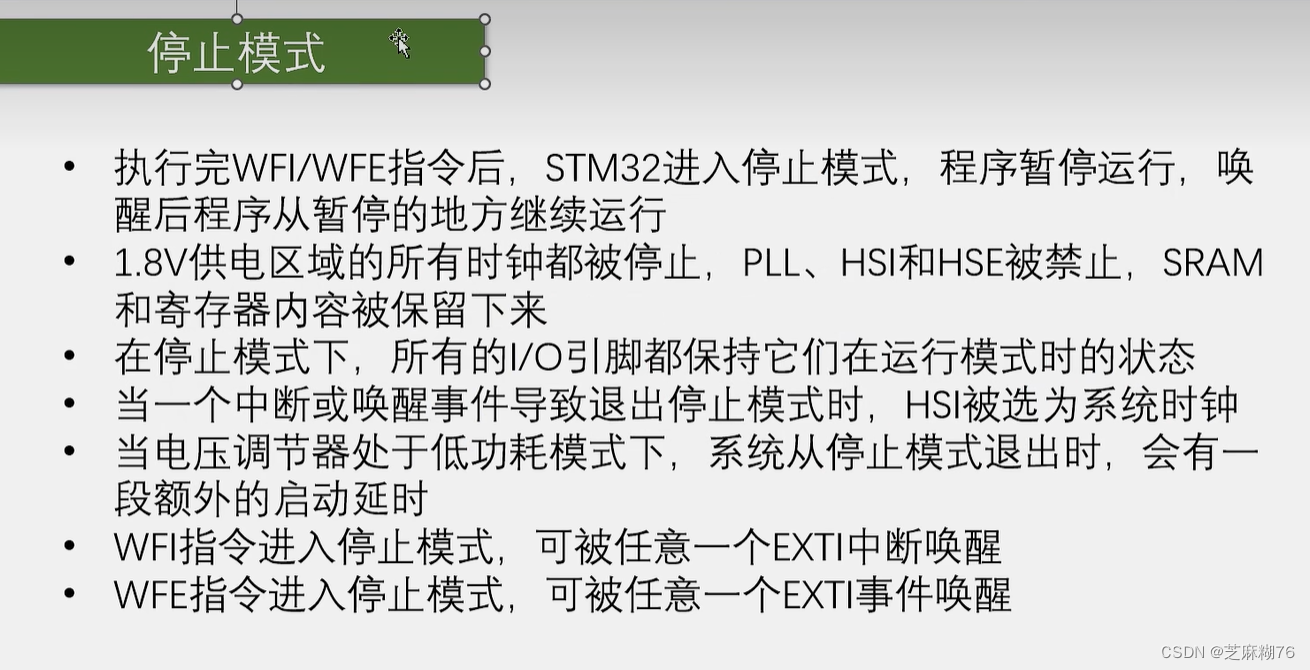

停机模式:

·进入停机模式,先将SLEEPDEEP位置1,告诉CPU可以方向进入深度睡眠模式,

PDDS这一位是用于区分是停机模式还是待机模式,PDDS = 0进入停机模式,PDDS = 1进入待机模式。要想进入停机模式要现将PDDS设置为0,

LPDS用于设置最后的电压调节器是开启还是进入低功耗模式,LPDS = 1电压调节进入低功耗,LPDS = 0电压调节器开启。当把前边提到的位设置好了之后,再调用WFI或WFE芯片就可以进入停止模式了。

停止模式的唤醒条件较为苛刻,因为在这个模式下芯片睡眠更深,关闭的东西更多。条件是任一外部中断,所有外设的中断都可以,以及前边提到的PVD、RTC闹钟、USB唤醒、ETH唤醒借道了外部中断,这四个信号也同样可以唤醒停止模式。

停止模式对电路的操作有:关闭所有1.8V区的时钟,不仅CPU不能运行,外设也运行不了,正在定时的定时器会暂停,串口收发数据也会暂停,由于没关闭电源,CPU和外设的寄存器数据都是维持原状的。HSI和HSE的振荡器关闭,CPU和外设时钟都关闭的情况下,这两个高速时钟也没什么作用,所以会关闭。LSI内部低速时钟和LSE外部低速时钟并不会主动关闭,如果开启过这两个时钟可以继续运行。

电压调节器可以开启或者选择低功耗模式,这个电压调节器是由LPDS位控制的,无论电压调节器是开启还是低功耗,都可以维持1.8V区域寄存器和存储器的数据内容,区别在于低功耗更省电,同时低功耗在唤醒时会花更多的时间,电压调节器开启的话更耗电一些但是唤醒更快

·睡眠模式和停止模式寄存器的内容都可以维持,唤醒后程序可以在暂停的地方继续运行

·高低电平维持暂停前一刻的状态

·程序默认在system_Init里的配置,是使用HSE外部高速时钟,通过PLL倍频得到72MHz主频,但是进入停止模式之后PLL和HSE都停止了,并且在退出停止模式的时候并不会自动帮我们再开启PLL和HSE,而是默认用HSI的8MHz作为主频,如果忽略这个问题会出现一个现象:程序刚上电的时候主频是72MHz,但是进入停止模式再唤醒的时候就变成8MHz的主频。在停止模式的唤醒之后第一时间就是重新启动HSE,配置主频为72MHz,只需调用System_Init即可

·电压调节器低功耗更省电,但是停止模式退出时会有一段额外的启动延时。

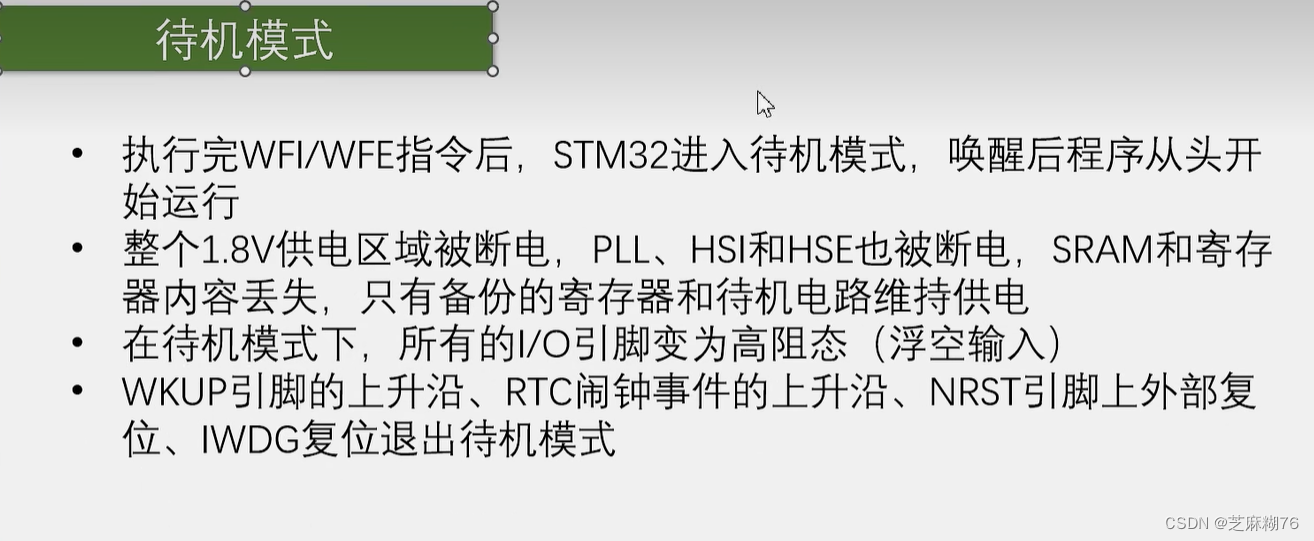

待机模式:

待机模式和停机模式类似,SLEEPDEEP置1,即将深度睡眠,PDDS置1表示即将进入待机模式,最后调用WFI或WFE就可以进入待机模式了。

唤醒条件更为严格,普通外设的中断和外部中断都无法唤醒待机模式,只有指定的几个信号可以唤醒:

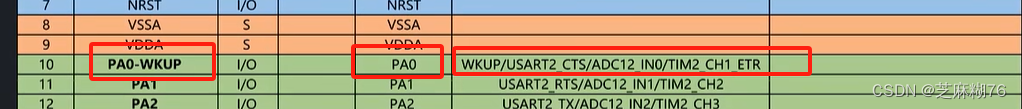

·WKUP引脚的上升沿,在引脚定义表里边可以看到WKUP的引脚位置在PA0

·RTC闹钟事件,RTC闹钟可以唤醒待机模式,应用场景是芯片每隔一段时间工作一次

·RTC闹钟事件,RTC闹钟可以唤醒待机模式,应用场景是芯片每隔一段时间工作一次

·NRST引脚上的外部复位,意思是按下复位键也可以唤醒

·IWDG独立看门狗复位

待机模式对电路的操作:基本将能关的都关了,1.8V区域的时钟关闭,两个高速时钟关闭,电压调节器关闭,意味着1.8V区域的电源关闭,那么内部的存储器和寄存器数据全部丢失。同停止模式一样,并没有主动关闭LSI和LSE的低速时钟,因为这两个时钟需要维持RTC和独立看门狗的运行,所以不会关闭

·待机模式下唤醒,程序从头开始运行,因为待机模式把大部分电路的电源都断了,数据丢失,唤醒后程序无法继续运行,只能从头开始

·浮空输入对于输出而言,就是高阻态,假如提前点了灯,在进入待机模式之后无论这个灯市高电平点亮还是低电平点亮都会熄灭,GPIO对外不输出高低电平,也不流过电流

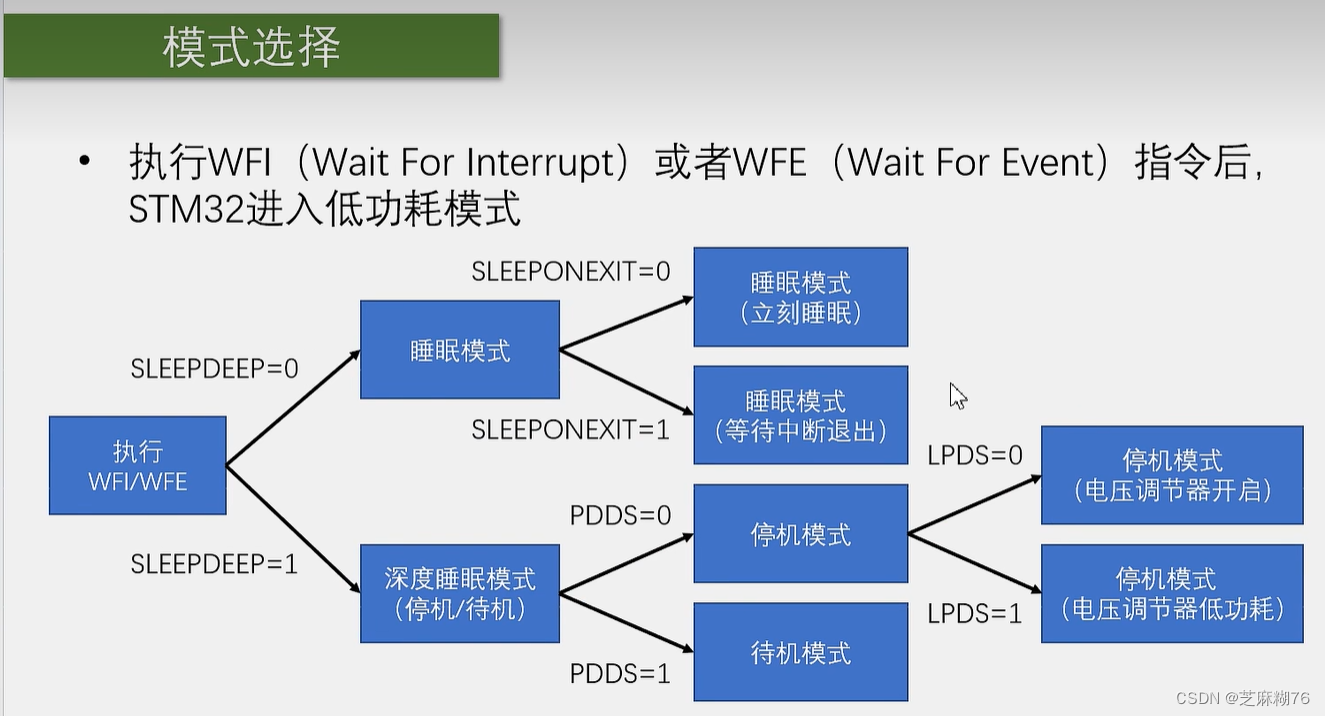

模式选择:

·执行WFI和WFE指令后,STM32进入低功耗模式,也就是说这两个指令时开启低功耗的触发条件,配置其他的寄存器都需要在这两个指令之前。

·一旦WFI或WFE执行了,芯片要想知道进入哪种低功耗模式,会按这个流程图进行判断:

·首先看SLEEPDEEP位是1还是0,如果SLEEPDEEP位是0就是浅睡眠,对应睡眠模式,是1表示进入深度睡眠模式,对应停机或待机模式,

·在普通睡眠模式下,SLEEPONEXIT位 = 0 时,无论程序在哪里调用WFI/WFE,都会立刻进入睡眠,SLEEPONEXIT = 1时,执行WFI/WFE之后会等待中断退出,等待所有中断完成之后才进入睡眠。

如果不在中断函数中调用WFI、WFE,实际上这两个功能的效果是一样的。可以将WFI、WFE放在主程序之中,主程序执行到的时候也代表中断处理完成了。如果想在中断函数中调用WFI、WFE,并且想中断结束后才睡眠,才需考虑(等待中断退出)这个模式

·进入深度睡眠模式,会继续判断PDDS这一位,如果PDDS = 0则进入停机模式,如果PDDS = 1则进入待机模式。

在停机模式下会继续判断LPDS位,如果LPDS = 0,就是停机模式且电压调节器开启,LPDS = 1就是停机模式且电压调节器低功耗,电压调节器低功耗的特性是更省电,但是唤醒延迟更高

功能实现部分:

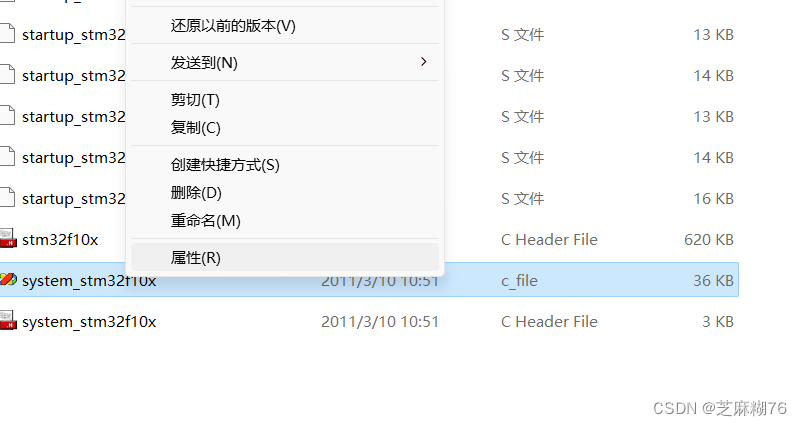

·实现功能前需要注意:如果文件图标带有钥匙标志,说明文件为只读,必须先解除只读才能修改程序

·解除只读的方法为:文件夹里找到文件 --> 文件 --> 右键 --> 取消只读

或者右键点击这个文件Open Contaning Folder直接跳转到文件所在的文件夹

进入文件夹之后点击属性

将只读的勾去掉,然后回到keil里边看这个文件,可以发现小钥匙消失,意味着可以进入编辑状态

·芯片再三种低功耗的情况下是没办法下载程序的,下载成功后开始执行程序,芯片进入休眠时再次点击下载会报错。解决方法是:按住复位键不放,点击下载按钮并及时松开复位键。在低功耗情况下都需要以这种方式下载

·如果不小心禁用了调试端口,也可以按上边这个方法解决

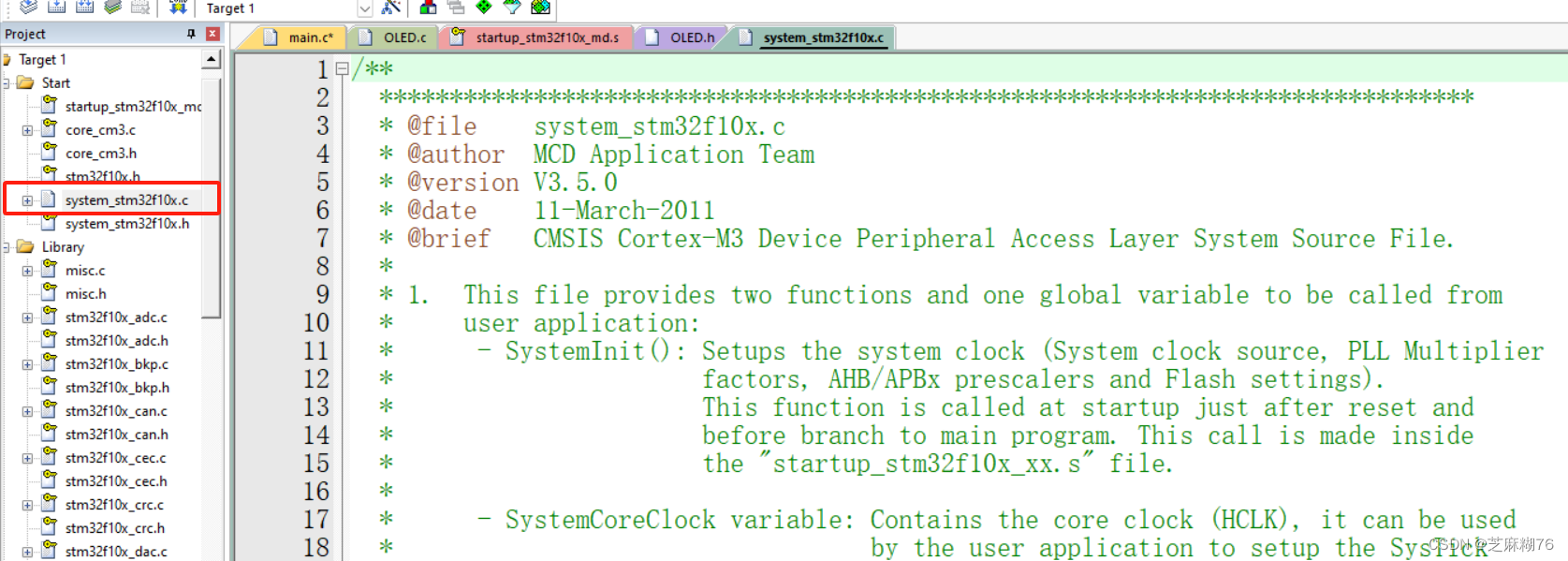

修改主频

·修改主频不属于三种低功耗模式,但是是可以降低STM32的功耗的方法之一。

·这段代码第一行显示系统主频,第二行以1秒为周期闪烁running,由于正常系统主频是72MHz,但是降频为36MHz之后,运行时间变为原来的二倍

·修改主频在system_stm32f10x.c里边的文件里110行的位置配置时钟,将预留好的宏定义解除注释即可

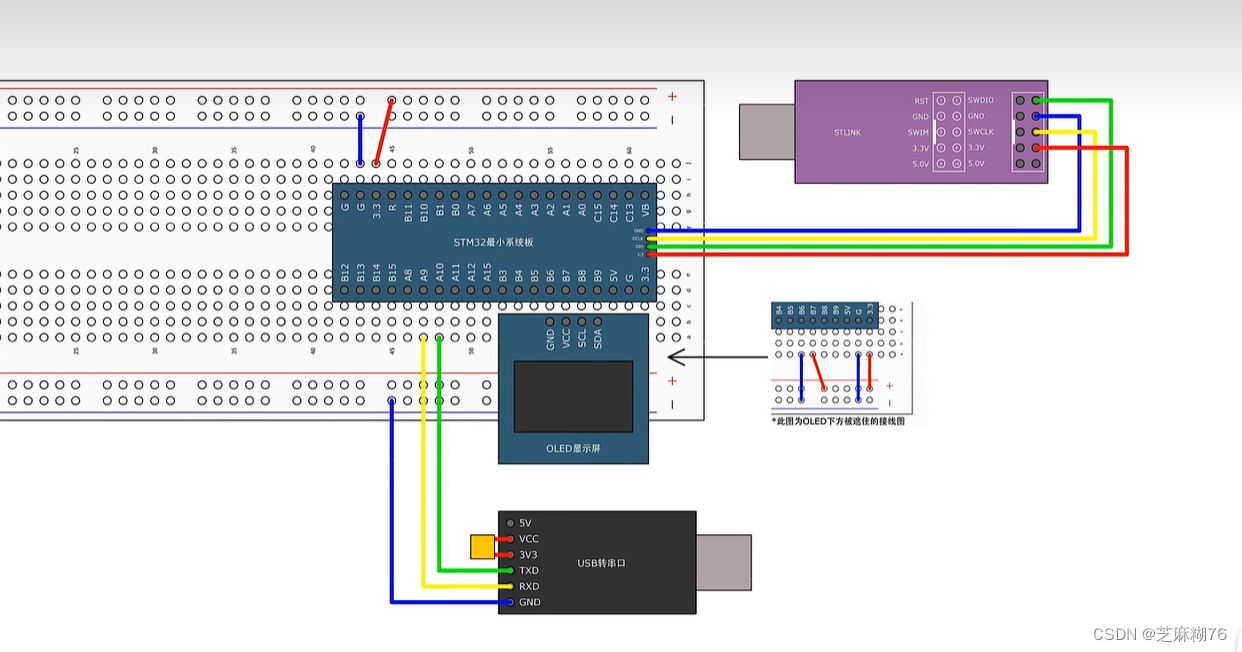

接线图

·

睡眠模式+串口发送+接收

·当收到一个字节的时候,中断触发,置标志位。主循环查询到标志位的时候,读取数据并用串口发送出去。收到数据后自动退出睡眠模式,执行一遍任务之后继续睡眠,空闲时芯片持续处于睡眠状态,降低系统功耗

·连接好串口后发送数据,发送数据给stm32,stm32成功接受数据并回传,现象和没使用睡眠模式的时候是一样的,区别的细节在于只有发送数据的时候,OLED才会显示一次running,空闲时芯片都在睡眠。

接线图

停止模式+对射式红外传感期计次

·每遮挡一次,执行一次计次,也显示一次running,没有外部中断信号时,stm32处于休眠模式省点,

接线图

待机模式+实时时钟

·LSE外部低速时钟,如果没有RTC晶振或RTC晶振不起振,LSI在待机模式下也可以继续工作

·在进入待机模式之前,关闭外部链接的各个模块,以最大化省电。每隔10s唤醒一次,唤醒后执行一次任务后继续待机,

接线图

这篇关于stm32f103c8t6学习笔记(学习B站up江科大自化协)-PWR电源控制的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!