本文主要是介绍用FPGA+DAC输出“心”形波,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1.前言

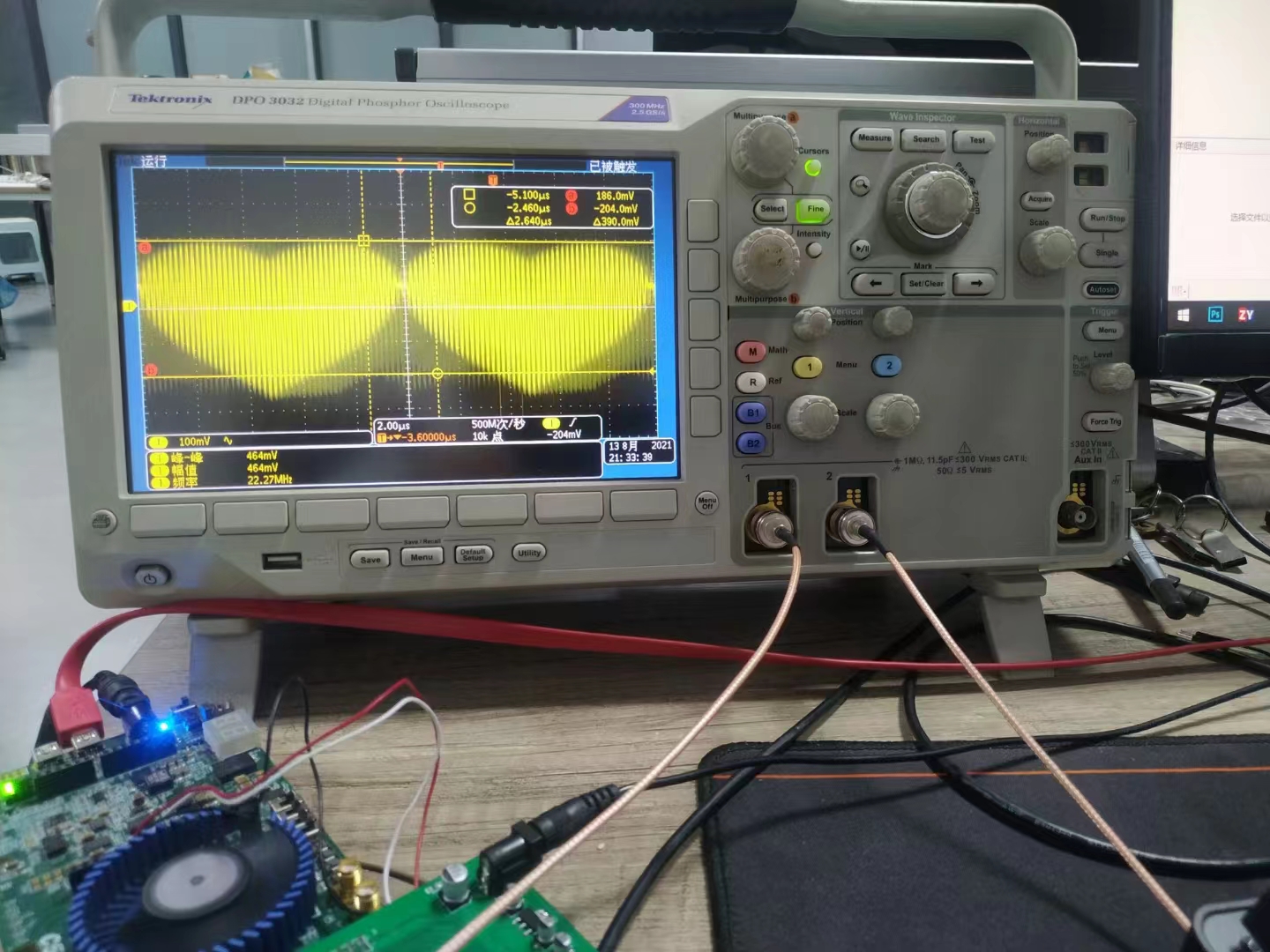

之前在做信号处理的时候整了一下活,用FPGA+DAC(数模转换器),输出了一个爱心形状的波形,今天整理资料的时候偶然发现了他,现在把他分享出来。当时将DAC的输出接在示波器上显示如下图所示:

2.原理

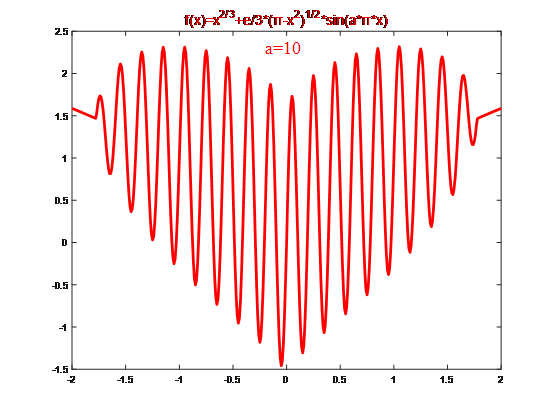

爱心波形的函数表达式如下:

f ( x ) = x 2 3 + 1 3 e ( π − x 2 ) 1 2 sin ( a π x ) f(x)=x^\frac{2}{3} + \frac{1}{3}e(\pi-x^2)^\frac{1}{2}\sin(a\pi x) f(x)=x32+31e(π−x2)21sin(aπx)

其中,e为自然对数,a为参数 π \pi π为圆周率。首先在Matlab当中,画出上述函数的波形,不断调整a的值,使其更逼近我们想要的“爱心”形状。经过试验,作者觉得 a = 10 a=10 a=10时比较像,图像如下:

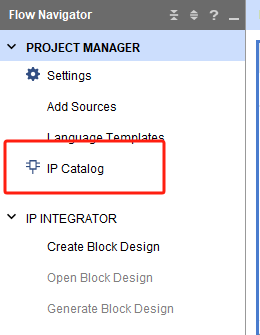

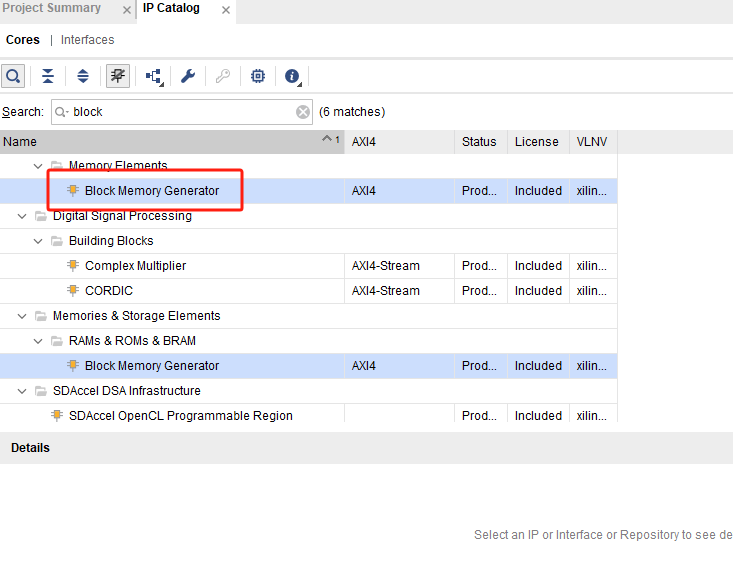

然后将图像进行采样和量化,存为coe文件,导入到FPGA的ROM中:

(1)打开IP Catalog:

(2)IP核选择Block Memory Generator:

(3)选择Single Port ROM,即单口ROM:

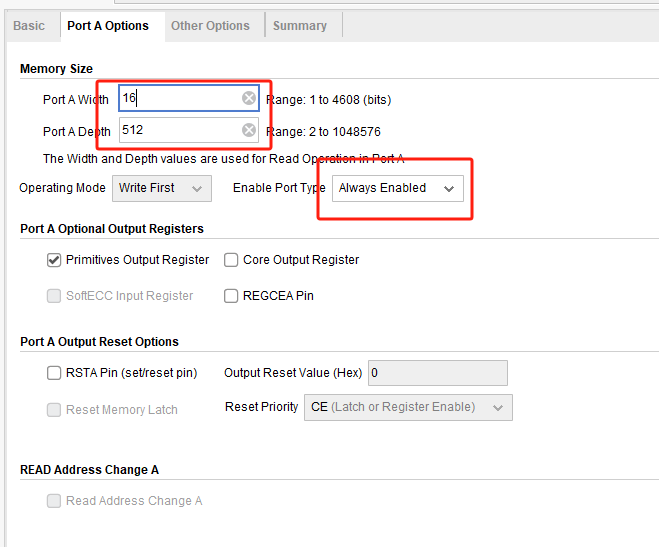

(4)修改位宽和深度与coe文件保持一致,选择端口始终使能:

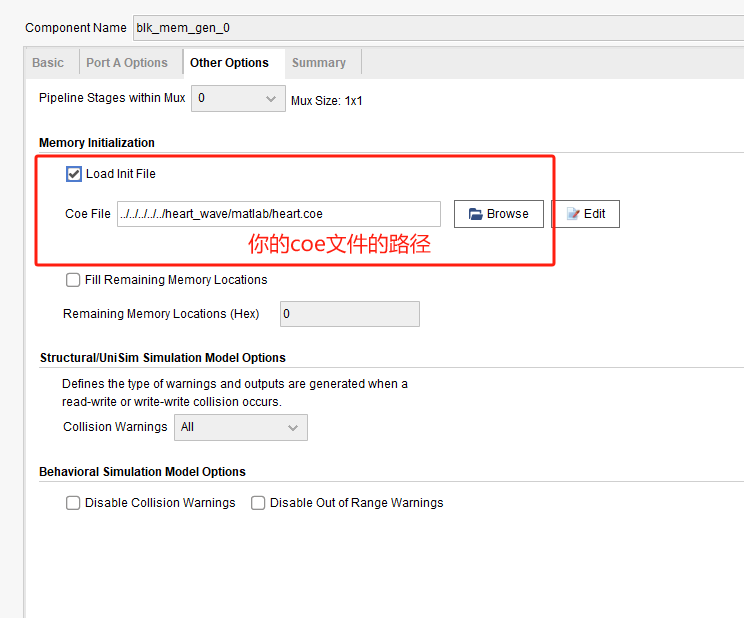

(5)添加coe文件:

IP配置核配置完成点击确定即可。仿真效果如下:

3.DAC

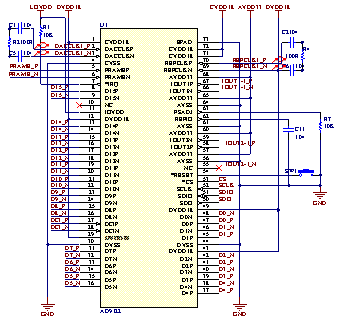

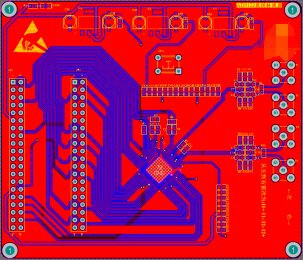

当时我使用的是ADI的AD9122进行输出,下面讲一下AD9122的电路设计:

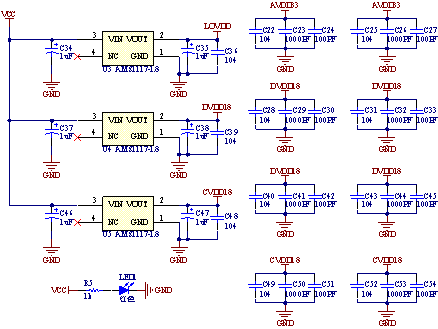

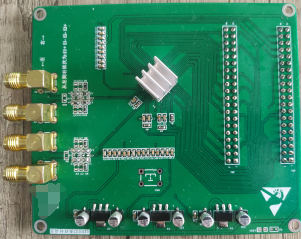

3.1电源

单板的供电方式是通过一个DC-DC的电源接头输入一个5.0V的直流电压,经过一个大电容滤波后,再分别由相应的电源芯片降压,产生AVDD33(3.3V)、DVDD18((1.8V)、CVDD18(1.8V)、LOVDD(1.8V),这些电源在经过滤波后给相应部件供电。

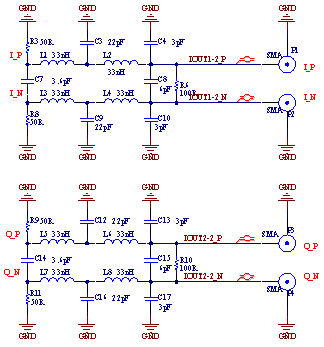

3.2低通滤波器

为了保证输出波形更平滑,需要在输出端口接一个低通滤波器。这里采用五阶巴特沃斯低通滤波器,其转折频率为300MHz。

3.3 AD9122

3.4 通过串行端口SPI配置AD9122功能寄存器

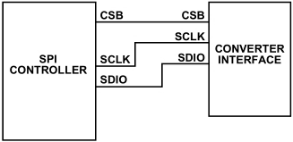

3.4.1 SPI协议简述

SPI端口由三个引脚组成:串行时钟引脚(SCLK)、串行数据输入/输出引脚(SDIO)和片选引脚(CSB),这被称为三线模式。一些芯片把串行数据输出引脚(SDO)作为可选引脚,如果包含它,它仅用于从设备读取数据,一般地,为了减少引脚数量,大多数芯片都省略了这个引脚。

(1)串行时钟(SCLK):SCLK用于同步串行接口读取和写入。输入数据记录在该时钟的上升沿,输出数据传输记录在下降沿。

(2)串行数据输入/输出(SDIO):SDIO引脚是一个双重用途的引脚。这个引脚可作为是输入或输出,具体取决于发送的指令(读或写)在时序帧中的相对位置(指令或数据相位)。在写或读的第一阶段,这个引脚作为输入传递信息到内部状态机。如果确定该命令为读命令,状态机将此引脚(SDIO)更改为输出,然后将数据传回控制器。如果设备包含一个SDO引脚,并且配置寄存器使能,那么SDO将变为串行数据输出端口,而SDIO只作为串行数据输入端口。

(3)片选信号(CSB):CSB是一个有效的低电平控制,用于控制读写周期。当该线路为低电平时,将选择该设备,并处理SCLK和SDIO线路上的信息。如果此引脚为高电平,器件会忽略SCLK和SDIO线路上的任何信息。通过这种方式,多个设备可以连接到SPI端口。如果只连接了一个器件,可以选择将CSB线拉低,使该器件永久有效。

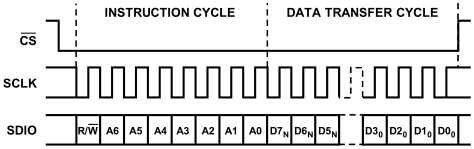

3.4.2 AD9122串行端口操作

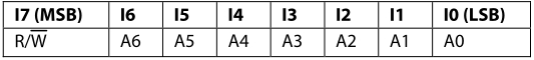

当CS引脚上的电平由逻辑高电平到逻辑低电平,串行端口时序将复位至指令周期的初始状态。从这个状态开始,接下来的前八个SCLK上升沿代表当前输入输出操作的指令位,后八个SCLK上升沿进行数据的传输。也就是说,控制器与AD9122的通信周期分为两个阶段:阶段1是指令周期(将指令字节写入器件),与前八个SCLK上升沿一致,指令字节定义了即将到来的数据传输是读还是写,以及数据传输第一个字节的起始寄存器地址;通信周期的第2阶段是指令字节向串行端口控制器提供有关数据传输周期的信息,向寄存器写入数据,改变寄存器的值,来配置自己所需要的功能,或者对寄存器的值进行访问,以判断器件此刻的工作状态。

指令字节的第7位,决定了在指令字节写入后是进行读数据传输还是写数据传输。逻辑1表示读操作,逻辑0表示写操作。A6至A0是指令字节的位6至位0,决定在通信周期的数据传输部分访问的寄存器的地址。

ADI的数模转换器(DAC)和模数转换器(ADC)使用起来都差别不大,基本都可以使用SPI去读写其寄存器。我这里用的是AD9122,你搞明白了,只要会看datasheet也能很快上手。

代码

获取代码和工程请点此链接

这篇关于用FPGA+DAC输出“心”形波的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!