本文主要是介绍【DSP系列】TMS320F28335——ADC采集,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

1.AD转换原理介绍

1.1ADC转换步骤

1.2ADC转换原理

1.3ADC核心指标

2.F28335 ADC介绍

2.1排序器的工作原理

(1)级联操作方式

①级联排序器顺序采样模式

②级联排序器同步采样模式

(2)双排序操作方式

①双排序器顺序采样模式

②双排序器同步采样模式

(3)排序器启动/停止模式

(4)输入触发源

(5)排序器转换的中断操作

(6)排序器覆盖功能

2.2ADC时钟控制

本文基于普中科技开发手册,进行学习记录,并且修正开发手册中的一些错误。经实践验证,以我为准。

1.AD转换原理介绍

1.1ADC转换步骤

AD 转换器(ADC)将模拟量转换为数字量通常要经过 4 个步骤:采样、保持、量化和编码。如下图所示:

将采样结果存储起来,直到下次采样,这个过程叫做保持。将采样电平归化为与之接近的离散数字电平,这个过程叫做量化。将量化后的结果按照一定数制形式表示就是编码。将采样电平(模拟值)转换为数字值时,主要有两类方法:直接比较型与间接比较型。

--直接比较型:就是将输入模拟信号直接与标准的参考电压比较,从而得到数字量。常见的有并行 ADC 和逐次比较型 ADC。

--间接比较型:输入模拟量不是直接与参考电压比较,而是将二者变为中间的某种物理量在进行比较,然后将比较所得的结果进行数字编码。常见的有双积分型 ADC。

1.2ADC转换原理

以常用的逐次逼近型ADC为例,介绍其工作原理。双积分型ADC不常用,如若需要自行查阅资料,这里不进行介绍。

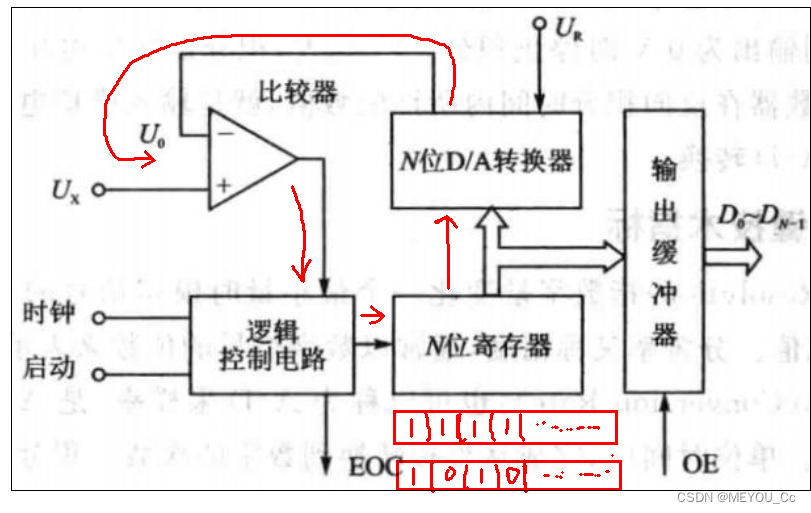

采用逐次逼近法的 AD 转换器是有一个比较器、DA 转换器、缓冲寄存器和控制逻辑电路组成,如下图所示:

基本原理是:从高位到低位逐次试探比较,就像用天平秤物体,从重到轻逐级增减砝码进行试探。逐次逼近法的转换过程是:初始化时将逐次逼近寄存器各位清零,转换开始时,先将逐次逼近寄存器最高位置 1,送入 DA 转换器,经 DA转换后生成的模拟量送入比较器,称为 U0,与送入比较器的待转换的模拟量 Ux进行比较,若 U0<Ux,该位 1 被保留,否则被清除。然后再将逐次逼近寄存器次高位置 1,将寄存器中新的数字量送 DA 转换器,输出的 U0 再与 Ux 比较,U0<Ux,该位1 被保留,否则被清除。重复此过程,直至逼近寄存器最低位。转换结束后,将逐次逼近寄存器中的数字量送入缓冲寄存器,得到数字量的输出。逐次逼近的操作过程是在一个控制电路的控制下进行的。

什么意思呢?如下图:

假如图中的N=12,12位寄存器中,先向最高位写1,然后送入到12位D/A转换器中生成模拟电压U0,然后这个U0和输入电压Ux进行比较, 若 U0<Ux,则12位寄存器中该位 1 就被保留,否则被清除。依次,次高位写1,再次送入到12位D/A转换器中生成模拟电压U0,然后这个U0和输入电压Ux进行比较,确定该位的1是否保留下来,最后确定12位数字量,输出到输出缓冲器中,因此完成了模拟电压到数字量的采集。这就逐次逼近型ADC。

1.3ADC核心指标

(1)分辨率

分辨率指数字量变化一个最小量时模拟信号的变化量,定义为满刻度与 2^n的比值。分辨率又叫做精度,通常以数字信号的位数来表示。

eg:12位ADC,若Vref=3V,最小分辨电压=3*(1/2^12)V

(2)转换速率

转换速率也叫做采样率,是 AD 转换一次所需要时间的倒数。单位时间内,完成从模拟转换到数字的次数。积分型 AD 的转换时间是毫秒级属低速 AD,逐次比较型 AD 是微妙级属于中速 AD,全并行/串并行型 AD 可达到纳秒级。采样时间则是另外一个概念,是指两次转换的间隔。为了保证转换正确完成,采样速率(Sample Rate)必须小于或等于转换速率。因此有人习惯上将转换速率在数值上等同于采样速率也是可以接受的。常用单位是 ksps 和 Msps,表示每秒采样千/百万次(kilo/Million Samples per Second)。

以上两个指标比较重要,其它的了解。

(3)量化误差

由于 AD 的有限分辨率而引起的误差,即有限分辨率 AD 的阶梯状态转移特性曲线与无限分辨率 AD(理想 AD)的转移特性曲线(直线)之间的最大偏差。通常是 1 个或半个最小数字量的模拟变化量,表示 1LSB、1/2LSB。

(4)偏移误差

输入信号为零时,输出信号不为零的值,可外接电位器调至最小。

(5)满刻度误差

满刻度输出时对应的输入信号与理想输入信号值之差。

(6)线性度

实际转换器的转移函数与理想直线的最大偏移,不包括以上 3 种误差。其他指标还有:绝对精度,相对精度,微分非线性等。

2.F28335 ADC介绍

F28335 片内集成的 ADC 转换模块的核心资源是一个 12 位的模数转换器,这个精度已经能够满足大多数测量需要,如果需要用到更高精度的 AD,比如 16 位或者 24 位的,就需要外扩高精度的AD 芯片。

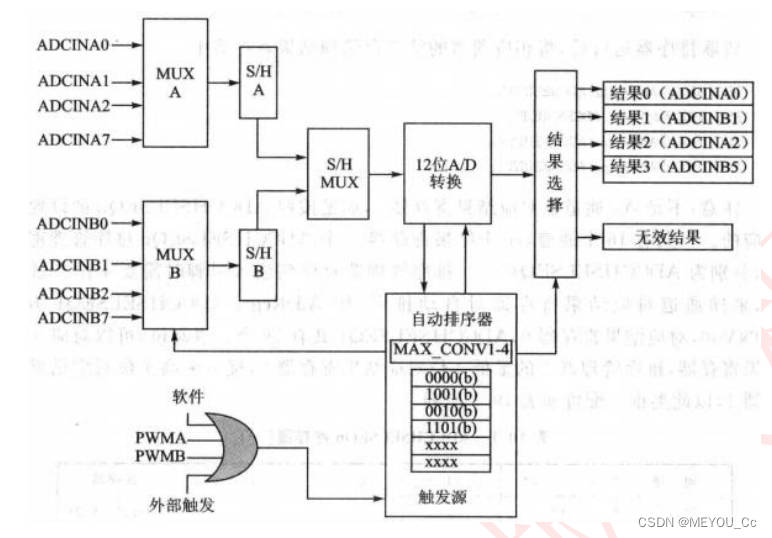

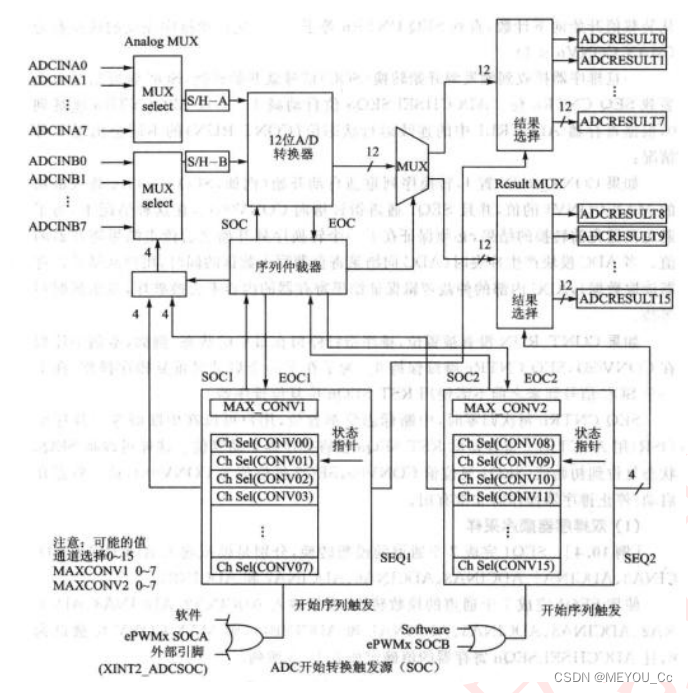

F28335 ADC 转换模块具有 16 个通道,由 2 个独立的 8 通道模块组成,这两个独立的 8 通道模块也可以级联成一个 16 通道模块。尽管 AD 转换器中有多个输入通道和两个序列发生器,但只有一个转换器。AD 转换器模块的内部结构如下图所示:

两个 8 通道模块能够自动排序构成一系列转换器,每个模块可以通过模拟的多路开(MUX)选择 8 个通道中的任何一个通道。在级联模式下,自动序列发生器是 16 通道的。对每一个序列发生器而言,一旦完成转换,所选通道的转换值将存储到相应的 ADCRESULT 寄存器中。自动排序过程允许系统对同一个通道进行多次变换,允许用户进行过采样算法从而得到比一般的单采样更精确的结果。

F28335 的 ADC 模块主要包括以下特点:

--12 位模数转换

--2 个采样保持器(S/H)

--同步或顺序采样

--模拟电压输入范围 0-3V

--ADC 转换时钟频率最高可配置为 25MHz,采样带宽 12.5MHz,也就是说,你采样的信号频率不能大于12.5MHz,这叫做带宽

--16 通道模拟输入

--排序器支持 16 通道独立循环“自动转换”,每次转换通道可以软件编程选择

--16 个结果寄存器存放 ADC 转换的结果,转换后的数字量表示为:

数字值=4096*输入模拟值/3,输入模拟值在 0-3V 之间

--多个触发源启动 ADC 转换(SOC):

①S/W--软件立即启动

②外部引脚

③ePWMx SOCA 启动

④ePWMx SOCB 启动

--灵活的中断控制,允许每个或者每隔一个序列转换结束产生中断请求

--排序器可工作在启动/停止模式

--采样保持(S/H)采集时间窗口有独立的预定标控制

在使用 ADC 转换模块时,特别要注意的是 F28335 的 AD 的输入范围 0-3V,若输入负电压或高于 3V 的电压就会烧坏 AD 模块,这一点要务必引起重视。超出输入范围的电压可在前级电路,通过电阻进行分压,或经运放比例电路进行处理后再输入。连接到 ADCINxx 引脚的模拟输入信号要尽可能的远离数字电路信号线,ADC 模块的电源供电要与数字电源电源隔离开,避免数字电源的高频干扰,ADC的参考源是影响 AD 精度的一个重要因数,注意 ADC 参考源的电压纹波处理。

2.1排序器的工作原理

F28335 的 ADC 转换模块有 2 个独立的 8 状态排序器(SEQ1 与 SEQ2),这两个排序器还可以级联为 1 个 16 状态的排序器(SEQ)。这里的状态是指排序器内能够完成的 AD 自动转换通道的个数。8 状态排序器指的是能够完成 8 个 AD 转换通道的排序管理。

2 个排序器可有两种操作方式,分别为单排序器方式(级联为1 个 16 状态排序器,即级联方式)和双排序器方式(2 个独立的 8 状态排序器)。AD 转换模块每次收到触发源开始转换的请求时,就能够通过排序器自动完成多路转换,将模拟输入信号引入采样保持器与 ADC 内核。转换完成后,将转换结果存入结果寄存器。

两种操作方式的最大差别就在于,单排序操作方式(级联方式)响应触发源是唯一的,可双排序的方式可以分别响应各自的触发源。单排序操作方式简单,双排序操作方式复杂。两种操作方式都可以进行顺序采样或者同步采样,两种采样最大的不同在于,顺序采样相当于串行模式,同步采样相当于并行模式,能保证信号的同时性,显然同步采样的要求高一些,两个采样保持器,决定了最多能够进行 2 路同步,在这电气常用控制中,跟 PWM 控制结合起来很有用,但超过 2 路同步就无能为力了。采样的时候可以多次采样,然后取平均值,以获得比单采样方式更精确的结果。

也就是说F28335芯片的ADC模块,有两个排序器,这两个排序器可以连起来当作一整个排序器使用叫做级联方式,也可以两个独立工作叫做双排序器方式。不管级不级联,ADC的采样都有两种采样:顺序采样和同步采样。

(1)级联操作方式

排序器级联方式内部结构图如下:

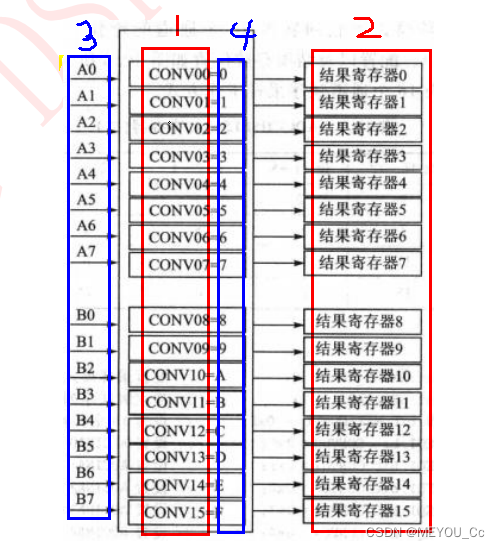

启动 ADC 之前,要进行一些初始化的工作。初始化转换的最多通道数(MAX_CONV),这个参数限制了最多有效通道数,对于级联模式,最大为 16,在双排序方式下,最大为 8。假如输入信号为 6,设置值为 4,实际只有 4 个输入有效通道。配置需要的转换输入信号对应的转换次序(CHSELxx),最终的转换结果存放在各自的结果寄存器(RESULT0-RESULT15),结果寄存器不与输入通道完全对应,而是结果寄存器与转换次序对应(这个一定要理解了)。对应程序更好理解。首先要知道ADC通道的控制数是怎么回事:

| ADC通道 | 控制数 | ADC通道 | 控制数 |

| ADCINA0 | 0x0 | ADCINB0 | 0x8 |

| ADCINA1 | 0x1 | ADCINB1 | 0x9 |

| ADCINA2 | 0x2 | ADCINB2 | 0xa |

| ADCINA3 | 0x3 | ADCINB3 | 0xb |

| ADCINA4 | 0x4 | ADCINB4 | 0xc |

| ADCINA5 | 0x5 | ADCINB5 | 0xd |

| ADCINA6 | 0x6 | ADCINB6 | 0xe |

| ADCINA7 | 0x7 | ADCINB7 | 0xf |

16个通道对应结果寄存器如下(这里是一 一对应的,可以不一 一对应):

对上图进行说明:框图1和2是一 一对应的,比如CONV00(向该位写 ADC控制数 表示该控制数所代表的ADC通道为第一个转换通道)和结果寄存器0对应,转换后的结果存放在寄存器0中。 框图3和4并不是一 一对应的关系,比如你也可以写 A2➡CONV00=2➡结果寄存器0,表示ADCINA2为第一个转换通道,结果存放在寄存器0中。

①级联排序器顺序采样模式

在级联排序器操作方式下,2 个 8 状态排序器(SEQ1 和 SEQ2)构成一个 16状态的排序器 SEQ 控制外部输入的模拟信号的排序,通过控制寄存器 CONVxx 的4 位值确定输入引脚,其中最高位确定采用哪个采样保持缓冲器,其他 3 位定义具体输入引脚。这里结合控制数更好懂一些,比如:ADCINA1的控制数为0x01,0001,最高位为0则采用A采样保持缓冲器,后面的001则表示具体引脚INA1,以此类推。两个采样保持器对应各自的 8 选 1 多路选择器和 8 个输入通道。

程序举例更能说明:

例1:级联模式下,ADCINA0、ADCINB1、ADCINA2和ADCINB5输入通道轮回顺序采样

//ADC工作方式设置:采样方式、工作频率、采样通道等AdcRegs.ADCTRL3.bit.ADCCLKPS = ADC_CKPS;//HSPCLK进行ADC_CKPS*2分频得到ADCLK,ADC工作时钟,这里进行了2分频,ADC工作时钟为12.5MHzAdcRegs.ADCTRL1.bit.ACQ_PS = ADC_SHCLK;//也就是ADC采样时间 = (ADC_SHCLK+1) * ADCLKAdcRegs.ADCTRL3.bit.SMODE_SEL = 0;//顺序采样(0),同步采样(1)AdcRegs.ADCTRL1.bit.SEQ_CASC = 1;//双排序(0),级联排序(1)AdcRegs.ADCTRL1.bit.CONT_RUN = 1;//非连续运行(0),连续运行(1)AdcRegs.ADCMAXCONV.bit.MAX_CONV1 = 0x3;//最大变换通道数 = 实际变换通道数-1AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0;//设置ADCINA0控制数为0x0,作为第1个变换,存入结果寄存器0AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x9;//设置ADCINB1控制数为0x9,作为第2个变换,存入结果寄存器1AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2;//设置ADCINA2控制数为0x2,作为第3个变换,存入结果寄存器2AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0xD;//设置ADCINB5控制数为0xD,作为第4个变换,存入结果寄存器3AdcRegs.ADCTRL2.bit.EPWM_SOCA_SEQ1 = 1;//使能 PWM SOC触发AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1 = 1;//使能 SEQ1 中断例2: 级联模式下轮回转换16个通道的操作。下表为ADCCHSELSEQn寄存器,配置如下:

| 地址 | 位15~12 | 位11~8 | 位7~4 | 位3~0 | 寄存器 |

| 70A3h | 3 | 2 | 1 | 0 | CHSELSEQ1 |

| 70A4h | 7 | 6 | 5 | 4 | CHSELSEQ2 |

| 70A5h | 11 | 10 | 9 | 8 | CHSELSEQ3 |

| 70A6h | 15 | 14 | 13 | 12 | CHSELSEQ4 |

//ADC工作方式设置:采样方式、工作频率、采样通道等AdcRegs.ADCTRL3.bit.ADCCLKPS = ADC_CKPS;//HSPCLK进行ADC_CKPS*2分频得到ADCLK,ADC工作时钟,这里进行了2分频,ADC工作时钟为12.5MHzAdcRegs.ADCTRL1.bit.ACQ_PS = ADC_SHCLK;//也就是ADC采样时间 = (ADC_SHCLK+1) * ADCLKAdcRegs.ADCTRL3.bit.SMODE_SEL = 0;//顺序采样(0),同步采样(1)AdcRegs.ADCTRL1.bit.SEQ_CASC = 1;//双排序(0),级联排序(1)AdcRegs.ADCTRL1.bit.CONT_RUN = 1;//非连续运行(0),连续运行(1)AdcRegs.ADCMAXCONV.bit.MAX_CONV1 = 0xF;//最大变换通道数 = 实际变换通道数-1AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0;//设置ADCINA0控制数为0x0,作为第1个变换,存入结果寄存器0AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1;//设置ADCINA1控制数为0x1,作为第2个变换,存入结果寄存器1AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2;//设置ADCINA2控制数为0x2,作为第3个变换,存入结果寄存器2AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3;//设置ADCINA3控制数为0x3,作为第4个变换,存入结果寄存器3AdcRegs.ADCCHSELSEQ2.bit.CONV04 = 0x4;//设置ADCINA4控制数为0x4,作为第5个变换,存入结果寄存器4AdcRegs.ADCCHSELSEQ2.bit.CONV05 = 0x5;//设置ADCINA5控制数为0x5,作为第6个变换,存入结果寄存器5AdcRegs.ADCCHSELSEQ2.bit.CONV06 = 0x6;//设置ADCINA6控制数为0x6,作为第7个变换,存入结果寄存器6AdcRegs.ADCCHSELSEQ2.bit.CONV07 = 0x7;//设置ADCINA7控制数为0x7,作为第8个变换,存入结果寄存器7AdcRegs.ADCCHSELSEQ3.bit.CONV08 = 0x8;//设置ADCINB0控制数为0x8,作为第9个变换,存入结果寄存器8AdcRegs.ADCCHSELSEQ3.bit.CONV09 = 0x9;//设置ADCINB1控制数为0x9,作为第10个变换,存入结果寄存器9AdcRegs.ADCCHSELSEQ3.bit.CONV010 = 0xA;//设置ADCINB2控制数为0xA,作为第11个变换,存入结果寄存器10AdcRegs.ADCCHSELSEQ3.bit.CONV011 = 0xB;//设置ADCINB3控制数为0xB,作为第12个变换,存入结果寄存器11AdcRegs.ADCCHSELSEQ4.bit.CONV012 = 0xC;//设置ADCINB4控制数为0xC,作为第13个变换,存入结果寄存器12AdcRegs.ADCCHSELSEQ4.bit.CONV013 = 0xD;//设置ADCINB5控制数为0xD,作为第14个变换,存入结果寄存器13AdcRegs.ADCCHSELSEQ4.bit.CONV014 = 0xE;//设置ADCINB6控制数为0xE,作为第15个变换,存入结果寄存器14AdcRegs.ADCCHSELSEQ4.bit.CONV015 = 0xF;//设置ADCINB7控制数为0xF,作为第16个变换,存入结果寄存器15AdcRegs.ADCTRL2.bit.EPWM_SOCA_SEQ1 = 1;//使能 PWM SOC触发AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1 = 1;//使能 SEQ1 中断理论+程序更容易看懂,上述备注中已说明的很清楚。

②级联排序器同步采样模式

如果一个输入来自 ADCINA0-ADCINA7,另一个输入来自 ADCINB0-ADCINB7,ADC 能够实现 2 个 ADCINxx 输入的同时采样。此外,要求 2 个输入必须有同样的采样和保持偏移量(比如 ADCINA4 和 ADCINB4,不能是 ADCINA7 和 ADCINA6)。为了让 ADC 模块工作在同步采样模式,必须设置 ADCTRL3 寄存器中的 SMODE_SEL位为 1。

在同步采样模式下,CONVxx 寄存器的最高位不起作用,每个采样和保持缓冲器对 CONVxx 寄存器低 3 位确定的引脚进行采样。

例如,如果向 CONVxx 寄存器写入的值是 0110b,ADCINA6 就由采样保持器 A 采样,ADCINB6 有采样保持器 B 采样,和向寄存器中写1110b 的效果是一样的;如果 CONVxx 寄存器的值是 1001b,ADCINA1 由采样和保持器 A 采样,ADCINB1 由采样和保持器 B 采样。

采样保持两路可以同步进行,因为有两个采样保持器,但是转换不可能同时进行。转换器首先转换采样保持器 A中锁存的电压量,然后转换采样保持器 B 中锁存的电压量。采样保持器 A 转换的结果保存到当前的 ADCRESULTn 寄存器(如果排序器已经复位,SEQ1 的结果放ADCRESULT0),采样保持器 B 转换的结果保存到下一个(顺延)ADCRESULTn 寄存器(如果排序器已经复位,SEQ1 的结果放到 ADCRESULT1),结果寄存器指针每次增加 2。

程序举例更能说明:

例:级联排序器操作方式下,双通道同时采样,8对(16个通道)模拟量均由SEQ1排序控制。这里的SEQ1和程序中的ADCCHSELSEQ1不同,可以认为,SEQ1排序器里边有ADCCHSELSEQ1和ADCCHSELSEQ2,SEQ2排序器里边有ADCCHSELSEQ3和ADCCHSELSEQ4。目前这样方便理解,但真实是不是这样的,有待确认,欢迎提出指正。

//ADC工作方式设置:采样方式、工作频率、采样通道等AdcRegs.ADCTRL3.bit.ADCCLKPS = ADC_CKPS;//HSPCLK进行ADC_CKPS*2分频得到ADCLK,ADC工作时钟,这里进行了2分频,ADC工作时钟为12.5MHzAdcRegs.ADCTRL1.bit.ACQ_PS = ADC_SHCLK;//也就是ADC采样时间 = (ADC_SHCLK+1) * ADCLKAdcRegs.ADCTRL3.bit.SMODE_SEL = 1;//顺序采样(0),同步采样(1)AdcRegs.ADCTRL1.bit.SEQ_CASC = 1;//双排序(0),级联排序(1)AdcRegs.ADCTRL1.bit.CONT_RUN = 1;//非连续运行(0),连续运行(1)AdcRegs.ADCMAXCONV.bit.MAX_CONV1 = 0x7;//最大变换通道数 = 实际变换通道数-1AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0;//设置ADCINA0控制数为0x0,作为第1个变换,存入结果寄存器0AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1;//设置ADCINA1控制数为0x1,作为第2个变换,存入结果寄存器1AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2;//设置ADCINA2控制数为0x2,作为第3个变换,存入结果寄存器2AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3;//设置ADCINA3控制数为0x3,作为第4个变换,存入结果寄存器3AdcRegs.ADCCHSELSEQ2.bit.CONV04 = 0x4;//设置ADCINA4控制数为0x4,作为第5个变换,存入结果寄存器4AdcRegs.ADCCHSELSEQ2.bit.CONV05 = 0x5;//设置ADCINA5控制数为0x5,作为第6个变换,存入结果寄存器5AdcRegs.ADCCHSELSEQ2.bit.CONV06 = 0x6;//设置ADCINA6控制数为0x6,作为第7个变换,存入结果寄存器6AdcRegs.ADCCHSELSEQ2.bit.CONV07 = 0x7;//设置ADCINA7控制数为0x7,作为第8个变换,存入结果寄存器7AdcRegs.ADCTRL2.bit.EPWM_SOCA_SEQ1 = 1;//使能 PWM SOC触发AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1 = 1;//使能 SEQ1 中断为什么只用开SEQ1中断而不开SEQ2中断?

这是因为在级联模式下,SEQ1的8状态排序和SEQ2的8状态排序公用一个触发源,所以只用开SEQ1的中断就够了。2个采样保持器复用一个A/D转换模块,16个输入通道复用2个采样保持器。

尽管只有一个A/D模块,但是2个采样保持器保证了F28335的ADC转换模块也能够同时采样2个输入通道,同时采样,但并不同步转换,但最终结果来看就等效为同步转换。

(2)双排序操作方式

双排序器方式内部结构图如下:

当 ADC 工作在双排序器工作方式下时,2 个 8 状态排序器(SEQ1 和 SEQ2)彼此独立。在这种方式下 PWMA 触发 SEQ1,PWMB 触发 SEQ2,触发源是独立的。双排序器工作方式可以将 ADC 看成两个独立的 AD 转换单元,每个单元由各自的触发源触发转换。

在双排序器连续采样模式下,一旦当前工作的排序器完成排序,任何一个排序器的挂起 ADC 开始转换都会开始执行。例如,当 SEQ1 产生 ADC 开始转换请求时,AD 单元正在对 SEQ2 进行转换,完成 SEQ2 的转换后会立即启动 SEQ1。SEQ1排序器有更高的优先级,如果 SEQ1 和 SEQ2 的 SOC 请求都没有挂起,并且 SEQ1和 SEQ2 同时产生 SOC 请求,则 ADC 完成 SEQ1 的有效排序后,将会立即处理新的SEQ1 的转换请求,SEQ2 的转换请求处于挂起状态。

双排序方式使用了 2 个排序器,SEQ1/SEQ2 能在一次排序过程中对 8 个任意通道进行排序转换。每次转换结果保存在相应的结果寄存器中,这些寄存器由低地址到高地址依次填充。

每个排序器中的转换通道个数依然受 MAXCONVn 控制,最大控制通道数为 7,而不是前面的 16。该值在自动排序转换的开始时被载到自动排序状态寄存器(AUTO_SEQ_SR)的排序计数器控制位(SEQ CNTR3-0),MAX CONVn 的值在 0-7内变化。当排序器安排内核从 CONV00 开始按顺序转换时,SEQ CNTRn 的值从装载值开始向下计数,直到 SEQ CNTRn 为 0.一次自动排序完成的转换数为 MAXCONVn+1。

一旦排序器接收到触发源开始转换(SOC)信号就开始转换,SOC 触发信号也会装载 SEQ CNTRn 位,ADCCHSELSEQn 位自动减 1。一旦 SEQCNTRn 递减到 0,根据寄存器 ADCTRL1 中的连续运行状态位(CONT_RUN)的不同会出现 2 种情况:

①如果 CONT_RUN 置 1,转换序列重新自动开始(比如 SEQ_CNTRn 装入最初的MAX_CONV1 的值,并且 SEQ1 通道指针指向 CONV00)。在这种情况下,为了避免覆盖先前转换的结果,必须保证在下一个转换序列开始之前读走结果寄存器的值。当 ADC 模块产生冲突时(ADC 向结果寄存器写入数据的同时,用户从结果寄存器读取数据),ADC 内部的仲裁逻辑保证结果寄存器的内容不会被破坏,发出延时写等待。

②如果 CONT_RUN 没有置位,排序指针停留在最后的状态,SEQ_CNTRn 继续保持 0。为了在下一个启动时重复排序操作,在下一个 SOC 信号到来之前不需使用RST_SETQn 位复位排序器。

SEQ_CNTRn 每次归零时,中断标志位都置位,用户可以在中断服务子程序中用 ADCTRL2 寄存器的 RST_SETQn 位将排序器手动复位。这样可以将 SETQn 状态复位到初始值(SEQ1 复位值 CONV00,SEQ2 复位值 CONV08),这一特点在启动/停止排序器操作时非常有用。

以上的理论看得懂的就看的懂,看不懂也就罢了。直接看程序!

①双排序器顺序采样模式

例:SEQ1 完成 7 个通道的模数转换,分别是模拟输入 ADCINA2、ADCINA3、ADCINA2、ADCINA3、ADCINA6、ADCINA7 和 ADCINB4。

使用 SEQ1 完成 7 个通道的模数转换(模拟输入 ADCINA2、ADCINA3、ADCINA2、ADCINA3 、ADCINA6 、 ADCINA7 和 ADCINB4) , 则 MAX_CONV 应 被 设为 6 ,且ADCCHSELSEQn 寄存器的值确定如下所示:

//ADC工作方式设置:采样方式、工作频率、采样通道等AdcRegs.ADCTRL3.bit.ADCCLKPS = ADC_CKPS;//HSPCLK进行ADC_CKPS*2分频得到ADCLK,ADC工作时钟,这里进行了2分频,ADC工作时钟为12.5MHzAdcRegs.ADCTRL1.bit.ACQ_PS = ADC_SHCLK;//也就是ADC采样时间 = (ADC_SHCLK+1) * ADCLKAdcRegs.ADCTRL3.bit.SMODE_SEL = 1;//顺序采样(0),同步采样(1)AdcRegs.ADCTRL1.bit.SEQ_CASC = 0;//双排序(0),级联排序(1)AdcRegs.ADCTRL1.bit.CONT_RUN = 1;//非连续运行(0),连续运行(1)AdcRegs.ADCMAXCONV.bit.MAX_CONV1 = 0x6;//最大变换通道数 = 实际变换通道数-1AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x2;//设置ADCINA2控制数为0x2,作为第1个变换,存入结果寄存器0AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x3;//设置ADCINA3控制数为0x3,作为第2个变换,存入结果寄存器1AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2;//设置ADCINA2控制数为0x2,作为第3个变换,存入结果寄存器2AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3;//设置ADCINA3控制数为0x3,作为第4个变换,存入结果寄存器3AdcRegs.ADCCHSELSEQ2.bit.CONV04 = 0x6;//设置ADCINA6控制数为0x6,作为第5个变换,存入结果寄存器4AdcRegs.ADCCHSELSEQ2.bit.CONV05 = 0x7;//设置ADCINA7控制数为0x7,作为第6个变换,存入结果寄存器5AdcRegs.ADCCHSELSEQ2.bit.CONV06 = 0xC;//设置ADCINB4控制数为0xC,作为第7个变换,存入结果寄存器6AdcRegs.ADCTRL2.bit.EPWM_SOCA_SEQ1 = 1;//使能 PWM SOC触发AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1 = 1;//使能 SEQ1 中断这里的顺序采样模式,双排序器只用到了SEQ1,没用到SEQ2, 至于怎么用SEQ2,还有最大转换通道数怎么确定,有待深入学习。

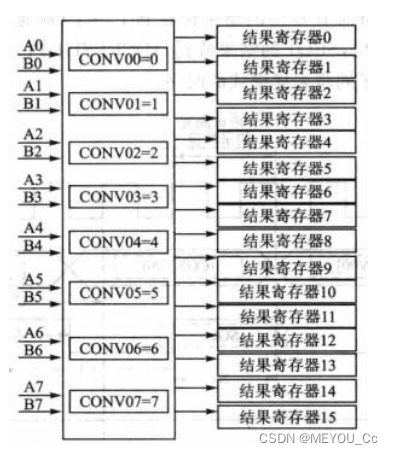

②双排序器同步采样模式

在同步采样模式下,双排序器和级联排序器相比,主要区别在于:

在双排序器中每个排序器分别控制4个转换8个通道,共构成16通道;而在级联排序器的同步采样模式下,实际上只用了SEQ1作为排序器,控制8个转换16个通道。

//ADC工作方式设置:采样方式、工作频率、采样通道等AdcRegs.ADCTRL3.bit.ADCCLKPS = ADC_CKPS;//HSPCLK进行ADC_CKPS*2分频得到ADCLK,ADC工作时钟,这里进行了2分频,ADC工作时钟为12.5MHzAdcRegs.ADCTRL1.bit.ACQ_PS = ADC_SHCLK;//也就是ADC采样时间 = (ADC_SHCLK+1) * ADCLKAdcRegs.ADCTRL3.bit.SMODE_SEL = 1;//顺序采样(0),同步采样(1)AdcRegs.ADCTRL1.bit.SEQ_CASC = 0;//双排序(0),级联排序(1)AdcRegs.ADCTRL1.bit.CONT_RUN = 1;//非连续运行(0),连续运行(1)AdcRegs.ADCMAXCONV.bit.MAX_CONV1 = 0x33;//最大变换通道数 = 实际变换通道数-1AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0;//设置ADCINA0和ADCINB0,作为第1个变换,存入结果寄存器0、1AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1;//设置ADCINA1和ADCINB1,作为第2个变换,存入结果寄存器2、3AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2;//设置ADCINA2和ADCINB2,作为第3个变换,存入结果寄存器4、5AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3;//设置ADCINA3和ADCINB3,作为第4个变换,存入结果寄存器6、7AdcRegs.ADCCHSELSEQ3.bit.CONV04 = 0x4;//设置ADCINA4和ADCINB4,作为第5个变换,存入结果寄存器8、9AdcRegs.ADCCHSELSEQ3.bit.CONV05 = 0x5;//设置ADCINA5和ADCINB5,作为第6个变换,存入结果寄存器10、11AdcRegs.ADCCHSELSEQ3.bit.CONV06 = 0x6;//设置ADCINA6和ADCINB6,作为第7个变换,存入结果寄存器12、13AdcRegs.ADCCHSELSEQ3.bit.CONV07 = 0x7;//设置ADCINA7和ADCINB7,作为第8个变换,存入结果寄存器14、15AdcRegs.ADCTRL2.bit.EPWM_SOCA_SEQ1 = 1;//使能 PWM SOC触发AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1 = 1;//使能 SEQ1 中断AdcRegs.ADCMAXCONV.bit.MAX_CONV1 = 0x33;//最大变换通道数 = 实际变换通道数-1至于这里的0x33,可看作为对SEQ1的 3,SEQ2的3,因为这是双排序器,SEQ1和SEQ2是独立的,所以最大转换通道数的设置也是独立的。我是这么理解的,要不然这里的0x33没办法解释。

SEQ1和SEQ2同时运行,将对应通道的转换结果存储到结果寄存器中:

至此,ADC中最重要的一部分已分析完毕,基本够用,后续其他各功能学习,量力而行。

(3)排序器启动/停止模式

看不懂,暂时没用到,先略过。

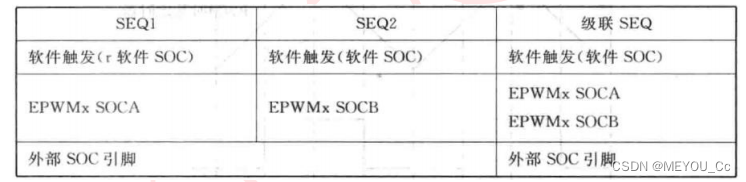

(4)输入触发源

每个排序器都有一系列可以使能或禁止的触发源。SEQ1、SEQ2 和级联 SEQ的有效输入触发源如下图所示:

只要排序器处于空闲状态,SOC 触发源就能启动一个自动转换排序器。空闲状态是指在收到触发信号前,排序器的指针指向 CONV00,或者是排序器已经完成了一个转换排序,也就是 SEQ_CNTRn 为 0。如果转换序列正在运行时,到来一个新的 SOC 触发信号,则 ADCTRL2 寄存器中的 SOC_SEQn 位置 1(该位在前一个转换开始时已经清除)。但如果又一个 SOC 触发信号到来,则该信号将被丢失,也就是当 SOC_SEQn 位置 1 时(SOC 挂起),随后的触发不起作用。

被触发后,排序器不能在中途停止或中断。程序必须等到一个序列的结束或复位排序器,才

能使排序器恢复到初始空闲状态(SEQ1 和级联的排序器指针指向 CONV00,SEQ1的指针指向 CONV08)。当 SEQ1/2 用于级联同步采样模式时,SEQ2 的触发源被忽略,SEQ1 的触发源有效。因此级联模式可以看做 SEQ1 有 16 个转换通道(并且把SEQ2排序器里边有ADCCHSELSEQ3和ADCCHSELSEQ4归属于SEQ1排序器中,我是这么理解的,至于真实是不是这样,自行分辨)。

(5)排序器转换的中断操作

看不懂,暂时没用到,先略过。

(6)排序器覆盖功能

看不懂,暂时没用到,先略过。

2.2ADC时钟控制

外设时钟 HSPCLK 是通过 ADCTRL3 寄存器的 ADCCLKPS[3-0]位来分频的,然后再通过寄存器 ADCTRL1 中的 CPS 位进行 2 分频或者不分频。此外,ADC 模块还通过扩展采样获取周期调整信号源阻抗,这由 ADCTRL1 寄存器中的 ACQPS3-0 位控制。这些位并不影响采样保持和转换过程,但通过延长转换脉冲的长度可以增加采样时间的长度,如下图所示:

ADC时钟来源。

注意:F28335 中的 ADC 模块在所有电路上电之后需要延迟 5ms,这一点和其他 DSP 的 AD 模块有所不同。

程序的编程,要结合相关寄存器的功能说明去理解,这里就不一 一列举寄存器的功能说明了。

这篇关于【DSP系列】TMS320F28335——ADC采集的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!