本文主要是介绍华为海思校园招聘-芯片-数字 IC 方向 题目分享——第四套,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

华为海思校园招聘-芯片-数字 IC 方向 题目分享——第四套

(共9套,有答案和解析,答案非官方,仅供参考)(共九套,每套四十个选择题)

部分题目分享,完整版获取(WX:didadidadidida313,加我备注:CSDN huawei数字芯片题目,谢绝白嫖哈)

华为海思校园招聘-芯片-数字 IC 方向

(第四套)

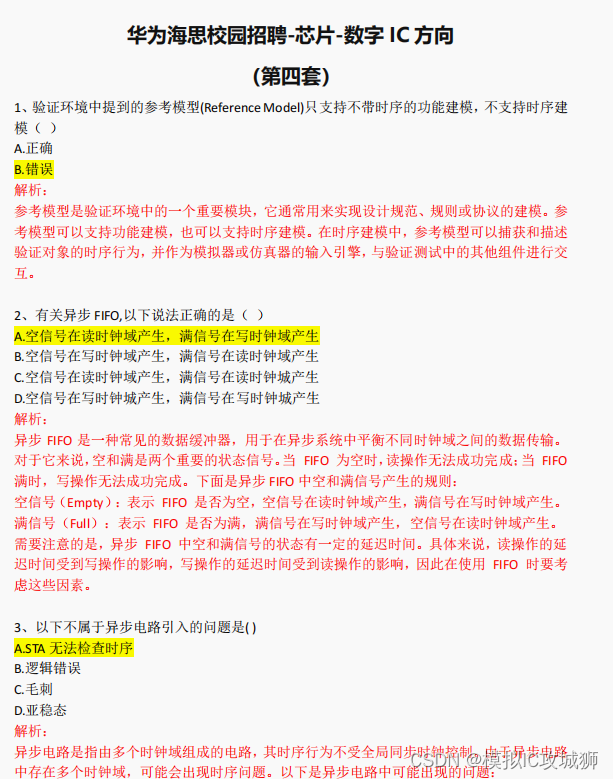

1、验证环境中提到的参考模型(Reference Model)只支持不带时序的功能建模,不支持时序建

模( )

A.正确

B.错误

解析:

参考模型是验证环境中的一个重要模块,它通常用来实现设计规范、规则或协议的建模。参

考模型可以支持功能建模,也可以支持时序建模。在时序建模中,参考模型可以捕获和描述

验证对象的时序行为,并作为模拟器或仿真器的输入引擎,与验证测试中的其他组件进行交

互。

2、有关异步 FIFO,以下说法正确的是( )

A.空信号在读时钟域产生,满信号在写时钟域产生

B.空信号在写时钟域产生,满信号在读时钟域产生

C.空信号在读时钟域产生,满信号在读时钟城产生

D.空信号在写时钟城产生,满信号在写时钟城产生

解析:

异步 FIFO 是一种常见的数据缓冲器,用于在异步系统中平衡不同时钟域之间的数据传输。

对于它来说,空和满是两个重要的状态信号。当 FIFO 为空时,读操作无法成功完成;当 FIFO

满时,写操作无法成功完成。下面是异步 FIFO 中空和满信号产生的规则:

空信号(Empty):表示 FIFO 是否为空,空信号在读时钟域产生,满信号在写时钟域产生。

满信号(Full):表示 FIFO 是否为满,满信号在写时钟域产生,空信号在读时钟域产生。

需要注意的是,异步 FIFO 中空和满信号的状态有一定的延迟时间。具体来说,读操作的延

迟时间受到写操作的影响,写操作的延迟时间受到读操作的影响,因此在使用 FIFO 时要考

虑这些因素。

3、以下不属于异步电路引入的问题是( )

A.STA 无法检查时序

B.逻辑错误

C.毛刺

D.亚稳态

解析:

异步电路是指由多个时钟域组成的电路,其时序行为不受全局同步时钟控制。由于异步电路

中存在多个时钟域,可能会出现时序问题。以下是异步电路中可能出现的问题:

B. 逻辑错误:异步电路中的各个电路模块之间可能存在状态冲突,导致逻辑错误。

C. 毛刺:由于信号传输延迟等原因,异步信号的上升沿、下降沿和保持时间等可能会出现

毛刺现象。

D. 亚稳态:由于异步电路中各模块时序关系的复杂性,可能会存在一些在特定条件下不稳

定的状态,这种状态称为亚稳态。

因为异步电路的时序行为复杂,不同时钟域的信号可能出现短暂的非确定性状态。STA 在检

查时序时会假定所有信号严格遵循一个全局同步时钟,因此在异步电路中不能直接使用 STA

检查时序,需要使用异步时序分析工具进行分析。

4、下列关于静态随机存储器(SRAM)和动态随机存储器(DRAM 说法错误的是( )。

A.DRAM 的存储单元结构中晶体管数量比 SRAM 的多

B.SRAM 的存储单元结构中晶体管数量比 DRAM 的多

C.SRAM 存放的信息在不停电的情况下能长时间保留

D.DRAM 存放的信息在不停电的情况下,会丢失保存的信息。

解析:

SRAM 和 DRAM 是两种常见的随机存储器。它们的主要区别在于存储单元的结构和访问方

式。下面是有关 SRAM 和 DRAM 的几个说法:

A. DRAM 的存储单元结构中晶体管数量比 SRAM 的多。这个说法是正确的,DRAM 使用一个

存储电容来存储单元的信息,需要使用一个晶体管作为开关来控制读写电路。因此,对于同

样大小的存储单元,DRAM 需要的晶体管数比 SRAM 更多。

B. SRAM 的存储单元结构中晶体管数量比 DRAM 的多。这个说法是错误的,因为 SRAM 使用

两个交叉反馈的存储单元以实现在电路中存储一个二进制位,所以对于同样大小的存储单

元,在 SRAM 中使用的晶体管数比 DRAM 少。

C. SRAM 存放的信息在不停电的情况下能长时间保留。这个说法是正确的,SRAM 使用的是

存储电路,因此它在不停电情况下可以长时间保持存储的信息。在掉电前,SRAM 会把数据

复制到电池供电的非易失性存储器中。

D. DRAM 存放的信息在不停电的情况下,会丢失保存的信息。这个说法是正确的,DRAM 使

用的是电容存储单元,电容被放电,因此在不带电的情况下数据不持久。所以在 DRAM 中需

要定期刷新(重载)存储电容,以防止数据丢失。

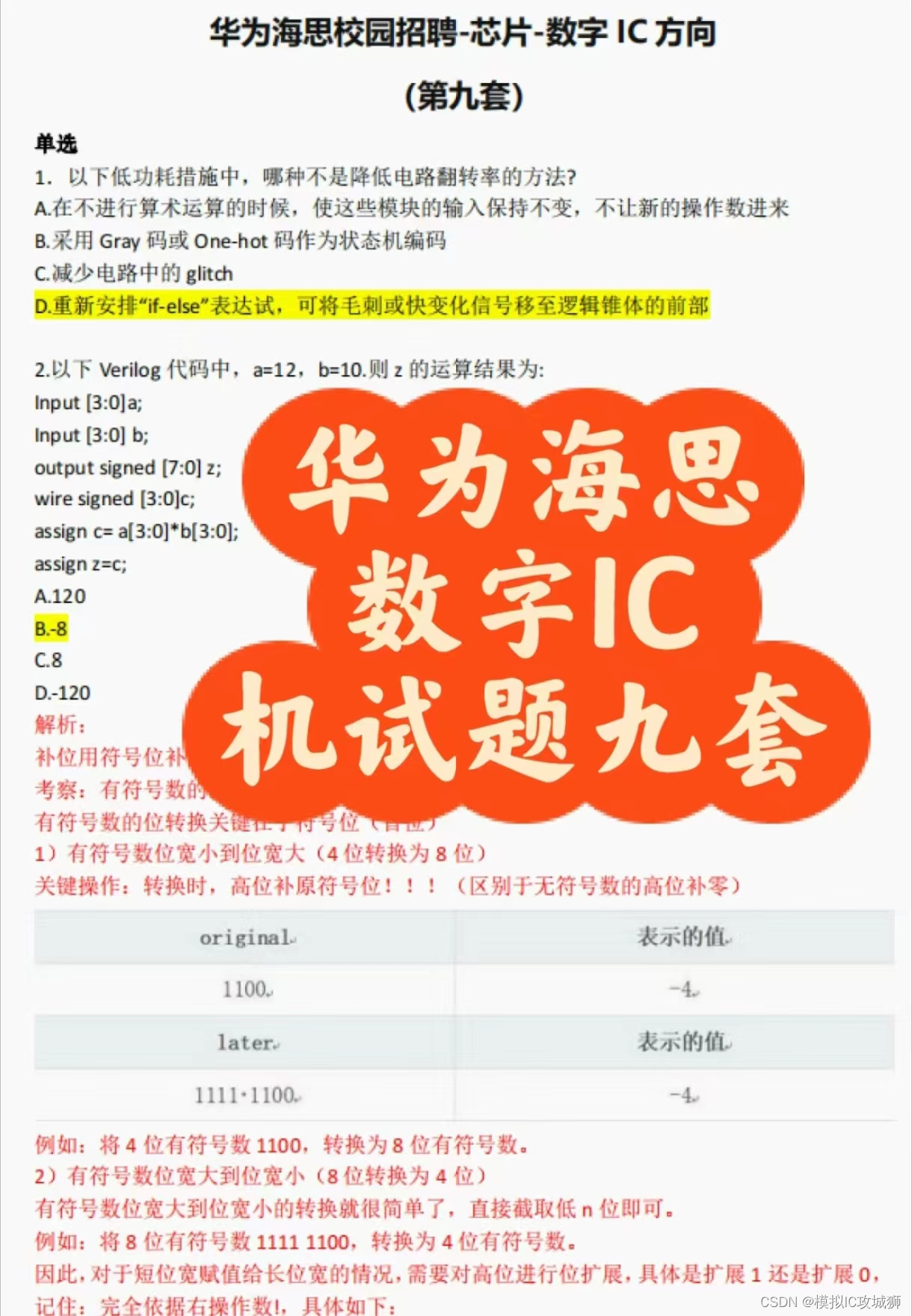

5、以下低功耗措施中,哪种不是降低电路翻转率的方法?( )

A.减少电路中的 glich

B.采用 Grav 码或 One‐hot 码作为状态机编码

C.在不进行算术运算的时候,使这些模块的输入保持不变,不让新的操作数进来

D.重新安排 if‐else 表达式将毛刺或快变化信号移至逻辑锥体的前部

解析:

低功耗是当代集成电路设计中的一个重要目标。电路翻转是消耗功耗的主要原因之一。以下

是几种降低电路翻转率的方法:

A. 减少电路中的 glitch。Glitch 是由于时序上的完整性问题而在电路中产生的短暂逻辑过渡

的现象,会引起电路翻转。通过减少 glitch,可以降低电路的翻转率。

B. 采用 Grav 码或 One‐hot 码作为状态机编码。在状态机的设计中,状态编码的选择会影响

电路的切换速度。采用 Grav 码或 One‐hot 码可以降低切换速度,减少状态翻转。

D. 重新安排 if‐else 表达式将毛刺或快变化信号移至逻辑锥体的前部。在时序电路中,毛刺

或快速变化信号可能会导致电路的翻转。通过重新安排 if‐else 表达式,将这些信号移至逻辑

锥体的前部可以有效降低电路的翻转率。

C. 在不进行算术运算的时候,使这些模块的输入保持不变,不让新的操作数进来,不是降

低电路翻转率的方法,它可以降低电路的功耗,但不会减少电路翻转。

6、以下说法错误的是( )

A.Latch(锁存器)静态时序分析比 D 触发器复杂

B.Latch(锁存器)容易产生毛刺,对毛刺敏感

C.Latch(锁存器)比 D 触发器的面积大,所以不建议使用

D.Latch 和寄存器样都能存储信息

解析:

Latch(锁存器)和 D 触发器是数字电路中常用的存储单元。它们都可以存储信息,但具有

不同的功能和特性。以下是有关 Latch 和 D 触发器的几个说法:

A. Latch(锁存器)静态时序分析比 D 触发器复杂。这个说法是正确的,因为 Latch 的时序特

性比 D 触发器更加复杂。Latch 具有透明和锁定两种模式,这两种模式在时序分析中需要考

虑。

B. Latch(锁存器)容易产生毛刺,对毛刺敏感。这个说法是正确的,Latch 的时序特性可能

导致毛刺的产生,而且 Latch 对毛刺非常敏感,没有正确的设计和时序分析可能会导致电路

故障。

C. Latch(锁存器)比 D 触发器的面积大,所以不建议使用。这个说法是错误的。Latch 和 D

触发器的面积大小取决于具体的设计和实现方法,没有明确的比较说法。

D. Latch 和寄存器样都能存储信息。这个说法是正确的,Latch 和寄存器样都是数字电路中常

用的存储单元,能够存储二进制信息。但是,它们的实现和使用方法不同,有着不同的特点

和适用范围。

7、在 PR 阶段将 std‐Vt 的逻辑单元替换为 high‐Vt 的逻辑单元主要作用是( )

A.降面积

B.优化时序

C.降低功耗

解析:

在芯片设计中,采用高阈值(high‐Vt)技术可以降低功耗。高阈值技术是通过将正常电路设

计中的标准阈值(std‐Vt)晶体管替换为高阈值(high‐Vt)晶体管的方式实现的。

在 PR(Physical Design and Verification)阶段,因为实际电路的时序和电流切换行为会受到工

艺因素的影响,所以需要将静态时序分析和时序优化与实际的工艺条件相结合。在这个过程

中,可以选择将 std‐Vt 的逻辑单元替换为 high‐Vt 的逻辑单元,以支持更低的功耗,这是使

用高阈值技术的主要目的之一。

此外,使用高阈值技术还可以带来其他优点,例如:

降低热失真:高阈值晶体管工作时需要更少的电流和电压,因此会产生更少的热能,从而减

少热失真。

增加可靠性:高阈值晶体管的带宽和噪声容限通常比标准晶体管更好,这可以提高电路的可

靠性。

简化布局布线:高阈值晶体管通常具有更大的面积和更迟缓的功率转移特性,这使得布局布

线的难度降低。

8、在 SystemVerilog 中,函数(function) 可以调用任务(task)。( )

A.正确

B.错误

9、以下不是 sva 语法的是( )

A. r o s e B . c l a s s C . p r o p e r t y D . c o v e r 解析:在 S y s t e m V e r i l o g A s s e r t i o n ( S V A )中, rose B. class C. property D.cover 解析: 在 SystemVerilog Assertion(SVA)中, roseB.classC.propertyD.cover解析:在SystemVerilogAssertion(SVA)中,rose,property 和 cover 都是常见的 SVA 语法。

A r o s e :在 S V A 中, rose:在 SVA 中, rose:在SVA中,rose 是一种时序操作符,用于检测时钟沿上升沿的发生。

C property:在 SVA 中,property 是一种用于表示设计行为规范的声明式语句。它可以用于描

述设计的正确性和安全性,并在验证过程中自动检测设计中的错误。

D cover:在 SVA 中,cover 表示评估用于检测设计中特定性质是否成立的 Coverage 规则。

Coverage 规则用于直接检测设计中的错误,通过评估特定条件的覆盖率来指导测试。

相反,class 不是 SVA 语法。Class 是 SystemVerilog 的另一个高级语言特性,它是一种面向对

象的编程语言扩展,主要用于描述和组织设计结构。

这篇关于华为海思校园招聘-芯片-数字 IC 方向 题目分享——第四套的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!