本文主要是介绍AD5758单通道16位电流和电压输出DAC的硬件应用介绍,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

概述

1 AD5758的功能介绍

1.1 特性

1.2 应用特性介绍

1.2.1 电源特性

1.2.2 通信特性

1.2.3 核心特性

2 AD5758的框架

2.1 AD5758的框架结构

2.2 AD5758外围引脚介绍

2.2.1 引脚框图

2.2.2 引脚功能介绍

3 AD5758的输出模式

3.1 电流输出模式

3.2 电压输出模式

4 经典AD5758应用电路

概述

AD5758是一款单通道、电压和电流输出数模转换器(DAC),采用AVSS 33 V(最小值)至AVDD1 +33 V(最大值)电源供电,两个供电轨之间的最大工作电压为60 V。片内动态功率控制(DPC)利用一个针对最小片内功耗而优化的降压型DC-DC转换器,在5 V至27 V范围内将输出驱动器电路的电源电压(VDPC+)调节至VIOUT,使封装功耗较小。CHART引脚可将HART信号耦合到电流输出上。该器件采用多功能四线式串行外设接口(SPI),能够以最高50 MHz的时钟速率工作,并与标准SPI、QSPI、MICROWIRE、DSP和微控制器接口标准兼容。该接口还具有可选SPI循环冗余校验(CRC)和看门狗定时器(WDT)。与前款产品相比,AD5758改善了诊断功能,如输出电流监控和集成12位诊断模数转换器(ADC)。通过在VIOUT、+VSENSE和VSENSE引脚上集成故障保护开关,提供额外的鲁棒性。

1 AD5758的功能介绍

1.1 特性

主要参数如下:

| 特性 | 参数 |

|---|---|

| 精度 | 16位分辨率和线性度 |

| 输出类型 | 电流/电压 |

| 电流输出范围 | 0 mA to 20 mA, 4 mA to 20 mA, 0 mA to 24 mA, ±20 mA, ±24 mA, -1 mA to +22 mA |

| 电压输出范围 | 0 V to 5 V, 0 V to 10 V, ±5 V, ±10 V |

| 工作温度范围 | -40°C to +115°C |

1.2 应用特性介绍

1.2.1 电源特性

AD5758是一款单通道电压和电流输出数模转换器(DAC),AVSS的-33 V(最小)到AVDD1的+33 V(最大),两者之间的最大工作电压为60 V。片上动态功率控制(DPC)通过使用降压dc- dc转换器将VIOUT输出驱动电路的电源电压(VDPC+)从5 V调节到27 V,从而最大限度地降低封装功耗,从而优化了片上功耗。CHART引脚可将HART®信号耦合到电流输出上。

1.2.2 通信特性

该设备使用通用4线串行外设接口(SPI)。它的时钟速率高达50兆赫,并且是兼容的标准SPI, QSPI™,MICROWIRE™,DSP和微控制器接口标准。该界面还具有一个可选SPI循环冗余校验(CRC)和看门狗计时器(WDT)。

AD5758提供了改进的诊断功能,如集成的12位诊断模数转换器(ADC)和通过+VSENSE和−VSENSE引脚,为VIOUT上的线路保护器额外的健壮性的保护电路。当有多个AD5758一起使用时电源管理单元(PMU)/隔离器(ADP1031)AD5758能够使客户开发一个8通道到通道隔离模拟输出模块用少功耗大于2w,同时满足CISPR 11 B类要求。

1.2.3 核心特性

1. DPC,采用集成降压dc- dc转换器为热管理。当与ADP1031一起使用时AD5758支持8通道到通道隔离输出耗散功率< 2w。

2. 一系列高级诊断功能,包括集成ADC,可靠性高。

3. 具有高度鲁棒性,具有防止误接线事件的输出保护(±38 V)。

4. HART兼容。

2 AD5758的框架

2.1 AD5758的框架结构

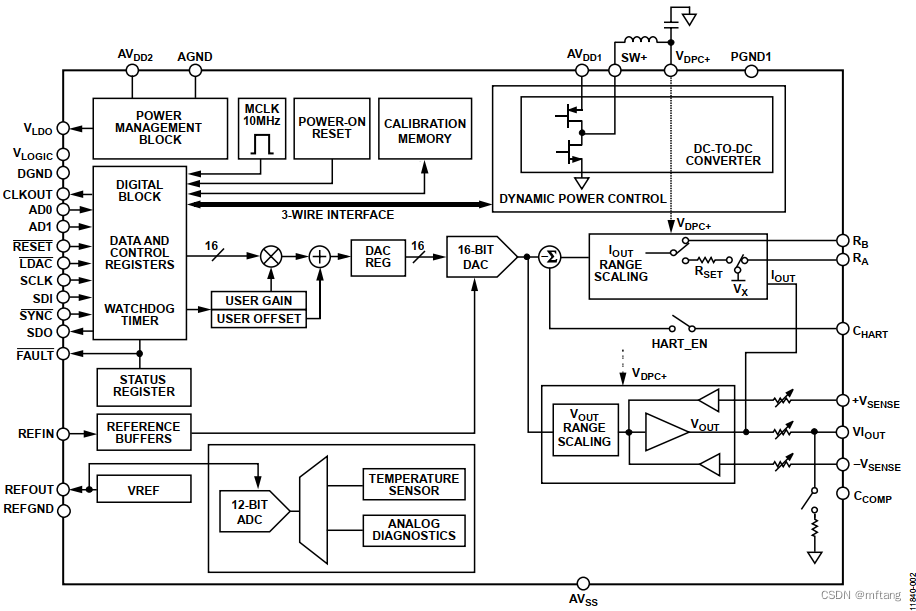

AD5758内部结构总结如下:

1)一个16bit递进累加型DAC模块

2)一个12bit ADC模块,用于监控DAC的输出特性

3)电压/电流输出控制

2.2 AD5758外围引脚介绍

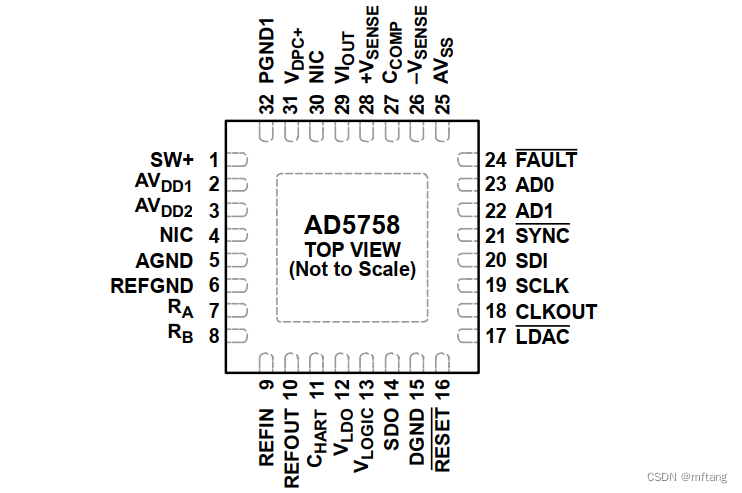

2.2.1 引脚框图

2.2.2 引脚功能介绍

| 引脚名称 | 功能介绍 |

|---|---|

| SW+ | 使用设备的dc-to-dc特性,使能dc - dc电路的开关输出 |

| AVDD1 | 正模拟电源。电压范围:7v ~ 33v。 |

| AVDD2 | 正低压模拟电源。电压范围:5v ~ 33v |

| NIC | 不需要连接的引脚 |

| AGND | 模拟电路的接地参考点。这个引脚必须连接到0v。 |

| REFGND | 内部参考的地面参考点。这个引脚必须连接到0v。 |

| RA | 外部电流设定电阻。RA和RB之间可以连接一个外部精密低漂移13.7 kΩ电流整定电阻,以提高电流输出温度漂移性能。建议将外部电阻尽可能靠近AD5758。 |

| RB | 外部电流设定电阻。RA和RB之间可以连接一个外部精密低漂移13.7 kΩ电流整定电阻,以提高电流输出温度漂移性能。建议将外部电阻尽可能靠近AD5758。 |

| REFIN | 外部2.5 V参考电压输入。 |

| REFOUT | 内部2.5 V参考电压输出。REFOUT必须连接到REFIN才能使用内部引用。不建议在REFOUT和REFGND之间安装电容。 |

| CHART | HART输入连接。HART信号必须与该引脚交流耦合。如果没有使用HART,请保持此引脚未连接。默认情况下,该引脚与HART求和节点断开连接,可以通过 GP_CONFIG1寄存器中的HART_EN位。 |

| VLDO | 3.3 V LDO输出电压。VLDO必须用0.1µF电容与AGND去耦 |

| VLOGIC | 数字电源。电压范围:1.71 V ~ 5.5 V。VLOGIC必须用0.1µF电容与DGND解耦 |

| SDO | 串行数据输出。该引脚以回读模式从串行寄存器中读取数据。读回模式的最大SCLK速度为15 MHz(取决于VLOGIC电压) |

| DGND | 数字电源地 |

| RESET | 硬件复位。低电平有效。在发出复位后100 μs内不要写SPI命令(使用硬件reset引脚或通过软件)。 |

| LDAC | 加载DAC的值。主动低输入。该引脚更新DAC_OUTPUT寄存器,从而更新DAC输出。不要在同步上升沿前500 ns或同步上升沿后1.5µs的窗口内断言LDAC |

| CLKOUT | 可选时钟输出信号(默认关闭)。该引脚是内部10 MHz振荡器(MCLK)的细分版本,并在GP_CONFIG1寄存器中配置。 |

| SCLK | 串行时钟输入。数据被输入到SCLK下降沿的输入移位寄存器中。在写模式下,该引脚工作在时钟速度高达50 MHz(取决于VLOGIC电压)。在读模式下,最大SCLK速度为15mhz(取决于VLOGIC电压)。 |

| SDI | 串行数据输入。数据必须在SCLK的下降沿上有效。 |

| SYNC | 串行接口的帧同步信号。主动低输入。当SYNC低时,数据在SCLK的下降沿上传输 |

| AD1 | AD5758的地址解码1 |

| AD0 | AD5758的地址解码0 |

| FAULT | 错误监测引脚。主动低,开漏输出。当没有检测到故障时,该引脚是高阻抗的,当检测到某些故障时,例如,电流模式下的开路,电压模式下的短路,CRC错误或过温错误(参见输出故障部分),该引脚被断言为低阻抗。该引脚必须用10 kΩ上拉电阻连接到VLOGIC。 |

| AVSS | 模拟地电源。电压范围为0v ~−33v。如果使用该设备仅用于单极电流输出目的,AVSS可以为0 V。对于单极电压输出,AVSS(最大)为−2.5 V。当使用双极输出范围时,在计算AVSS最大值时必须遵循VOUT/IOUT净空,例如,对于±10v输出,AVSS最大值为−12.5 V。有关电源顺序的重要说明,请参阅AVSS注意事项部分。 |

| -VSENSE | VOUT模式的负电压输出负载连接的感测连接。该引脚必须保持在±10v 指定操作的AGND。建议将串联1 kΩ电阻连接到该引脚。如果不使用遥感,将此引脚短至AGND。 |

| CCOMP | 电压输出缓冲器的可选补偿电容连接。在该引脚和VIOUT引脚之间连接一个220pf电容,可使电压输出驱动高达2µF。该电容器的加入减少了输出放大器的带宽,增加了稳定时间。 |

| +VSENSE | 电压输出模式下的正电压输出负载连接。建议将串联1 kΩ电阻连接到该引脚。如果不使用遥感,通过该系列将该引脚短至VIOUT 1 kΩ电阻器。 |

| VIOUT | 电压/电流输出引脚。VIOUT是一个共享引脚,提供缓冲输出电压或电流。 |

| NIC | 不需要连接的引脚 |

| VDPC+ | 电流和电压输出级正电源。要使用设备的dc-to-dc特性 |

| PGND1 | Power Ground. |

3 AD5758的输出模式

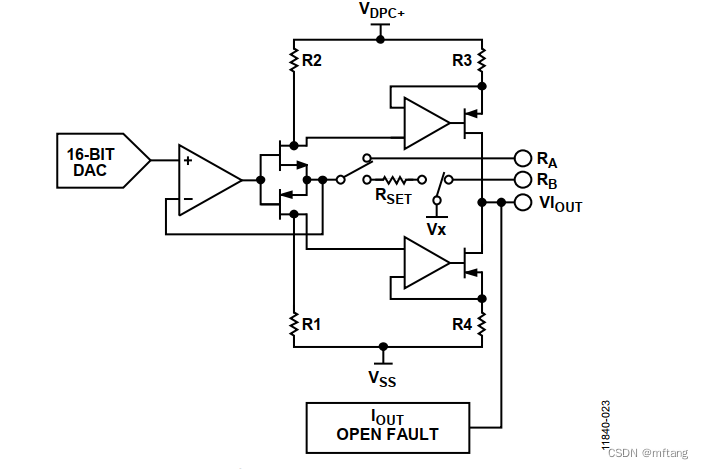

3.1 电流输出模式

如果使能电流输出模式,则从DAC被转换为电流,然后将其镜像到供电轨,以便应用程序只看到电流源输出。

可用电流范围为:

1)0 mA至20 mA,

2)0 mA至24 mA,

3)4 mA至20 mA,

4)±20 mA,

5)±24 mA,

6)−1 mA至+22 mA。

内部或外部13.7 kΩ RSET电阻可用于电压到电流的转换。具体电路结构如下:

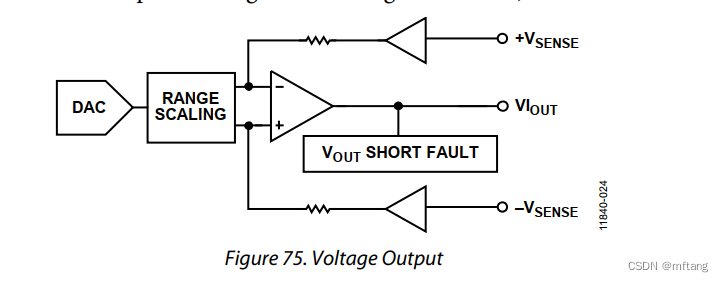

3.2 电压输出模式

如果使能了电压输出模式,则从DAC经过缓冲和缩放,可输出软件可选的单极或双极电压范围。

电压范围为:

1)0v ~ 5v

2)±5v

3)0v ~ 10v

4)±10v。

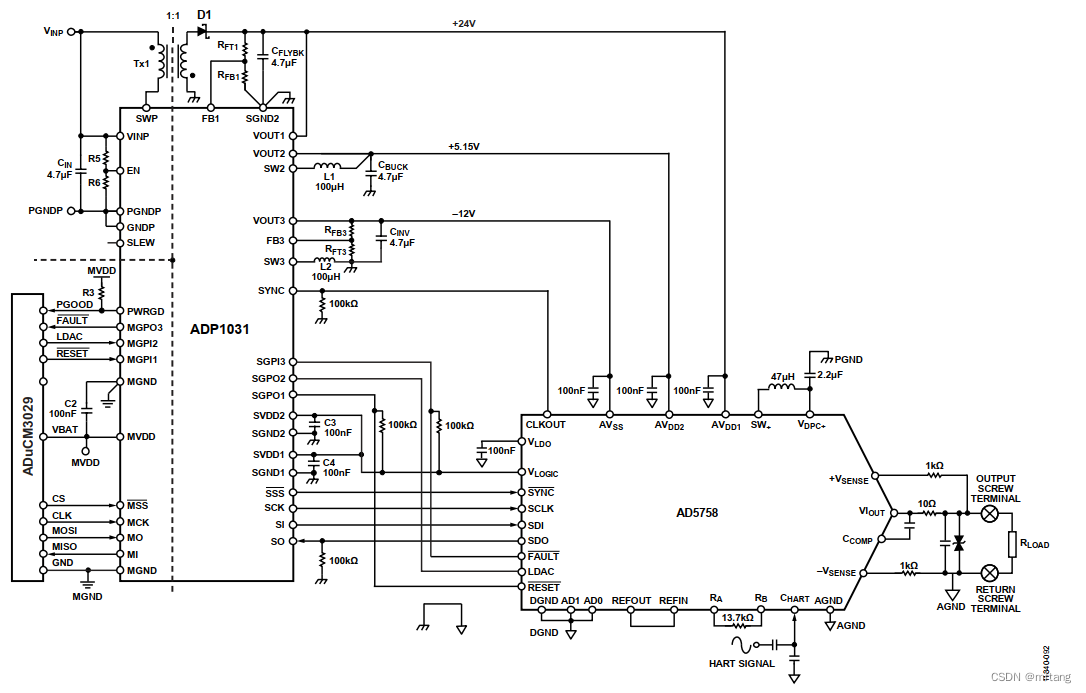

4 经典AD5758应用电路

这篇关于AD5758单通道16位电流和电压输出DAC的硬件应用介绍的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!