本文主要是介绍STM32 SPI NSS 功能的灵活应用案例,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1. 前言

某客户开发一款高精度工业测量仪器,打算使用 STM32H7+外置高精度 ADC 采样的分离方案来实现。客户选取了一款所属行业内比较通用的 ADC 采样芯片。

在读取该 ADC芯片手册后,客户发现该款 ADC 采样芯片使用 MCU 标准 SPI 与之通信存在问题,手册里面也推荐使用 DSP/FPGA 的来实现,客户一下就犯难了。为了降低成本和开发周期,客户想使用 MCU 来替代 DSP/FPGA 与 ADC 采样芯片的高速通信。

2. 现场调研与问题分析

根据客户提供的信号采集板上使用的 ADC 数据手册及现场反馈:

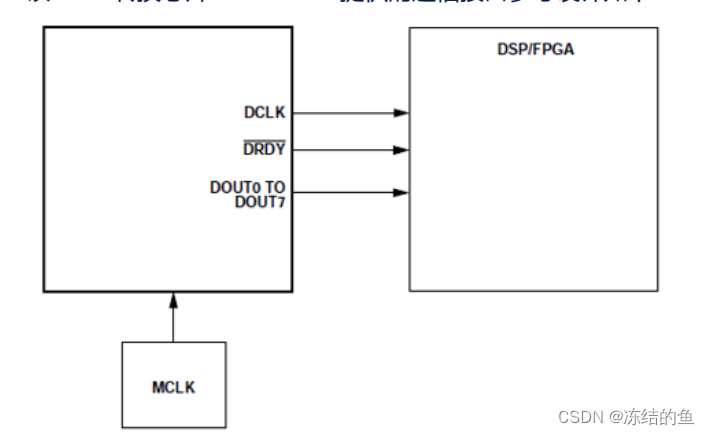

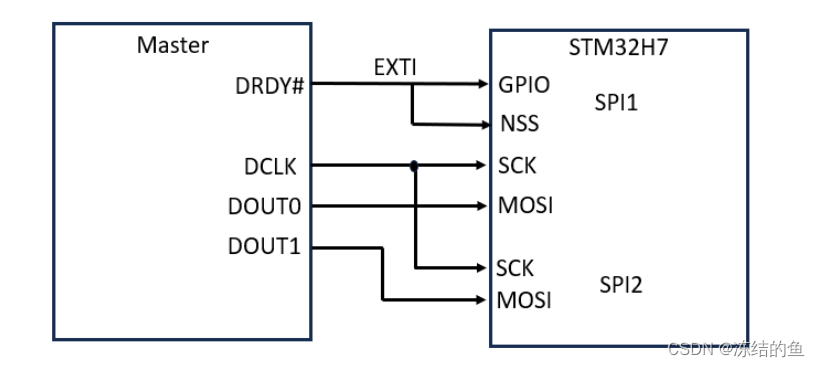

- 该 ADC 转换芯片 DataSheet 提供的通信接口参考设计如下:

- 该 ADC 采样芯片工作于 Master 模式,DSP/FPGA 工作于 Slave 模式,其通信时序如下图所示。在 DRDY 信号的下降沿通过 DOUT0~DOUT7 引脚将数据输出到 DSP/FPGA。

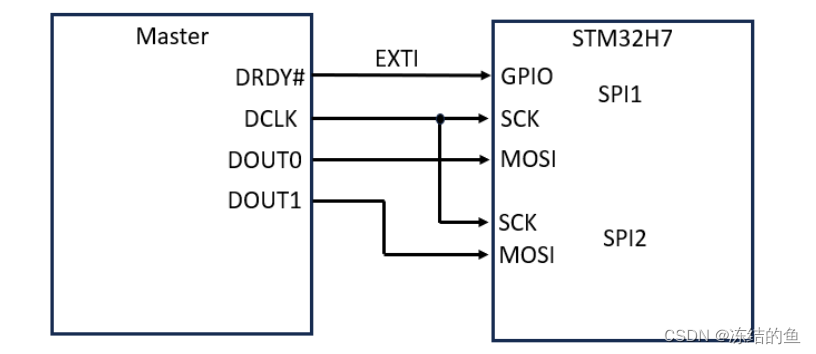

客户使用STM32H7 的 SPI Slave 模式与该 IC 进行通信,采用 Software NSS 工作模式来接收 Master 的数据。

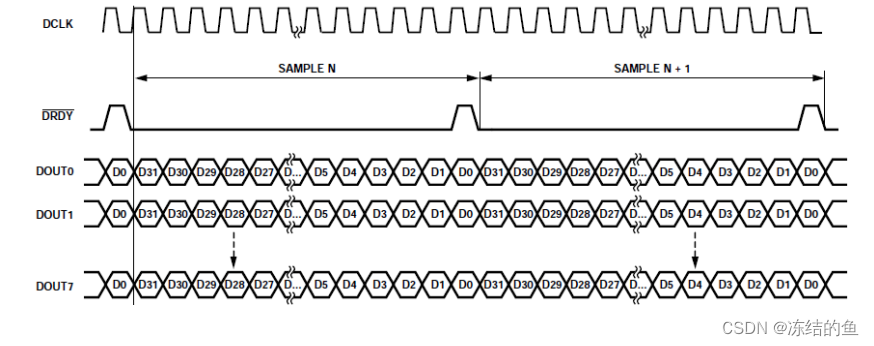

在连续采样模式下(Master 不间断采样),STM32H7 接收数据正常,其通信时序如下图所示。

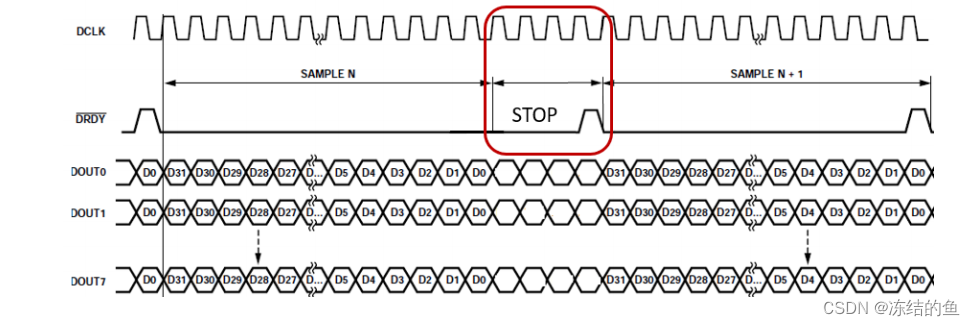

但是,当 Master 停止采样时,DCLK 仍然会一直工作发出工作时钟。此时,STM32H7 的 SPI 做Slave 在 Stop 期间仍然会收到数据(无效干扰数据)。此数据会造成 Slave 端接收数据失序,

如下图所示。

3. 问题分析与解决

显然使用标准 SPI 与该芯片进行通信是行不通的,再次聚焦到客户 DRDY 信号并未使用和充分利用,能否利用 DRDY 信号来滤除 Stop 期间的干扰信号呢?

笔者也再次查阅 RM 后发现 STM32H7 的 SPI NSS 脉冲模式(RM 中称为 TI 模式)。在本文中统称为 NSS 脉冲模式,STM32H7 的 NSS 脉冲模式其核心要点如下:

-

通过设置 SPI_CFG2 寄存器的 SP[2:0]位来使能 SPI 工作在 NSS 脉冲模式,当 SPI 工作于脉冲模式时,SCK 和 SS 引脚的信号极性、相位、字节序是固定的,不需要配置 CPOL, CPHA, LSBFRST, SSOM, SSOE, SSIOP 和 SSM 相关寄存器位。

-

SPI NSS 脉冲模式通信时序如下图,与标准 SPI 通信相比差异如下:

启动数据传输前,NSS 会被拉高并维持一个时钟周期(NSS 脉冲)。

数据帧的传输过程起止于 2 个 NSS 脉冲之间(前一帧 LSB 开始拉高 SS,前一帧 LSB 结束后拉低 NSS 开始下一帧传输)。

在时钟 SCK 的上升沿开始发送数据,在时钟 SCK 的下降沿进行采样和接收。

所以,STM32H7 的 SPI 的 NSS 脉冲模式时序刚好与该 ADC 芯片是匹配的。

那么我们将客户的接法进行改进,并配置 STM32H7 的 SPI 工作于 NSS 脉冲模式,经过客户

反复验证工作正常。

参考文献

本文档参考ST官方的《【应用笔记】LAT1398+STM32H7+SPI+NSS功能的灵活应用案例》文档。

参考下载地址:https://download.csdn.net/download/u014319604/89139845

这篇关于STM32 SPI NSS 功能的灵活应用案例的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!