本文主要是介绍STM32H7的Cache学习和应用,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

STM32H7的Cache学习和应用

- 啥是Cache?

- Cache的配置

- 配置 Non-cacheable

- 配置 Write through,read allocate,no write allocate

- 配置 Write back,read allocate,no write allocate

- 配置 Write back,read allocate,write allocate

- 共享配置是个隐形的大坑

- Cache的关键知识点

- Cache的推荐配置和隐患

啥是Cache?

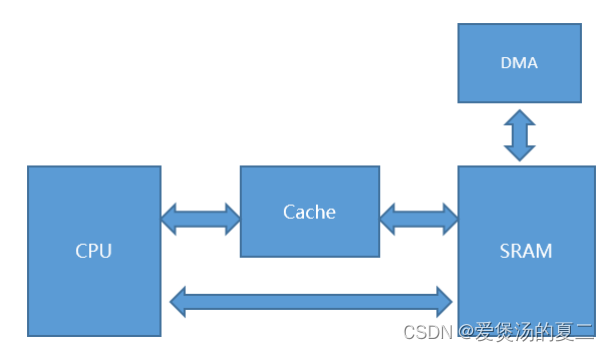

当前芯片厂商出的 M7 内核芯片基本都做了一级 Cache 支持,Cache 又分数据缓存 D-Cache 和指令缓冲 I-Cache,STM32H7 的数据缓存和指令缓存大小都是 16KB。对于指令缓冲,用户不用管,这里主要说的是数据缓存 D-Cache。以 STM32H7 为例,主频是 400MHz,除了 TCM 和 Cache 以 400MHz工作,其它 AXI SRAM,SRAM1,SRAM2 等都是以 200MHz 工作。数据缓存 D-Cache 就是解决 CPU加速访问 SRAM。

如果每次 CPU 要读写 SRAM 区的数据,都能够在 Cache 里面进行,自然是最好的,实现了 200MHz到 400MHz 的飞跃,实际是做不到的,因为数据 Cache 只有 16KB 大小,总有用完的时候。

读操作:

如果 CPU 要读取的 SRAM 区数据在 Cache 中已经加载好,这就叫读命中(Cache hit),如果 Cache里面没有怎么办,这就是所谓的读 Cache Miss。

写操作:

如果 CPU 要写的 SRAM 区数据在 Cache 中已经开辟了对应的区域(专业词汇叫 Cache Line,以 32字节为单位),这就叫写命中(Cache hit),如果 Cache 里面没有开辟对应的区域怎么办,这就是所谓的写 Cache Miss。

Cache的配置

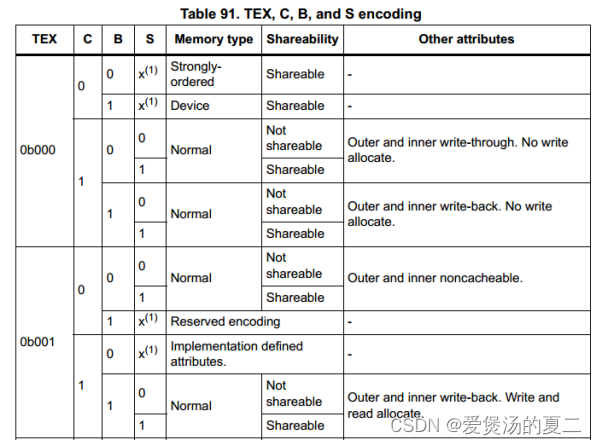

主要通过配置TEX C B S位,其中TEX是设置Cache的策略,B是缓冲用来配合Cache设置,S则是共享。

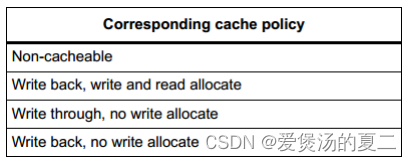

分为4种模式:

配置 Non-cacheable

这个最好理解,就是正常的读写操作,无 Cache。

配置 Write through,read allocate,no write allocate

使能了此配置的 SRAM 缓冲区写操作

如果 CPU 要写的 SRAM 区数据在 Cache 中已经开辟了对应的区域,那么会同时写到 Cache 里面和SRAM 里面;如果没有,就用到配置 no write allocate 了,意思就是 CPU 会直接往 SRAM 里面写数据,而不再需要在 Cache 里面开辟空间了。

在写 Cache 命中的情况下,这个方式的优点是 Cache 和 SRAM 的数据同步更新了,没有多总线访问造成的数据一致性问题。缺点也明显,Cache 在写操作上无法有效发挥性能。

对应的两种 MPU 配置如下:

TEX = 000 C=1 B=0 S=1

TEX = 000 C=1 B=0 S=0

配置 Write back,read allocate,no write allocate

使能了此配置的 SRAM 缓冲区写操作

如果 CPU 要写的 SRAM 区数据在 Cache 中已经开辟了对应的区域,那么会写到 Cache 里面,而不会立即更新 SRAM;如果没有,就用到配置 no write allocate 了,意思就是 CPU 会直接往 SRAM 里面写数据,而不再需要在 Cache 里面开辟空间了。

安全隐患,如果 Cache 命中的情况下,此时仅 Cache 更新了,而 SRAM 没有更新,那么 DMA 直接从 SRAM 里面读出来的就是错误的。

对应两种 MPU 配置如下:

TEX = 000 C=1 B=1 S=1

TEX = 000 C=1 B=1 S=0

配置 Write back,read allocate,write allocate

使能了此配置的 SRAM 缓冲区写操作

如果 CPU 要写的 SRAM 区数据在 Cache 中已经开辟了对应的区域,那么会写到 Cache 里面,而不会立即更新 SRAM;如果没有,就用到配置 write allocate 了,意思就是 CPU 写到往 SRAM 里面的数据,会同步在 Cache 里面开辟一个空间将 SRAM 中写入的数据加载进来,如果此时立即读此 SRAM 区,那么就会有很大的速度优势。

安全隐患,如果 Cache 命中的情况下,此时仅 Cache 更新了,而 SRAM 没有更新,那么 DMA 直接从 SRAM 里面读出来的就是错误的。

注意,M7 内核只要开启了 Cache,read allocate 就是开启的,因此4种模式的Cache的对SRAM的读操作一样:

read allocate下SRAM 缓冲区读操作

如果 CPU 要读取的 SRAM 区数据在 Cache 中已经加载好,就可以直接从 Cache 里面读取。如果没有,就用到配置 read allocate 了,意思就是在 Cache 里面开辟区域,将 SRAM 区数据加载进来,后续的操作,CPU 可以直接从 Cache 里面读取,从而时间加速。

安全隐患,如果 Cache 命中的情况下,DMA 写操作也更新了 SRAM 区的数据,CPU 直接从 Cache里面读取的数据就是错误的。

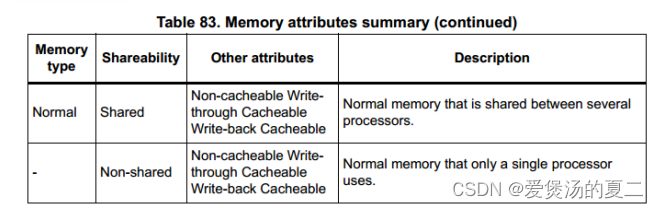

共享配置是个隐形的大坑

而 H7 的应用笔记对齐的描述是开启共享基本等同于关闭 Cache。

实际测试下面四种开 Cache 的情况,开关共享对缓冲区的大批量数据的读操作影响很大,基本差出两倍,而写操作基本没有影响,也许这就是所谓的多总线同步读造成的。另外共享开关仅对开启了 Cache 的情况下有影响,而对于关闭了 Cache 的情况是没有影响的,开不开没关系。(来源于安富莱_STM32-V7开发板手册)

Cache的关键知识点

- Cortex-M7 内核的 L1 Cache 由多行内存区组成,每行有 32 字节,每行都配有一个地址标签。数据缓冲 DCache 是每 4 行为一组,称为 4-way set associative。而指令缓冲区 ICache 是 2 行为一组,这样节省地址标签,不用每个行都标记一个地址。

- 对于读操作,只有在第 1 次访问指定地址时才会加载到 Cache,而写操作的话,可以直接写到内存中(write-through 模式)或者放到 Cache 里面,后面再写入(write-back 模式)。

- 如果采用的是 Write back,Cache line 会被标为 dirty,等到此行被 evicted 时,才会执行实际的写操作,将 Cache Line 里面的数据写入到相应的存储区。

- Cache 命中是访问的地址落在了给定的 Cache Line 里面,所以硬件需要做少量的地址比较工作,以检查此地址是否被缓存。如果命中了,将用于缓存读操作或者写操作。如果没有命中,则分配和标记新行,填充新的读写操作。如果所有行都分配完毕了,Cache 控制器将支持 eviction 操作。根据 Cache Line 替换算法,一行将被清除 Clean,无效化 Invalid 或者重新配置。数据缓存和指令缓存是采用的伪随机替换算法。

- Cache 支持的 4 种基本操作,使能,禁止,清空和无效化。Clean 清空操作是将 Cache Line 中标记为 dirty 的数据写入到内存里面,而无效化 Invalid 是将 Cache Line 标记为无效,即删除操作。

Cache的推荐配置和隐患

推荐使用 128KB 的 TCM 作为主 RAM 区,其它的专门用于大缓冲和 DMA 操作等。

Cache 问题主要是 CPU 和 DMA 都操作这个缓冲区时容易出现,使用时要注意。

Cache 配置的选择,优先考虑的是 WB,然后是 WT 和关闭 Cache,其中 WB 和 WT 的使用中可以配合 ARM 提供的函数解决上面说到的隐患问题(见本章 24.6 小节)。但不是万能的,在不起作用的时候,直接暴力选择函数 SCB_CleanInvlaidateDCache 解决。关于这个问题,在分别配置以太网MAC 的描述符缓冲区,发送缓冲区和接收缓冲区时尤其突出。

这篇关于STM32H7的Cache学习和应用的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!