本文主要是介绍华为海思校园招聘-芯片-数字 IC 方向 题目分享——第二套,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

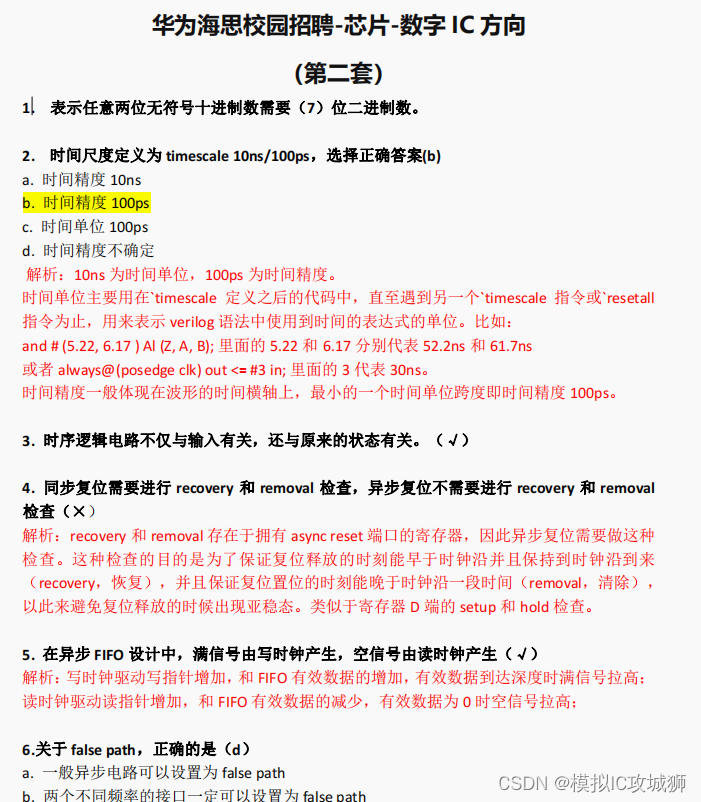

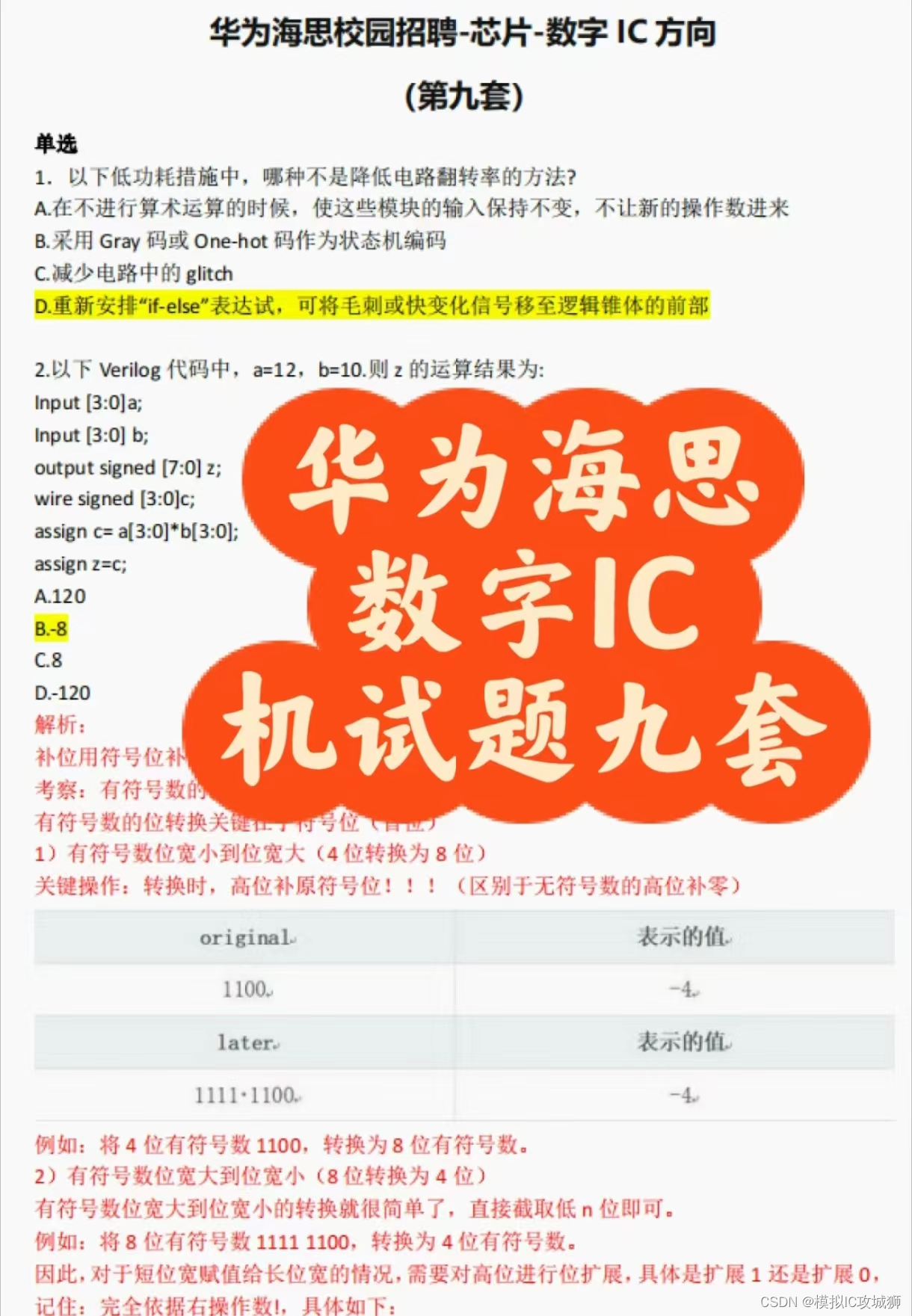

华为海思校园招聘-芯片-数字 IC 方向 题目分享(有参考答案)——第二套(共九套,每套四十个选择题)

部分题目分享,完整版获取(WX:didadidadidida313,加我备注:CSDN huawei数字芯片题目,谢绝白嫖哈)

-

表示任意两位无符号十进制数需要(7)位二进制数。

-

时间尺度定义为 timescale 10ns/100ps,选择正确答案(b)

a. 时间精度 10ns

(recovery,恢复),并且保证复位置位的时刻能晚于时钟沿一段时间(removal,清除),

以此来避免复位释放的时候出现亚稳态。类似于寄存器 D 端的 setup 和 hold 检查。 -

在异步 FIFO 设计中,满信号由写时钟产生,空信号由读时钟产生(√)

解析:写时钟驱动写指针增加,和 FIFO 有效数据的增加,有效数据到达深度时满信号拉高;

读时钟驱动读指针增加,和 FIFO 有效数据的减少,有效数据为 0 时空信号拉高;

b. 时间精度 100ps

c. 时间单位 100ps

d. 时间精度不确定

解析:10ns 为时间单位,100ps 为时间精度。

时间单位主要用在timescale 定义之后的代码中,直至遇到另一个timescale 指令或`resetall

指令为止,用来表示 verilog 语法中使用到时间的表达式的单位。比如:

and # (5.22, 6.17 ) Al (Z, A, B); 里面的 5.22 和 6.17 分别代表 52.2ns 和 61.7ns

或者 always@(posedge clk) out <= #3 in; 里面的 3 代表 30ns。

时间精度一般体现在波形的时间横轴上,最小的一个时间单位跨度即时间精度 100ps。 -

时序逻辑电路不仅与输入有关,还与原来的状态有关。(√)

-

同步复位需要进行 recovery 和 removal 检查,异步复位不需要进行 recovery 和 removal

检查(×)

解析:recovery 和 removal 存在于拥有 async reset 端口的寄存器,因此异步复位需要做这种

检查。这种检查的目的是为了保证复位释放的时刻能早于时钟沿并且保持到时钟沿到来

6.关于 false path,正确的是(d)

a. 一般异步电路可以设置为 false path

b. 两个不同频率的接口一定可以设置为 false path

c. 一般异步复位可以设置为 false path

d. 一般模拟 ip 和系统的互联接口都可以设置为 false path

解析:

a 是错误的。设置 false path 的原因是该路径没必要满足特定时序(比如

setup/hold,recovery/removal,clock gating,max delay 等特定时序)。虽然异步电路时钟之间

没有固定的相位关系,工具没法直接做 reg‐reg 的 setup/hold 检查,但是可以设置 max delay

等特殊约束对需要满足一定时序关系的异步电路做检查,需要看具体的场景。

b 是错误的。频率不同和 false path 没有任何关系。而异步电路的频率可能不同,但是频率

不同不等于异步电路,异步电路的本质是来自不同晶振的时钟源驱动的电路,他们频率甚至

也可以相同。

c 是错误的。对于异步复位,指的只是寄存器使用了异步复位端口 async_reset,在复位的时

候复位信号可以是异步的。但它在释放的时候是需要满足 recovery‐removal 时序检查的,需

要做同步释放,因为做了同步,所以 STA 工具有能力做检查。所以异步复位不能设为 false

path,需要检查 recovery‐removal 时序。

d 是正确的。模拟 ip 的时钟频率一般远小于数字电路,因此对数字电路的时序不敏感,互联

接口可以设置 false path。

7.下面是一个什么电路:©

always@(posedge clk or negedge rst_n) begin

If(rst_n == 1’b0)

a<=2’b0;

elseif(b>2’b0)

a<= b

end

a. 综合为 latch

b. 带同步复位的 d 触发器

c. 带异步复位的 d 触发器

d. 组合逻辑

解析:posedge clk 决定了这是一个触发器,if(rst_n == 1’b0)和 negedge rst_n 决定了这是一个

异步复位的 d 触发器,复位和时钟无关(异步)。

-

对于信号定于语句:reg[0:4] always,a;说法错误的是(b)

a. 不能使用关键字定义信号名

b. 信号定义为 reg 型,只能使用在时序电路的赋值中

c. bit 定义顺序应该从高到低

d. 每个信号应单独用一行来声明

解析:a 和 c 违背 verilog 语法,是错的。d 只是建议,并不违背 verilog 语法。相比之下,b

是绝对错的,因为 reg 型可以用于组合逻辑赋值,比如 always(*)。 -

下列说法错误的是(d)

a. 条件语句,如果无优先级关系,尽量采用 case,避免多级 else if,影响时序;

b. If/else 语句配对使用,case 语句加 default 项;组合逻辑中在所有条件下都要对信号幅值,

如果要保持步便用 a=a 方式赋值;

c. 两个向量进行比较操作或加减操作或赋值操作时,两个向量的位宽要相等,避免隐式扩

展。

d. 可综合代码中,除了 for 语句中的循环变量可以定义为 integer 型以外,所有变量和信号

都只能为 wire 或 reg 型,不能定义为整型,实数型,无符号型,realtime 型和 time 型。

解析:

a 是正确的,优先级条件语句会综合成串联的选择逻辑,时序较差,而 case 可以综合成并行

的选择逻辑,n 个条件逻辑级数为 log2n。

b 是正确的,但不严谨。if/else 可以不配对使用,在时序逻辑下,可以只有 if 没有 else,这

时候 else 分支保持寄存器原值,当然有 else 使代码更清晰。有 case 语句,如果是组合逻辑,

只要有条件没给赋值,会综合出 latch。

c 是正确的。两个向量位宽不匹配会隐式拓展高位,如果有操作数定义为 wire 类型但是作为

有符号数使用,隐式拓展会错误高位补 0,拓展成无符号数,功能出错。

d 是错误的,integer 可以被定义成信号,会综合出 32bit 的 register。但因为位宽固定,一般

不这么使用。另外在 verilog‐2001 中加入了无符号型和有符号型的 reg/wire 定义,也属于可

综合类型。其他类型不可综合。

10.关于异步设计的危害,下面说法错误的是:(b)

a. 信号的时延随着每次布局布线的不同而不同,随着 pvt 的改变而改变,因此可靠性很差,

而且不容易移植

b. 异步设计会产生毛刺

c. 异步设计不能做静态时序分析

d. 异步设计会带来很大的同步翻转噪声

解析:

a 是正确的。现在大部分的设计都是同步设计,小部分高性能低功耗电路可能会考虑使用异

步设计。异步设计的好处之一便是可以最大限度利用时间窗的 margin。有点类似 latch 的

timeborrow,无需等待同步打拍,并且没有了时钟信号,功耗可以大大降低。坏处是需要特

殊的握手机制来保证时序,而握手机制又很大程度上依赖于信号的时延,像 a 所说,时延不

可控型较强,因此可靠性较差,而且不容易移植。

b 是错的,毛刺并非异步设计导致,即便是同步设计,只要信号传递过程中中间结果和最终

输出不同(卡诺图可以清楚看到),也会有毛刺,只不过异步设计的毛刺比较容易导致功能

错误,因为没有时序检查,没有 setup/hold 来保证毛刺消除。

c 是对的。现在的静态时序分析都是基于同步设计,异步设计没有时钟的概念,所有信号没

有固定的相位关系,工具无法建模分析。

d 是对的。这里的翻转噪声主要来自于信号线之间的耦合电容。如果两个异步信号之间有耦

合电容,那么他们的噪声比同步信号之间大得多,因为他们的电平跳变相互影响的时间窗口

更大。 -

多 bit 总线信号可以通过格雷码转换进行异步处理,例如:8bit 的数据总线进行格雷码

转换,然后通过双触发器法实现异步处理(√)

解析:格雷码将多 bit 的翻转转化为单 bit 的翻转,解决了多 bit 异步信号传播过程中因时延

不同而导致的数据采集端采集信号错误的问题。 -

System Verilog 中,下面哪种数组在使用前需要执行 new 操作(c)

a. 压缩数组

b. 联合数组

c. 动态数组

d. 多维数组

解析:动态数组通过 new()函数预先分配存储空间。 -

电路设计中,只要采用静态时序分析就可以保证电路设计的准确性,不需要再进行动态

时序分析了。(×)

解析:现在大部分的同步电路设计流程都是 rtl 验证+formality 形式验证+sta 静态时序分析。

通过 rtl 验证保证功能完备,通过 formality 保证 rtl 和网表一致性。因为有了 formality 保证

网表和 rtl 的一致性,因此如果 rtl 验证完备,一般情况下就可以保证网表功能验证完备。然

后通过对网表进行静态时序分析(sta)来保证没有时序风险。动态时序分析(后仿)主要是

跑一些典型场景,保证在典型场景下不会有时序问题,增强设计信心,对于同步电路,只要

sta 阶段检查仔细,问题一般不大。但是设计中难免会有一小部分异步电路无法进行静态时

序分析,因此必须需要通过后仿来进行排查。

这篇关于华为海思校园招聘-芯片-数字 IC 方向 题目分享——第二套的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!