本文主要是介绍【学习笔记】3、逻辑门电路,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

3.1 MOS逻辑门电路

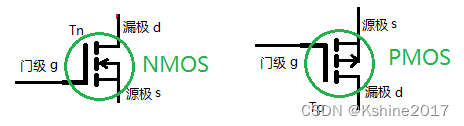

- 按照器件结构的不同形式,分为NMOS、PMOS、CMOS三种逻辑门电路。

3.1.1 CMOS

- CMOS电路成为主导地位的逻辑器件。

- 工作速度:赶上甚至超过TTL电路。(早期CMOS速度慢,后来工艺提升速度变快)

- 功耗和抗干扰能力:远远优于 TTL电路。(功耗低,工作电压宽,抗干扰)

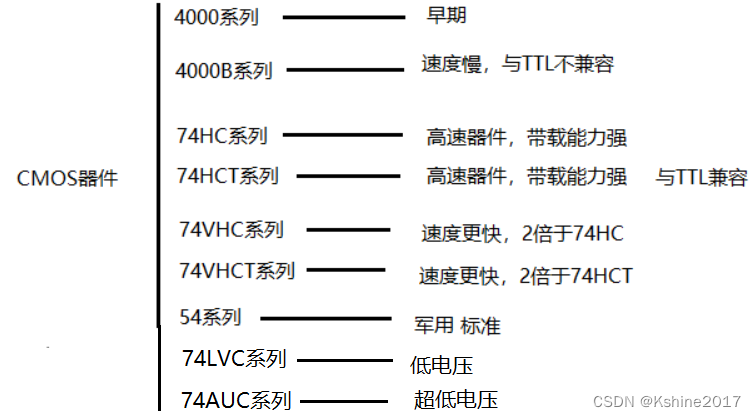

- 下图中,74后面都跟着一个字母C,表示是CMOS。

- CMOS技术不适用于射频和模拟电路中。

- BiMOS是射频系统中用的最多的工艺技术。高速、高驱动、高密度、低功耗、低成本。既可以用于数字电路,又可以用于模拟集成电路。

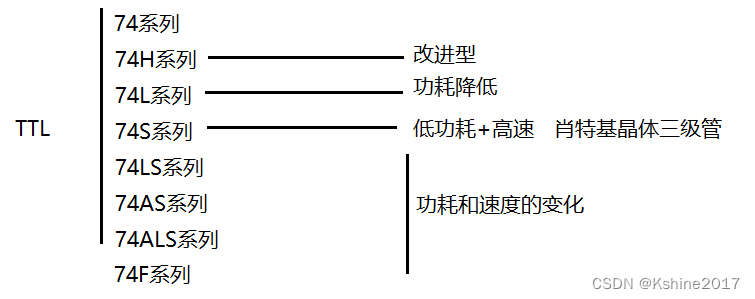

- 双极型数字集成电路TTL和ECL。

- TTL(晶体三极管+肖特基二极管)应用最早,目前一些小规模到中规模的数字系统仍采用TTL技术。低功耗和高速TTL器件(肖特基二极管BSD)。

- ECL(差分对管)不工作在饱和区,工作速度极高。功耗大,不合适做大规模集成电路。应用于高速或者超高速数字系统或设备中。

- 砷化镓是新型半导体材料。工作速度比硅器件快得多。功耗低、抗辐射。应用于光纤通信、移动通信、全球定位等等。

3.1.2 逻辑电路的一般特性

- 生产厂家提供的数据手册中,电压传输特性 v 1 − v 0 v_1 - v_0 v1−v0包括:

(1)输入输出的高低电压

(2)噪声容限

(3)传输延迟时间

(4)功耗

(5)延迟-功耗积

(6)扇入数与扇出数。

3.1.3 MOS开关及其等效电路

- MOS管用于有触点的“断开”和“闭合”。

- 速度与可靠性比机械开关优秀很多。

1. MOS的开关作用

-

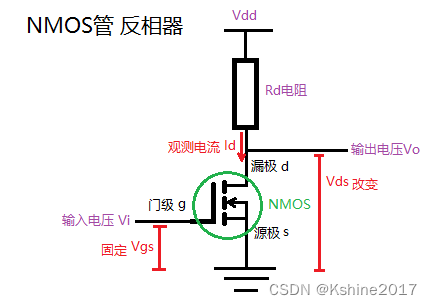

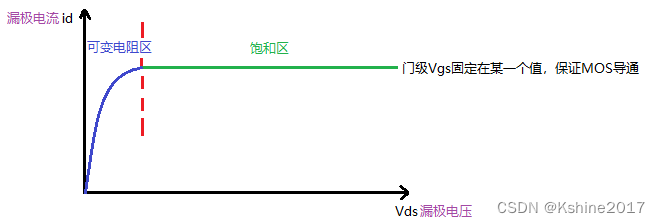

MOS管是一种“压控晶体管”。固定(门级)的电压Vgs,通过改变漏极和源极的电压Vds,观测通过漏极的电流Id。

-

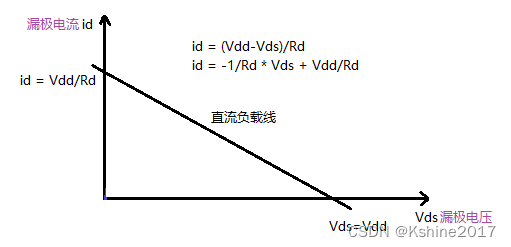

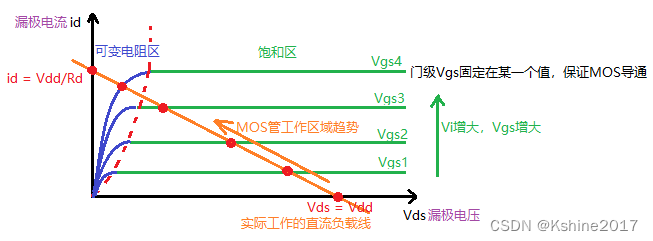

绘制“直流负载线”。

-

通过负载电阻Rd的电流id与Vds之间的关系(仅针对当前电路)。

-

绘制“伏安特性曲线”。

-

门级存在一个固定的电压值Vgs,大于开启电压Vt,保证mos管的导通。

-

流经MOS管的电流id。

-

漏极与源极之间的电压差Vds。

-

在“可变电阻区”内,Vds变大,电流Id也变大,电流Id变化趋势逐渐变缓慢。可知在这个过程中,MOS的内阻逐渐变大。

-

在“饱和区”内,Vds变大,电流饱和,不再变大。

-

已知固定Vgs时,Id-Vds存在上述图中的变化关系。

-

在这个基础上,改变Vgs,可以绘制出如下的图。

-

总结

(1)当门级输入电压Vgs<开启电压Vt时,MOS处于截止状态。 I d = 0 I_d = 0 Id=0, V o = V d s = V d d V_o = Vds = Vdd Vo=Vds=Vdd。

(2)当门级输入电压Vgs>开启电压Vt时,MOS处于导通状态。

随着 V g s Vgs Vgs的变大,MOS管的工作趋势,从饱和区向可变电阻区变化。

当 V g s Vgs Vgs门级输入电压非常大时,MOS管工作在可变电阻区,MOS的内阻趋向于非常小。负载 R d R_d Rd远大于此时的MOS管内阻。

根据串联分压,可知 V g s Vgs Vgs无线趋向于0V。此时电流 I d = V d d / R d I_d = Vdd /R_d Id=Vdd/Rd。 -

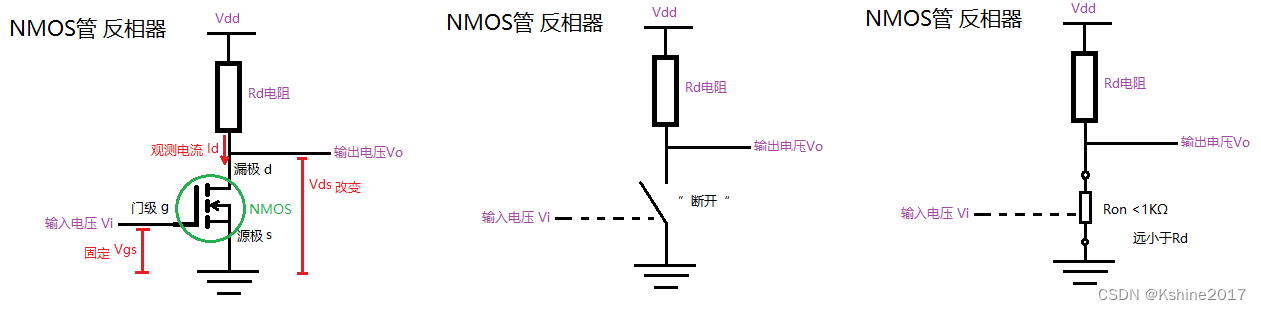

等效电路

在上述电路中,MOS管相当于一个由 V G S V_{GS} VGS控制的无触点开关。

当输入为低电平时,MOS管截止,“断开”,输出高电平。

当输入为高电平时,MOS管在可变电阻区,“闭合”,输出低电平。

2. MOS管的开关特性

- MOS管的栅极g(门级g)与衬底b之间存在电容。

- MOS管的漏极d与衬底b之间存在电容。

- MOS管的栅极g(门级g)与漏极d之间存在电容。

- MOS管导通时存在导通电阻。

- 由于上述等原因,MOS管的实际输出电压与理想的输入电压进行比较,输出电压上升沿和下降沿变化存在滞后性。也就是响应时间。

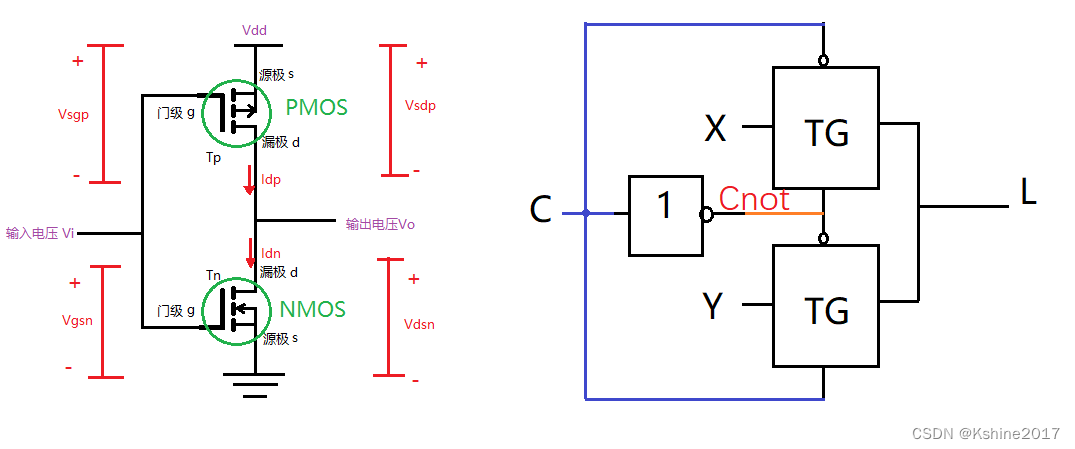

3.1.4 CMOS反相器(非门)

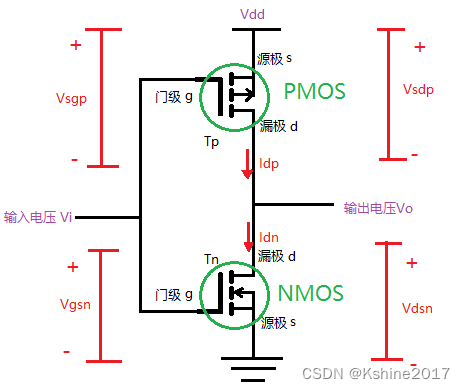

- 模拟电路中的知识:由N沟道和P沟道两种MOSFET组成的电路,成为互补MOS电路 或者 CMOS电路。

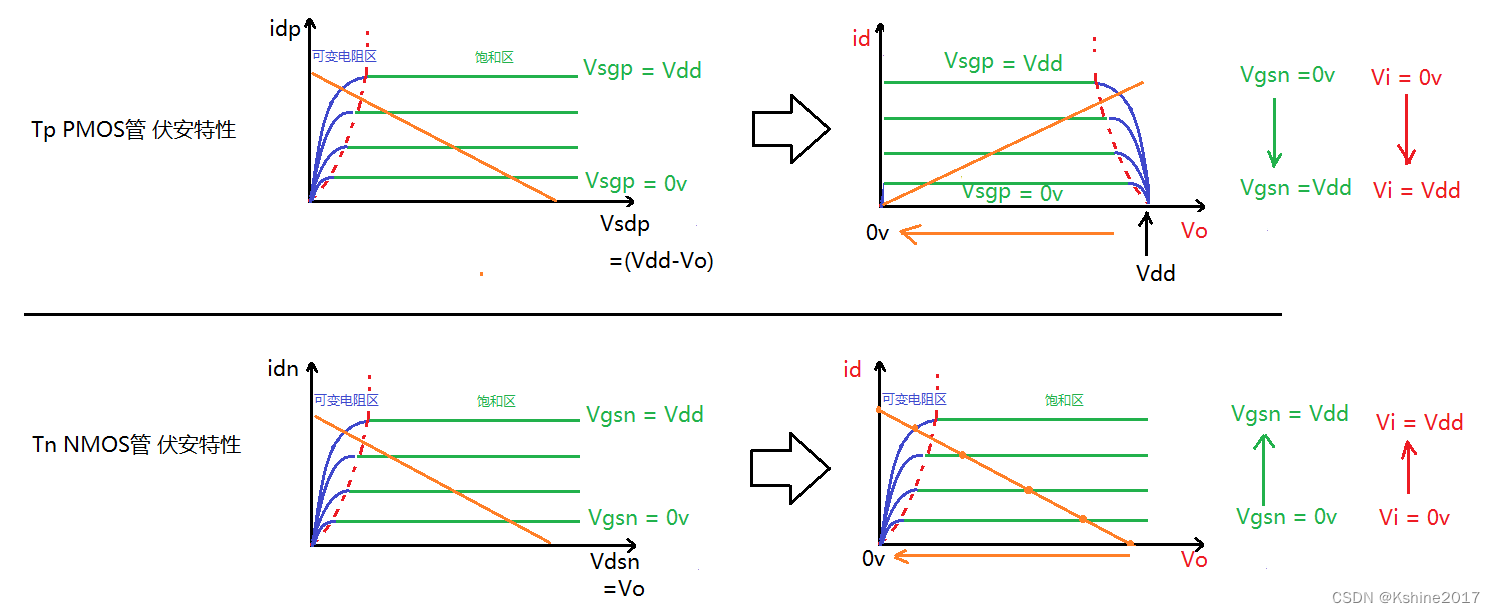

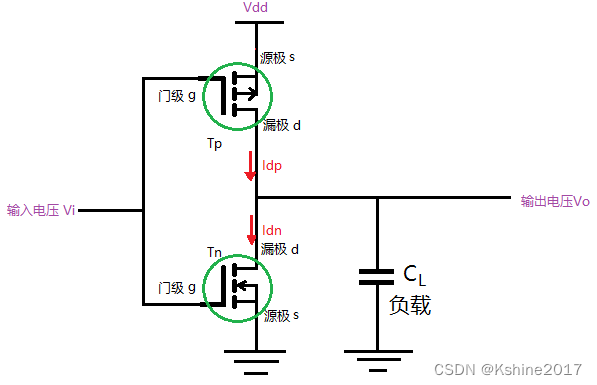

- 下图为CMOS反相器电路。其中电源电压必须大于两个MOS的开启电压之和( V D D V_{DD} VDD > ∣ V T P ∣ |V_{TP}| ∣VTP∣+ V T N V_{TN} VTN)。

- V I = V G S N V_I = V_{GSN} VI=VGSN,NMOS的栅级电压值

- V O = V D S N V_O = V_{DSN} VO=VDSN,NMOS的漏极电压值

- i D N = i D P = i D i_{DN} = i_{DP} = i_D iDN=iDP=iD

1. 工作原理

- 当 V I = 0 V V_I = 0V VI=0V(逻辑0), T N T_N TN NMOS管截止, T P T_P TP PMOS管导通(可变电阻区)。 V O = V D D V_O = V_{DD} VO=VDD。此时通过两管的电流,为通过 T P T_P TP PMOS管的电流, i D P i_{DP} iDP非常小,总的功耗小。

- 当 V I = V D D V_I = V_{DD} VI=VDD(逻辑1), T N T_N TN NMOS管导通(可变电阻区), T P T_P TP PMOS管截止。 V O = 0 V V_O = 0V VO=0V(约等于0V,典型值10mv)。此时通过两管的电流,为通过 T N T_N TN NMOS管的电流, i D N i_{DN} iDN非常小,总的功耗小。

- CMOS反相器近似一个理想的逻辑单元。输出电压近似为 V D D 或者 0 V V_{DD}或者0V VDD或者0V。功耗几乎为0。

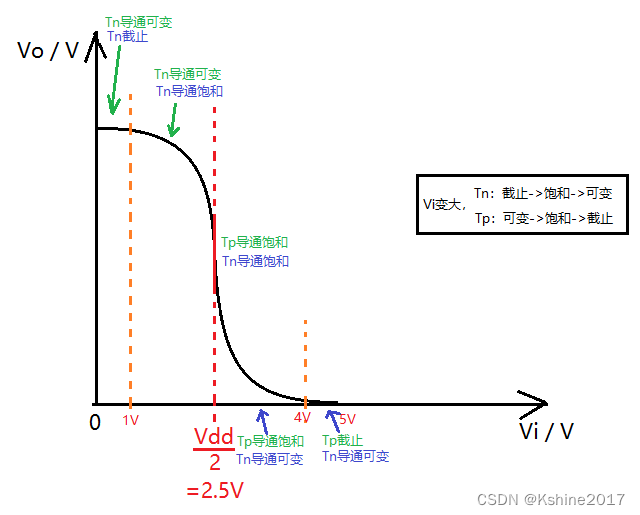

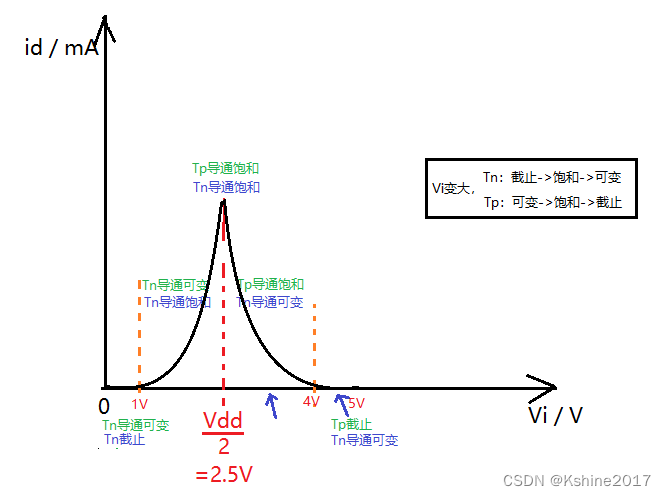

2. 电压传输特性和电流传输特性

-

电压传输特性(输出电压 V O V_O VO与 V I V_I VI的变化关系)。

-

由下图可知,栅极电压较大时,MOS处于导通可变电阻区,彻底导通,相当于一根闭合导线。栅极电压很小时,MOS处于截止区,相当于断开。

-

电流传输特性。

-

在 V I = V D D / 2 = 2.5 V V_I = V_{DD}/2=2.5V VI=VDD/2=2.5V处,电流最大,功耗最大。危害mos管。使用时应避免长时间工作在这个状态下。

-

当一个MOS截止,一个MOS导通可变时,电流较小,功耗低。

3. 工作速度

-

CMOS反相器的工作速度(电压值的平均传输延迟时间)大约是10ns,与带负载时的充放电时间有关系。

-

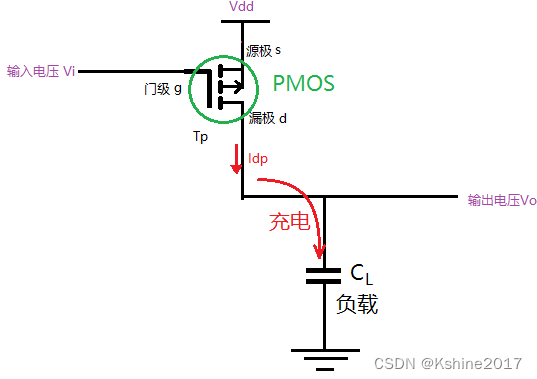

CMOS反相器(或CMOS电路),用来驱动其他MOS器件时,负载的输入阻抗是电容性的。如下图所思,负载被简化成一个电容符号 C L C_L CL。

-

CMOS反相器的输入电压 V i = 0 V_i=0 Vi=0时, T N T_N TN截止, T P T_P TP导通。

-

T P T_P TP的导通电阻很小(工作在可变电阻区)。

-

根据电阻和电容的配合关系,可知充电回路的时间常数较小。

-

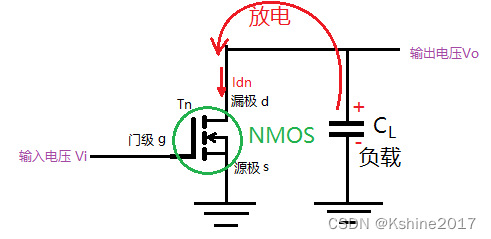

CMOS反相器的输入电压 V i = V d d V_i=V_{dd} Vi=Vdd时, T P T_P TP截止, T N T_N TN导通。

-

T N T_N TN的导通电阻很小(工作在可变电阻区)。

-

根据电阻和电容的配合关系,可知放电回路的时间常数较小。

3.1.5 CMOS逻辑门电路

- 在3.1.4中及介绍的CMOS反相器,为“非门”。

- 拓展可以得到,“与非门”,“或非门”,“异或门”等等。

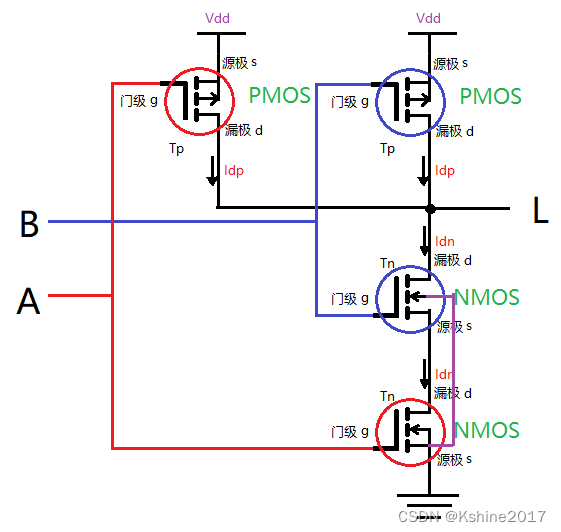

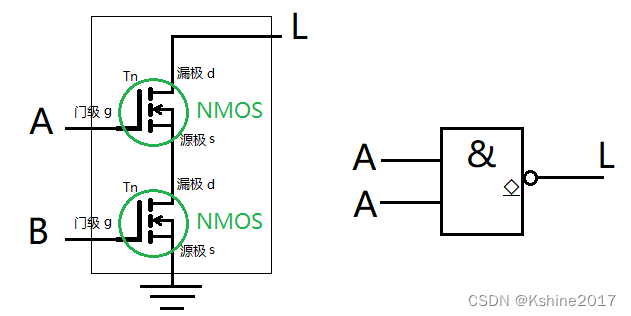

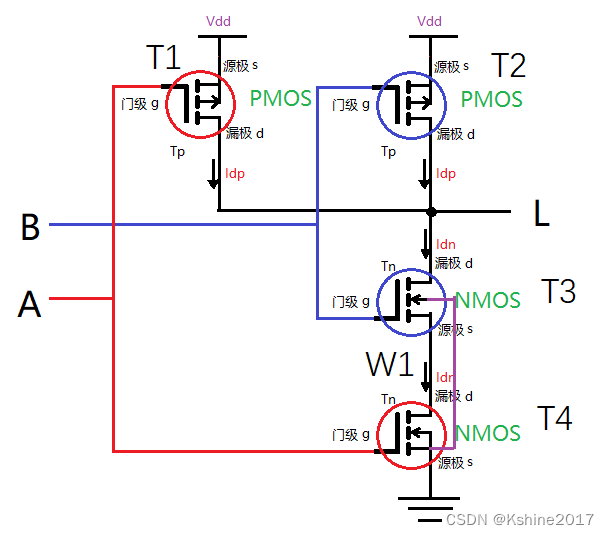

1. 与非门

- 当A和B中出现低电平( A = = 0 ∣ ∣ B = = = 0 A==0||B===0 A==0∣∣B===0),两个串联的NMOS支路一定是截止,两个并联的PMOS一定有导通的支路,最终输出高电平 L = 1 L=1 L=1。

- 当A和B同时高电平( A = = 1 & & B = = = 1 A==1\&\&B===1 A==1&&B===1),两个串联的NMOS支路同时导通,两个并联的PMOS同时截止,最终输出低电平 L = 0 L=0 L=0。

- L = A ⋅ B ‾ L = \overline{A · B} L=A⋅B

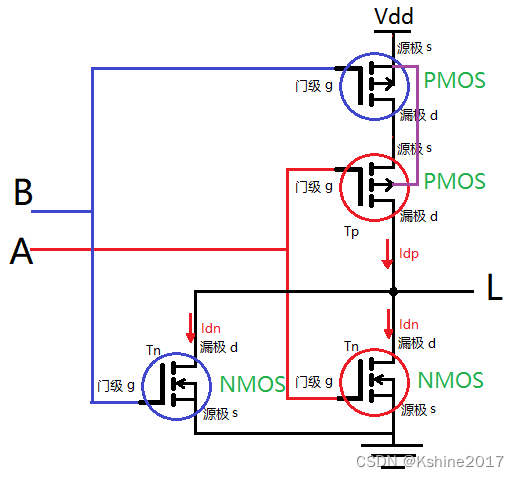

2. 或非门

- 当A和B中出现高电平( A = = 1 ∣ ∣ B = = = 1 A==1||B===1 A==1∣∣B===1),两个并联的NMOS支路一定有导通的支路,两个串联的PMOS一定截止,最终输出高电平 L = 0 L=0 L=0。

- 当A和B同时低电平( A = = 0 & & B = = = 0 A==0\&\&B===0 A==0&&B===0),两个并联的NMOS支路同时截止,两个串联的PMOS同时导通,最终输出低电平 L = 1 L=1 L=1。

- L = A + B ‾ L = \overline{A + B} L=A+B

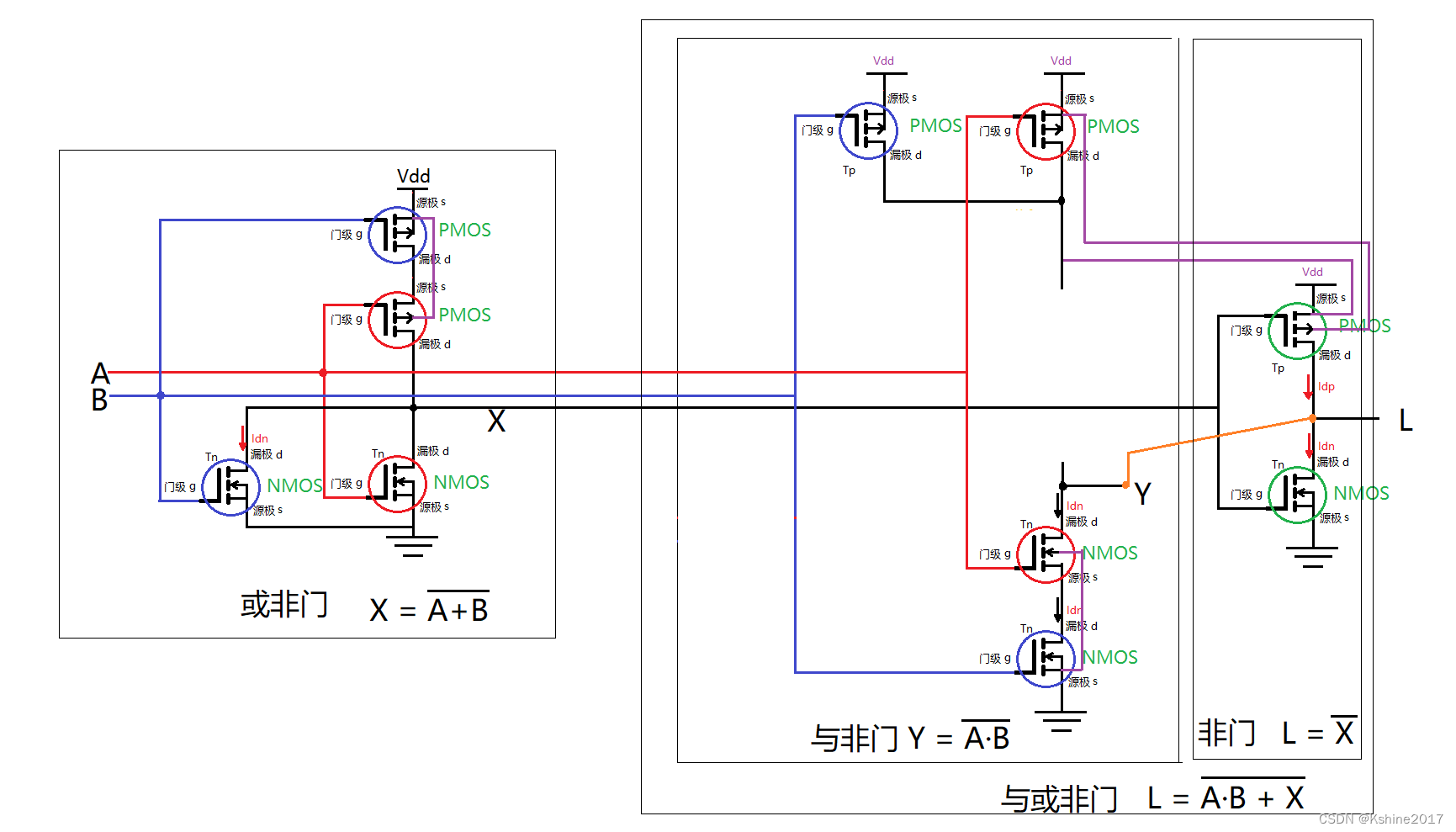

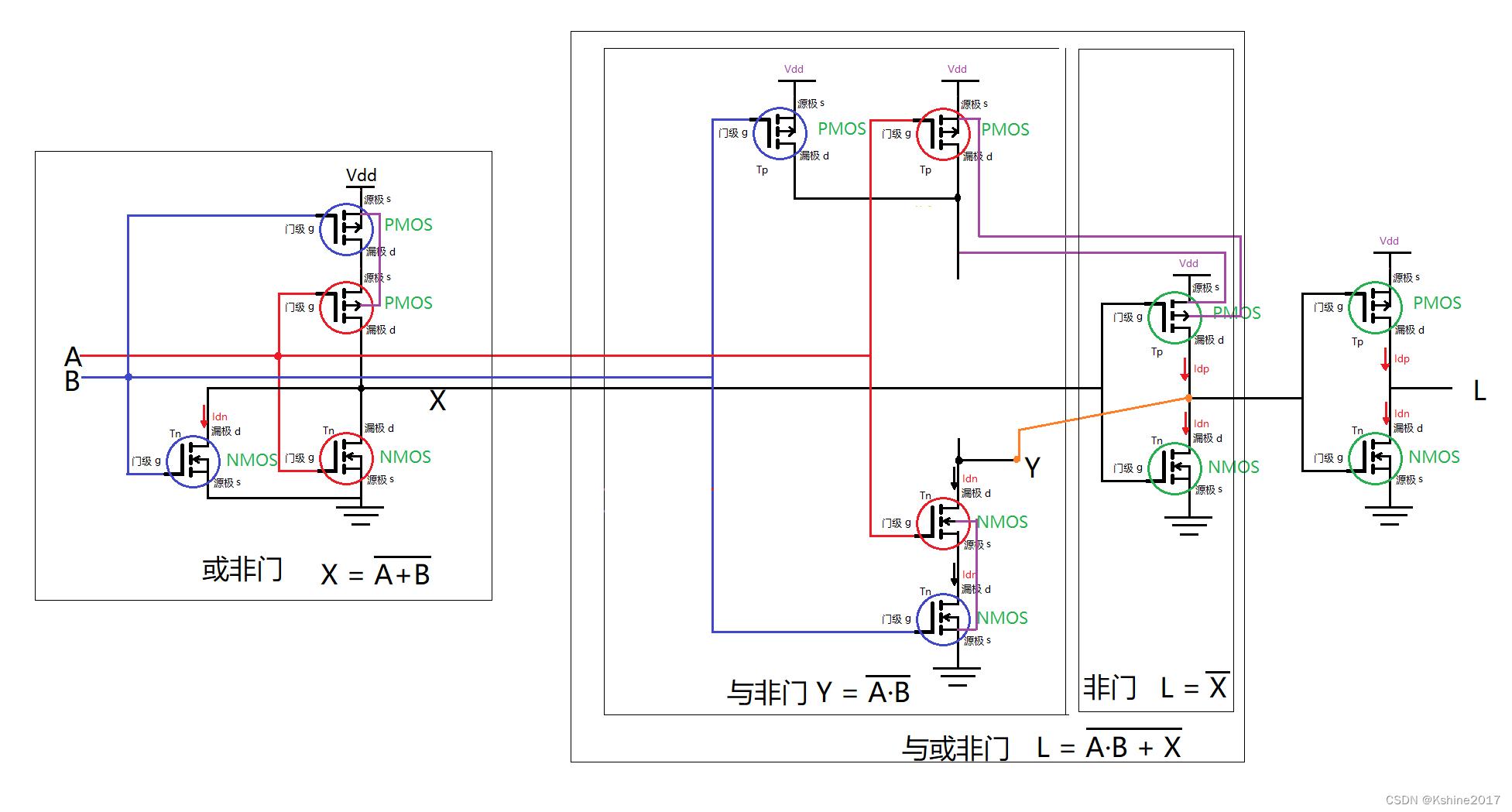

3. 异或门

- L = A ⋅ B + X ‾ = A ⋅ B + A + B ‾ ‾ = A ⋅ B + A ‾ ⋅ B ‾ ‾ = A ⊙ B ‾ = A ⊕ B L = \overline{A·B+X} = \overline{A·B+\overline{A+B}} = \overline{A·B+\overline{A}·\overline{B}} =\overline{A⊙B}=A⊕B L=A⋅B+X=A⋅B+A+B=A⋅B+A⋅B=A⊙B=A⊕B

4. 同或门

- 在异或门的后面增加一个非门,就构成了“异或非门”,也就是同或门。

- L = A ⋅ B + A ‾ ⋅ B ‾ = A ⊙ B L =A·B+\overline{A}·\overline{B} =A⊙B L=A⋅B+A⋅B=A⊙B

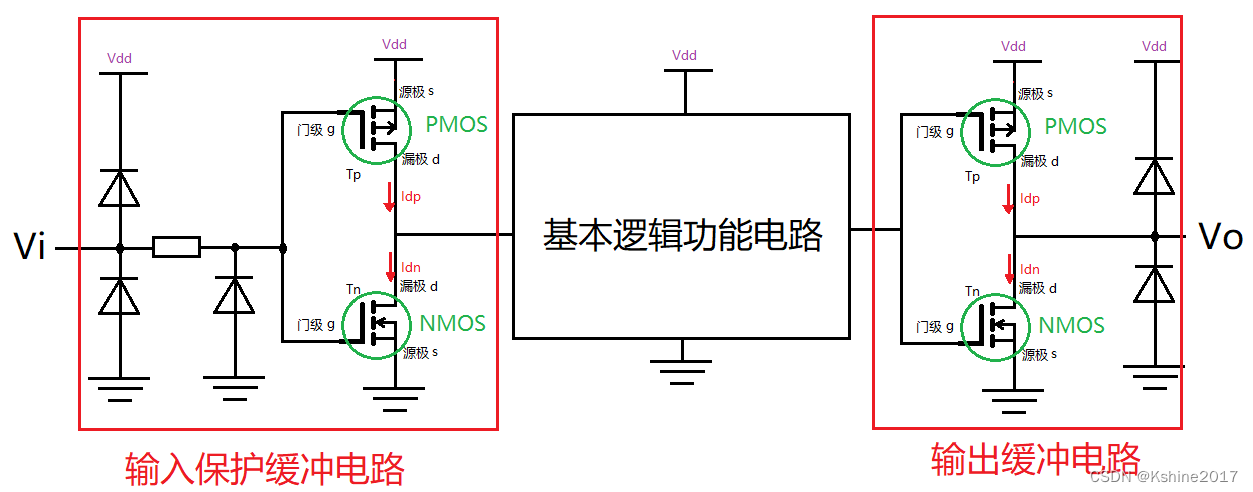

5. 输入、输出保护电路和缓冲电路

- 输入保护缓冲电路和输出缓冲电路,用于隔离外部与基本逻辑功能电路。

- 提供稳定的输入特性和输出特性。输入输出不会受到内部逻辑影响。

(1)输入保护缓冲电路。 - 输入缓冲电路是指CMOS反相器,栅极与沟道之间很薄,易被击穿。

- 输入保护电路是指二极管保护电路,二极管的反向击穿电压30V,小于缓冲电路栅极SiO2层的击穿电压。二极管反向击穿后,会限制MOS管栅极的电位,起到保护作用。

- 过冲时间较短时,二极管可以恢复正常。

- 过冲时间较长时,二极管会损坏。

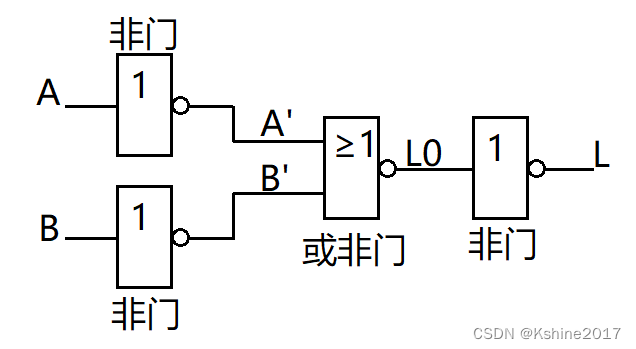

(2)缓冲电路。 - 因为增加了输入和输出的缓冲电路,电路的逻辑功能也发生了变化。

- 具体举例如下图:原本为“或非门”的逻辑电路,在输入和输出端都增加了缓冲电路非门,导致逻辑功能变成了“与非门”。

- L 0 = A ′ + B ′ ‾ L0 = \overline{A' + B'} L0=A′+B′

- A ′ = A ‾ A' = \overline{A} A′=A

- B ′ = B ‾ B' = \overline{B} B′=B

- L = L 0 ‾ = A ′ + B ′ ‾ ‾ = A ‾ + B ‾ ‾ ‾ = A ⋅ B ‾ L=\overline{L0} = \overline{\overline{A' + B'}} =\overline{\overline{\overline{A}+\overline{B}}}=\overline{A·B} L=L0=A′+B′=A+B=A⋅B

3.1.6 CMOS漏极开路门和三态输出门电路

- 输出端的两种输出结构:漏极开路门(OD)和三态输出门(TSL)。

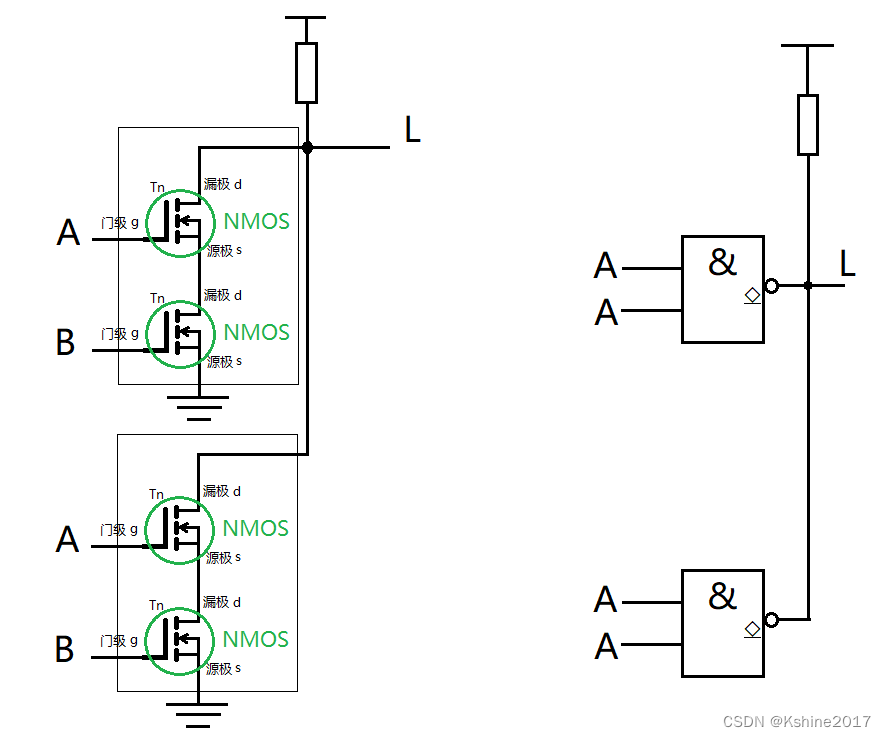

1. 漏极开路门电路“ ◇ ‾ \underline{◇} ◇”(OD)

- 应用场景,不同输出端,需要进行“并联”(线与)。

- 避免出现,不同输出端并联时,高电平和低电平直连,导致电流过大,损坏器件。

- 漏极开路是指,输出电路只有NMOS管(S极只能接地,拉低)。

- 输出为漏极开路的“与非门”,如下图所示。

- 输出端“线与”。

- 上拉电阻的大小会影响OD门的开关速度。电阻越小,充电时间越小,开关速度越快。

- 上拉电阻不能取得太小,需要保证电流不超过允许的最大值。上拉电阻最小值的计算,在书中有简要记载。

- 上拉电阻不能取得太大,会影响工作速度。当工作速度较快时,应避免使用OD门,驱动大电容的负载。

- 门电路在从低电平转为高电平时,OD门比CMOS门慢的多。因为上拉电阻比PMOS管导通时的电阻大的多。

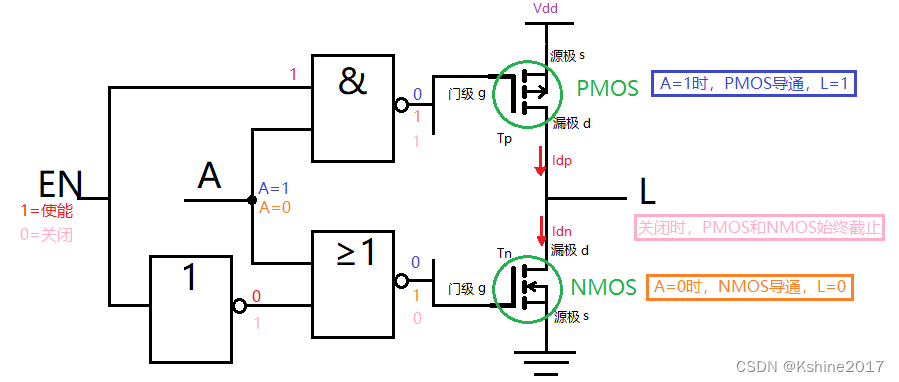

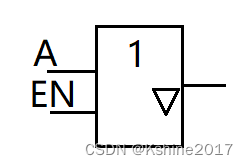

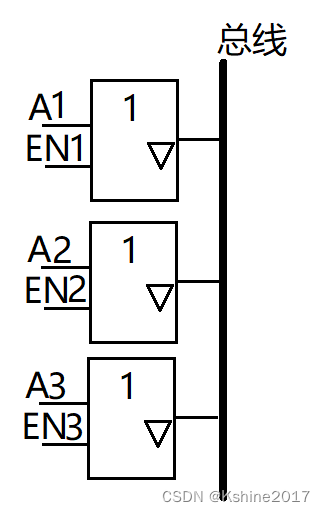

2. 三态输出门电路“▽”

- 应用场景,为了保持“推挽式”输出端的优点,且满足“线与”连接的需要,可以使用三态输出门电路。

- 三态输出门电路,包括“高电平”、“低电平”、“高阻态”(禁止态)。

- 当使能 E N = 0 EN=0 EN=0时,A不能影响PMOS和NMOS的栅极电压,PMOS和NMOS始终处于截止状态。电路出现开路,高阻态。

- 当使能 E N = 1 EN=1 EN=1时,A值的非值 A ‾ \overline{A} A,会传递到CMOS反相器的两个MOS管上,“负负得正”。此时 L = A L=A L=A。

- 三态门的逻辑符号。

- 三态输出门电路,主要用于总线传输。

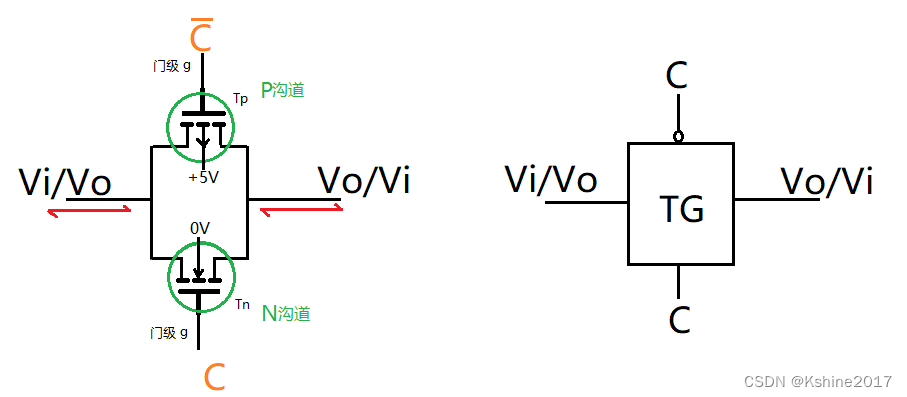

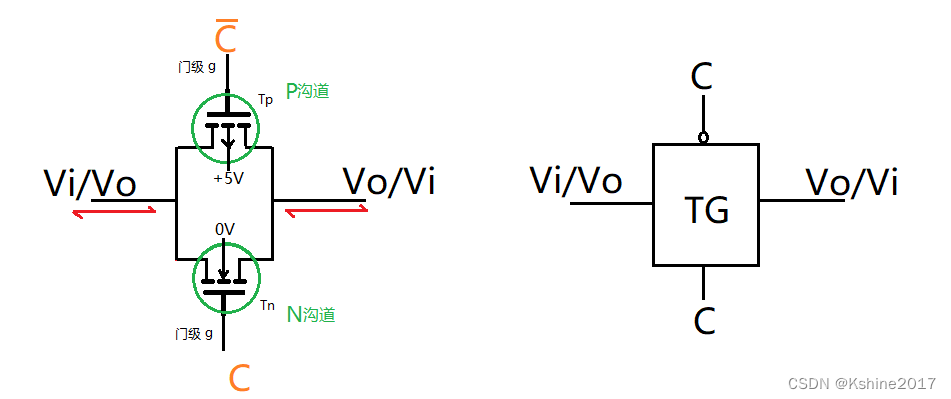

3.1.7 CMOS传输门(TG)

- Transmission Gate。

- 作为基本单元电路,可用于数字信号的传输。

- 传输门又被称为“模拟开关”。可应用于“取样-保持电路”、“斩波电路”、“模数和数模转换电路”等等。

- CMOS传输门,由一个P沟道(左右对称,漏极源极可互换)和一个N沟道(左右对称,漏极源极可互换),并联而成。

- MOS的衬底接-5V,+5V。输入信号的范围是-5V到+5V。

- MOS的衬底接0V,+5V,输入信号的范围是0V到+5V。

- C = 0 V , C ‾ = 5 V C=0V,\overline{C}=5V C=0V,C=5V时,传输门断开。

- C = 5 V , C ‾ = 0 V C=5V,\overline{C}=0V C=5V,C=0V时,传输门的栅极电压OK。当 V i V_i Vi在0到5V时,至少有一个管导通。实现传递。

- 传输门的优点,传输延迟时间短,结构简单。

- 传输门的优点,由于互补作用的两管并联在一起,传输门的导通电阻的变化较小(一个变小一个变大,相互抵消)。

- 导通电阻一般在几百欧以内。

- 导通电阻的稳定,经过电阻分压,输出电压和输入电压之间成线性关系。

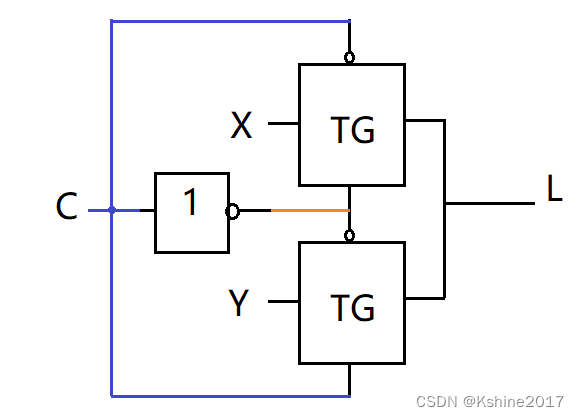

1. 二选一数据选择器

- C=0时,L=X。

- C=1时,L=Y。

3.1.8 CMOS逻辑门电路的技术参数

- 传输延迟时间

- 功耗

- 延时功耗积=传输延迟时间x功耗

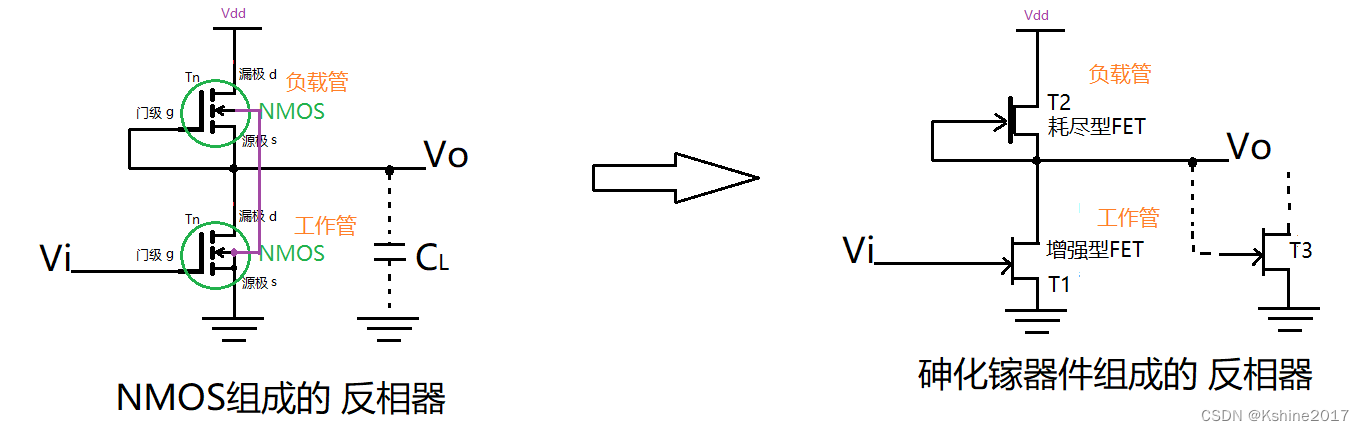

3.1.9 NMOS门电路

-

MOS管发展历史:PMOS->NMOS->CMOS

-

PMOS管,以“空穴”为载流子,空穴迁移率低于电子。

-

NMOS管,以“电子”为载流子,因而NMOS管的速度快于PMOS管。

-

NMOS逻辑门电路,全部使用N沟道MOS。

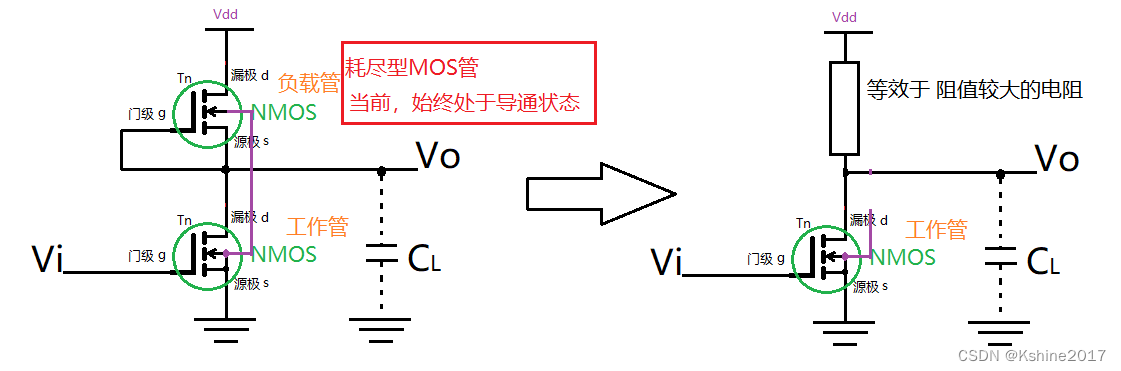

1. NMOS反相器

- NMOS反相器有两个NMOS管,一个是工作管,一个是负载管。

- 工作管为增强型NMOS管。

- 负载管为耗尽型NMOS管。(也可以是增强型)

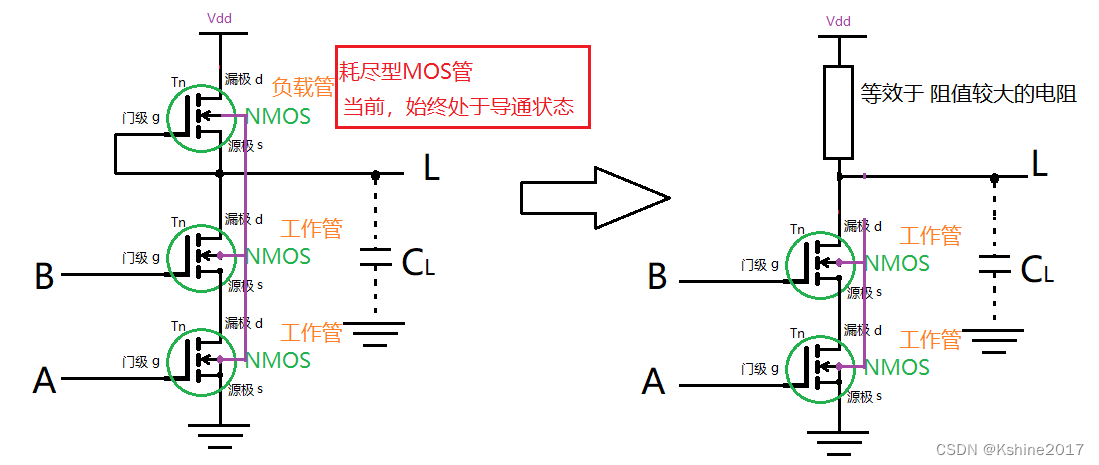

- 下图负载管始终处于导通状态,等效于一个阻值较大的电阻。在集成电路中,考虑到大电阻的体积较大,可以使用MOS管代替电阻。

(1)当 V i = 0 V V_i = 0V Vi=0V时,工作管NMOS截止, V o = 5 V V_o=5V Vo=5V。

(2)当 V i = 5 V V_i = 5V Vi=5V时,工作管NMOS导通, V o ≈ 0 V V_o≈0V Vo≈0V(负载管的阻值远大于工作管的阻值,串联分压)。 - 在 V o − > 5 V V_o->5V Vo−>5V时,负载NMOS管等效的电阻阻值在变小,为 C L C_L CL充电的电流较大,因而充电的时间短。

- 耗尽型负载管NMOS电路的开关速度比较快。

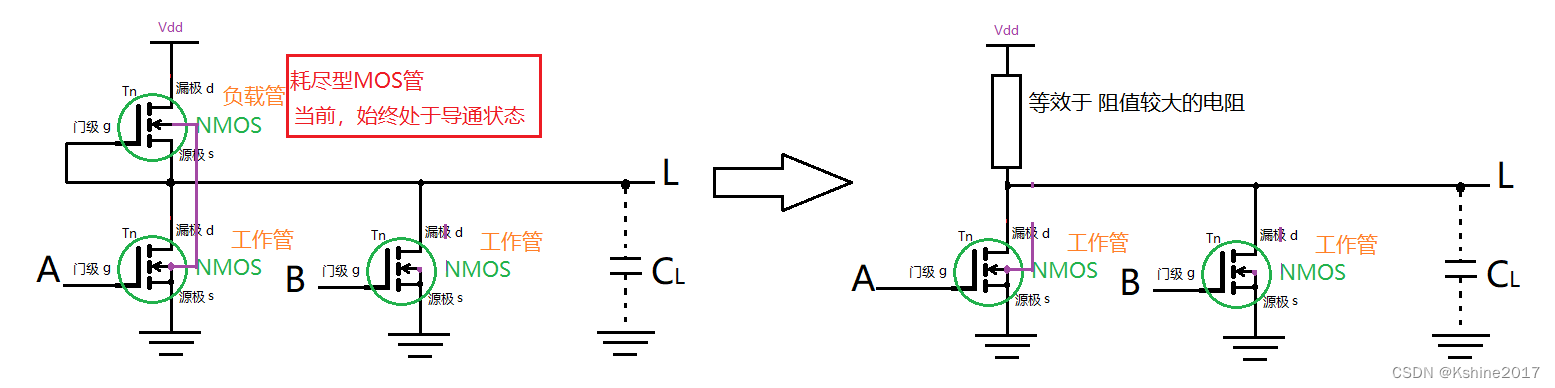

2. NMOS与非门电路

-

NMOS与非门,基于NMOS反相器,在“非门”上加个“与”,即串联。

-

负载管仍然始终处于导通状态,充当大电阻的作用。

-

下面用0表示0V,1表示Vdd。

(1)当 A = 0 ∣ ∣ B = 0 A= 0||B=0 A=0∣∣B=0时,工作管支路NMOS截止, L = 1 L=1 L=1。

(2)当 A = 1 & & B = 1 A= 1\&\&B=1 A=1&&B=1时,工作管NMOS导通, L = 0 L=0 L=0(负载管的阻值远大于工作管的阻值,串联分压)。 -

在 L − > 1 L->1 L−>1时,负载NMOS管等效的电阻阻值在变小,为 C L C_L CL充电的电流较大,因而充电的时间短。

-

耗尽型负载管NMOS电路的开关速度比较快。

3. NMOS或非门电路

- NMOS或非门,基于NMOS反相器,在“非门”上加个“或”,即并联。

- 负载管仍然始终处于导通状态,充当大电阻的作用。

- 下面用0表示0V,1表示Vdd。

(1)当 A = 0 & & B = 0 A= 0\&\&B=0 A=0&&B=0时,工作管全部NMOS截止, L = 1 L=1 L=1。

(2)当 A = 1 ∣ ∣ B = 1 A= 1||B=1 A=1∣∣B=1时,工作管NMOS导通, L = 0 L=0 L=0(负载管的阻值远大于工作管的阻值,串联分压)。 - 在 L − > 1 L->1 L−>1时,负载NMOS管等效的电阻阻值在变小,为 C L C_L CL充电的电流较大,因而充电的时间短。

- 耗尽型负载管NMOS电路的开关速度比较快。

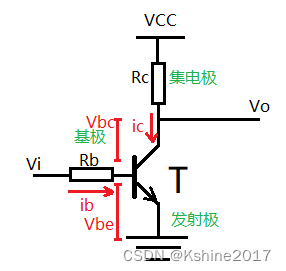

3.2 TTL逻辑门电路

- 三极管:NPN型和PNP型

- 三极管:基极B,集电极C,发射极E

3.2.1 BJT的开关特性

1. BJT开关的作用

- 与CMOS不同,BJT以电流为分析依据。

- 基极的电流 i b i_b ib需要大于阈值,才可以导通三极管。

(1)当 V I = 0 V_I=0 VI=0时, i B ≈ 0 , i C ≈ 0 , V O = V C E ≈ V C C i_B≈0,i_C≈0,V_O=V_{CE}≈V_{CC} iB≈0,iC≈0,VO=VCE≈VCC,(只有很小的电流流过PN结)。

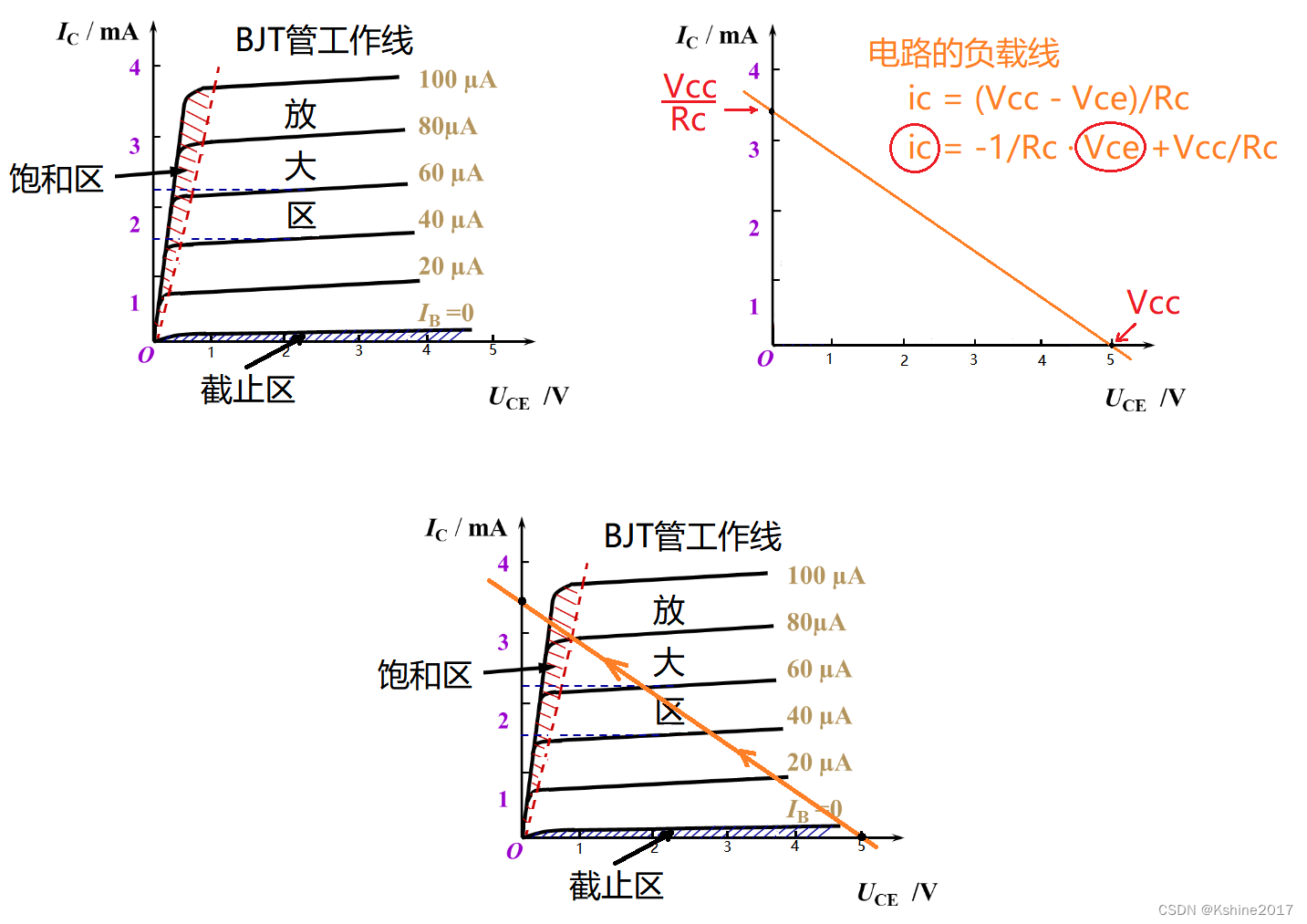

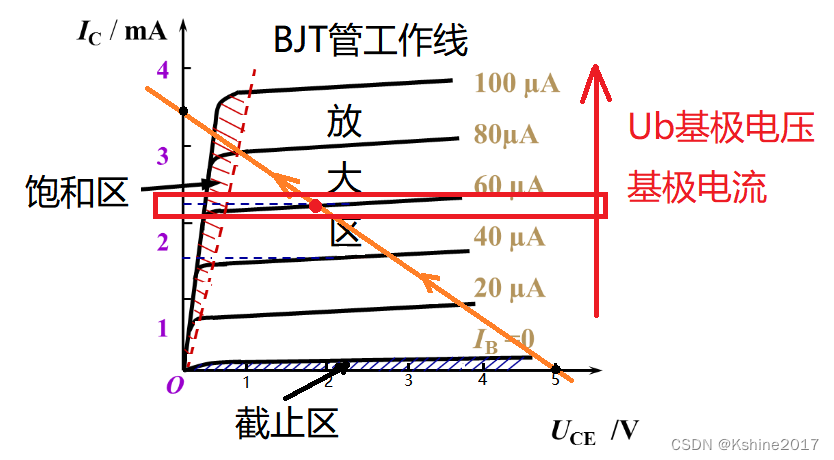

(2)当 V I = 5 V V_I=5V VI=5V时, i B = V C C / ( β R C ) i_B=V_{CC}/(βR_C) iB=VCC/(βRC)电阻与 , i C ≈ 0 , V O = V C E ≈ V C C ,i_C≈0,V_O=V_{CE}≈V_{CC} ,iC≈0,VO=VCE≈VCC,(只有很小的电流流过PN结)。 - 结合BJT管工作线和负载线看,在 i B i_B iB逐渐增大的过程中,允许通过三极管的电流 i C i_C iC越大,三极管工作状态从放大区逐渐变到饱和区。

- 放大区,可以看成是三极管将 i B i_B iB放大为 i C i_C iC。CE间等效电阻阻值可变。

- 饱和区,可以看成是无法继续被线性放大的区域。属于三极管的极限。 CE间等效电阻阻值很小,相当于一个闭合的开关。

2. BJT的开关时间

- BJT开关过程是“饱和区”与“截止区”的转换过程。需要一定的时间才能转换完成。

- 开通,从截止到饱和。需要时间建立基区电荷,以形成饱和电流。

- 关闭,从饱和到截止。基区存储的电荷消散需要时间。

- 提升开关速度的方法:

(1)改进管子的内部构造。减小基区宽度和发射结集电结的面积。

(2)改进外部电路。适当选择正向基极电流,反向基极电流,临界饱和电流。

3.2.2 基本BJT反相器的动态性能

- 影响基本BJT反相器开关速度的原因1:基区内电荷的存入与消散需要一定的时间

- 影响基本BJT反相器开关速度的原因2:基本反相器接电容性负载 C L C_L CL, C L C_L CL的充放电过程需要时间。

- 可见,BJT反相器的开关速度“不理想”。

- 改变电路结构,提升开关速度。

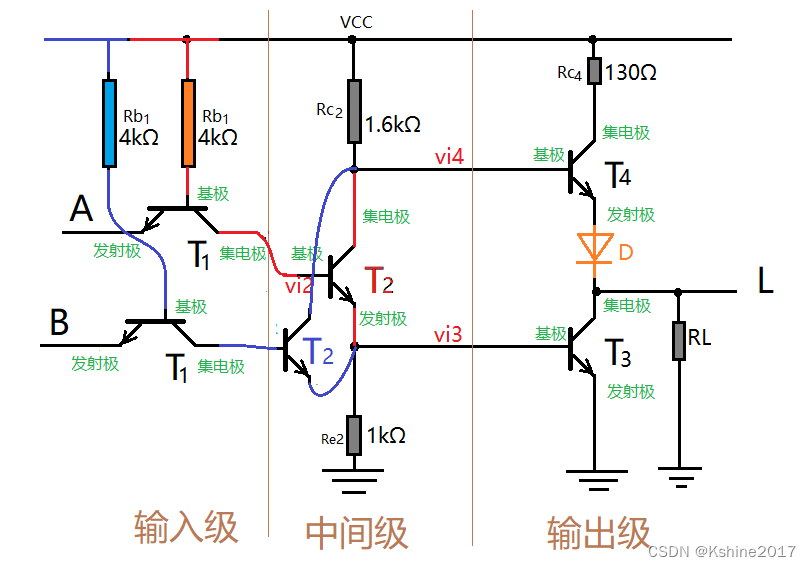

3.2.3 TTL反相器的基本电路

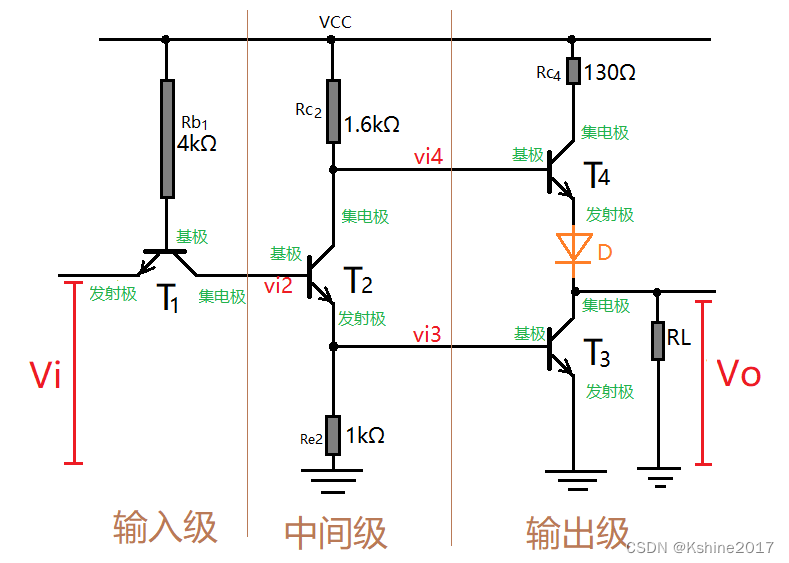

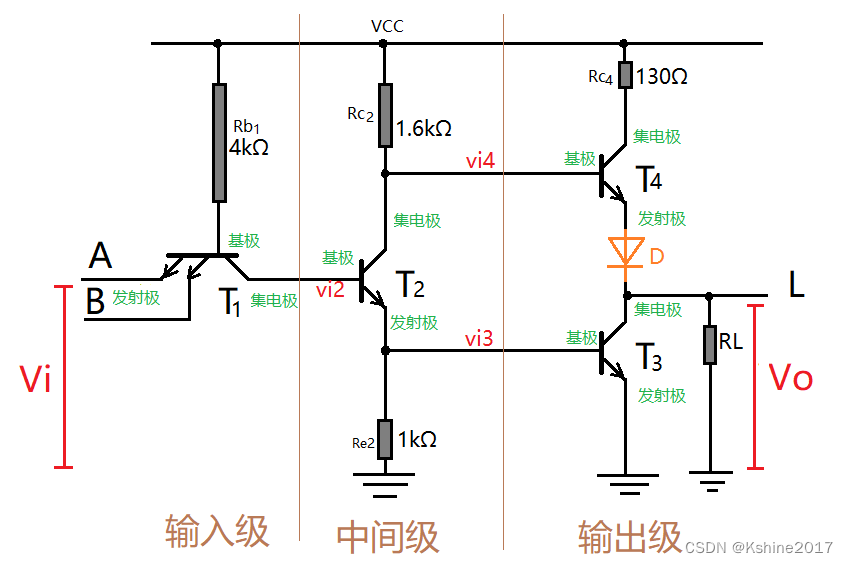

- TTL,晶体管-晶体管逻辑电路(Transistor-Transistor-Logic )

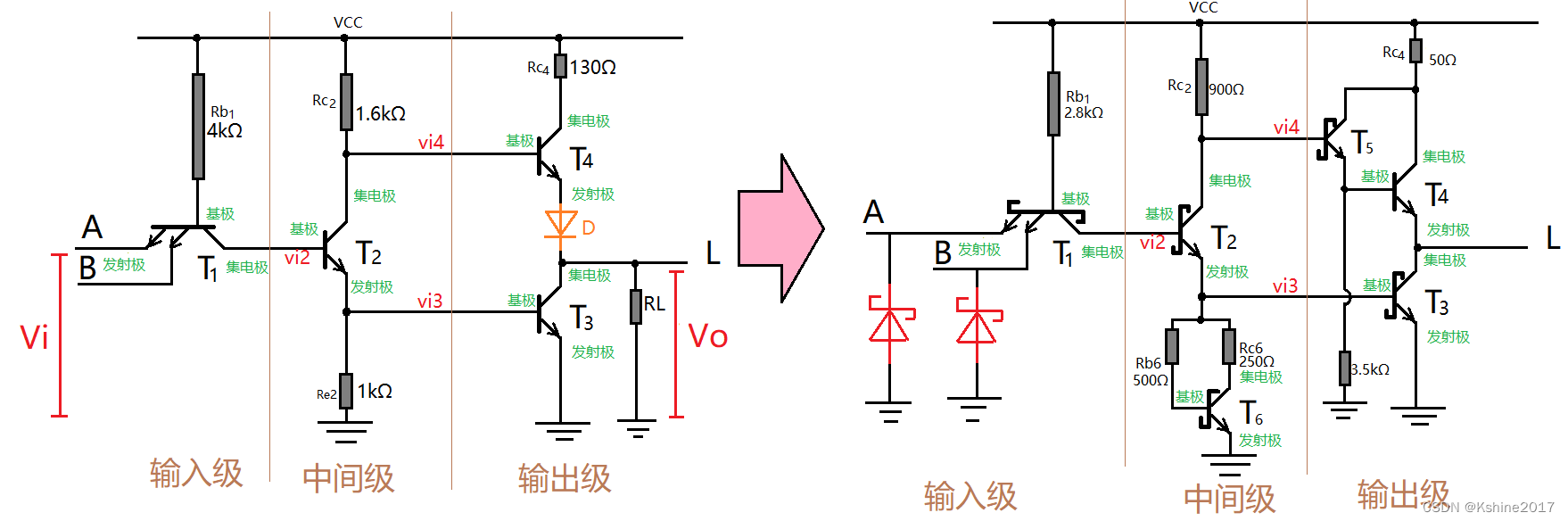

- 由于BJT反相器的开关速度“不理想”,修改电路结构,得到TTL反相器。

- 单端输入信号 V I 2 V_{I2} VI2经过三极管 T 2 T_2 T2转换为互补的双端输出信号 V I 3 V_{I3} VI3和 V I 4 V_{I4} VI4。 T 3 和 T 4 状态相反,一个截止一个导通 T_3和T_4状态相反,一个截止一个导通 T3和T4状态相反,一个截止一个导通

- 输入级:提高工作速度。 T 1 在放大状态和倒置放大状态之间转换, T 2 的电流变化快 T_1在放大状态和倒置放大状态之间转换,T_2的电流变化快 T1在放大状态和倒置放大状态之间转换,T2的电流变化快。

- 输出级:推拉式输出,提高开关速度,增强带载能力。

1. TTL反相器的工作原理

V C C = 5 V V_{CC} = 5V VCC=5V,硅管三极管导通时,电压 V B E = 0.7 V V_{BE}=0.7V VBE=0.7V。集电极和发射极之间的压降实际不可能为0,在0.2~0.3V左右。这里认为 V C E S = 0.2 V V_{CES}=0.2V VCES=0.2V。

(1)当 V I = 0.2 V V_I = 0.2V VI=0.2V低电平时

- V I < 0.4 V 时, T 1 的基极和发射极的压差远远大于开启电压。 V_I<0.4V时,T_1的基极和发射极的压差远远大于开启电压。 VI<0.4V时,T1的基极和发射极的压差远远大于开启电压。

- T 1 导通后,压降 V b e 1 = 0.7 V 。 R b 1 两边的电压 V b 1 > V c c − 0.7 − 0.4 = 3.9 V T_1导通后,压降V_{be1}=0.7V。R_{b1}两边的电压V_{b1}>Vcc-0.7-0.4=3.9V T1导通后,压降Vbe1=0.7V。Rb1两边的电压Vb1>Vcc−0.7−0.4=3.9V,

- T 1 导通后,压降 V c e s 1 = 0.2 V 。 V I 2 = V C 1 < 0.2 + 0.4 = 0.6 V , T 2 截止 T_1导通后,压降V_{ces1}=0.2V。V_{I2}=V_{C1} < 0.2+0.4=0.6V,T_{2}截止 T1导通后,压降Vces1=0.2V。VI2=VC1<0.2+0.4=0.6V,T2截止。

- T 2 截止, T 3 基极电压为 0 , T 3 截止 T_{2}截止,T_3基极电压为0,T_3截止 T2截止,T3基极电压为0,T3截止。

- T 2 截止, T 4 T_{2}截止,T_4 T2截止,T4基极电压为 V B 4 = V C C = 5 V V_{B4}=V_{CC}=5V VB4=VCC=5V(确定的电压值) , T 4 饱和导通(二极管 D 同时也导通) ,T_4饱和导通(二极管D同时也导通) ,T4饱和导通(二极管D同时也导通)。

- T 4 饱和导通, V o = V B 4 − V B E 4 − V D = V C C − 0.7 − 0.7 = 3.6 V 高电平 T_4饱和导通,V_o =V_{B4} - V_{BE4}-V_D = V_{CC} - 0.7-0.7=3.6V高电平 T4饱和导通,Vo=VB4−VBE4−VD=VCC−0.7−0.7=3.6V高电平

(2)当 V I = 3.6 V V_I=3.6V VI=3.6V高电平时

- T 1 的基极和发射极的压差是 5 V − 3.6 V = 1.4 V ,此时 T 1 导通。 T_1的基极和发射极的压差是5V-3.6V=1.4V,此时T_1导通。 T1的基极和发射极的压差是5V−3.6V=1.4V,此时T1导通。

- T 1 导通后,压降 V b e 1 = 0.7 V 。 R b 1 两边的电压 V b 1 = V c c − 0.7 − 3.6 = 0.7 V T_1导通后,压降V_{be1}=0.7V。R_{b1}两边的电压V_{b1}=Vcc-0.7-3.6=0.7V T1导通后,压降Vbe1=0.7V。Rb1两边的电压Vb1=Vcc−0.7−3.6=0.7V,

- T 1 导通后, T 2 基极电压 V B 2 = V I + V C E S 1 > 3.6 V , T 2 饱和导通 T_1导通后,T_2基极电压V_{B2} = V_I+V_{CES1}>3.6V,T_2饱和导通 T1导通后,T2基极电压VB2=VI+VCES1>3.6V,T2饱和导通。

- T 2 导通后,压降 V b e 2 = 0.7 V , T 3 基极电压 V B 3 = V B 2 − 0.7 V > 2.9 V , T 3 导通 T_2导通后,压降V_{be2}=0.7V,T_3基极电压V_{B3}=V_{B2}-0.7V>2.9V,T_3导通 T2导通后,压降Vbe2=0.7V,T3基极电压VB3=VB2−0.7V>2.9V,T3导通。

- T 3 导通后,压降 V b e 3 = 0.7 V , V I 4 = V b e 3 + V c e s 2 = 0.7 + 0.2 = 0.9 V T_3导通后,压降V_{be3}=0.7V,V_{I4} = V_{be3}+V_{ces2} = 0.7+0.2=0.9V T3导通后,压降Vbe3=0.7V,VI4=Vbe3+Vces2=0.7+0.2=0.9V

- V I 4 = 0.9 V 不足以让 T 4 和 D 导通,因而 T 4 和 D 均截止 V_{I4}=0.9V不足以让T_4和D导通,因而T_4和D均截止 VI4=0.9V不足以让T4和D导通,因而T4和D均截止

- T 4 和 D 均截止, V O = V c e s 3 = 0.2 V 低电平 T_4和D均截止,V_O = V_{ces3} = 0.2V低电平 T4和D均截止,VO=Vces3=0.2V低电平。

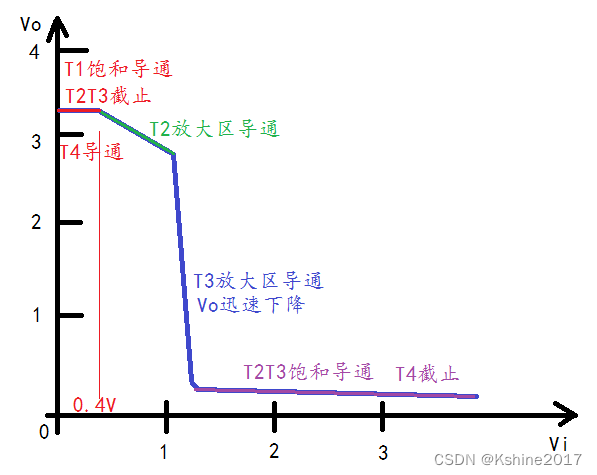

2. TTL反相器的传输特性

- 结合上述工作原理以及下图,可知T3由放大变到饱和的过程,Vo变化的速度最快。

3.2.4 TTL逻辑门电路

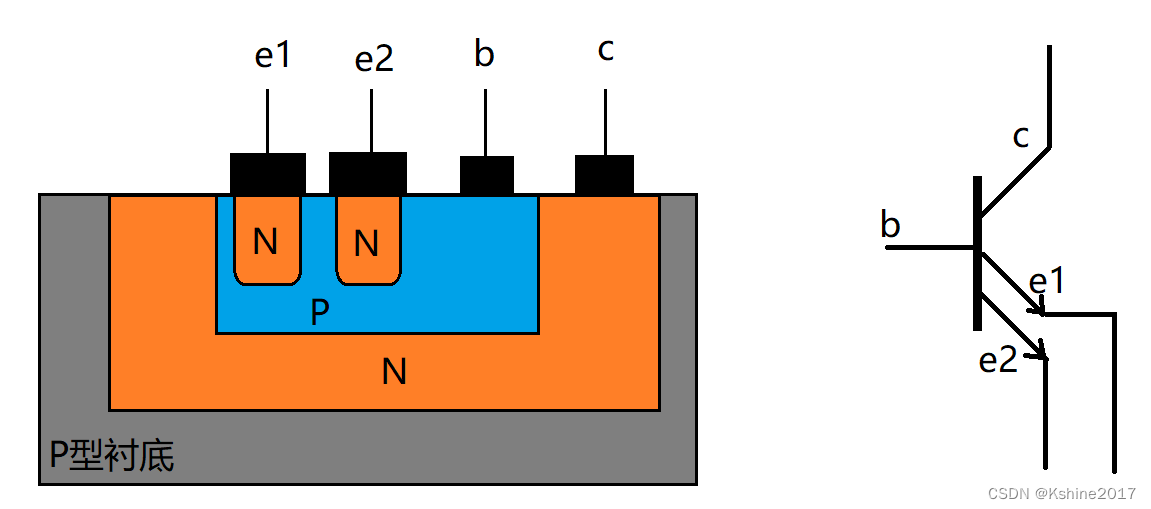

1. 与非门电路

- 多发射极e的NPN三极管。(发射极e,接低电平,用来发射电子)

- 将“TTL反相器”非门的输入级 T 1 T_1 T1,增加一个发射极e,就构成“与非门”电路。$L=V_o=\overline{V_i} =

- A或B任意一个发射极为低电平时, T 1 T_1 T1发射极正偏导通, V B 1 = 0.2 (给定低电平) + 0.7 = 0.9 V V_{B1}=0.2(给定低电平)+0.7=0.9V VB1=0.2(给定低电平)+0.7=0.9V, T 2 T 3 T_2 T_3 T2T3截止, T 4 T_4 T4导通,L为高电平。

- A且B两个发射极都为高电平时, T 1 T_1 T1发射极倒置放大状态, T 2 T 3 T_2 T_3 T2T3饱和导通, T 4 T_4 T4截止,L为低电平。

- L = A ‾ + B ‾ = A ⋅ B ‾ L=\overline{A}+\overline{B} = \overline{A·B} L=A+B=A⋅B

2. 或非门电路

- A和B均低电平时,两路 T 2 T 3 T_2 T_3 T2T3截止, T 4 T_4 T4导通,L为高电平。

- A或B为高电平时,至少有一路 T 2 T 3 T_2 T_3 T2T3饱和导通, T 4 T_4 T4截止,L为低电平。

- L = A ‾ ⋅ B ‾ = A + B ‾ L=\overline{A}·\overline{B} = \overline{A+B} L=A⋅B=A+B

3. 与或非门电路

- 在或非门基础上,为A和B分别增加一个发射极。

- 略。

3.2.5 集电极开路门和三态门电路

1. 集电极开路门电路(OC)

- TTL门电路的输出级,BJT管的集电极为开路状态。

- OC门比OD门,可以承受更高电压和电流。

- 需要外接上拉电阻。

- 参考3.1.6.1的内容。

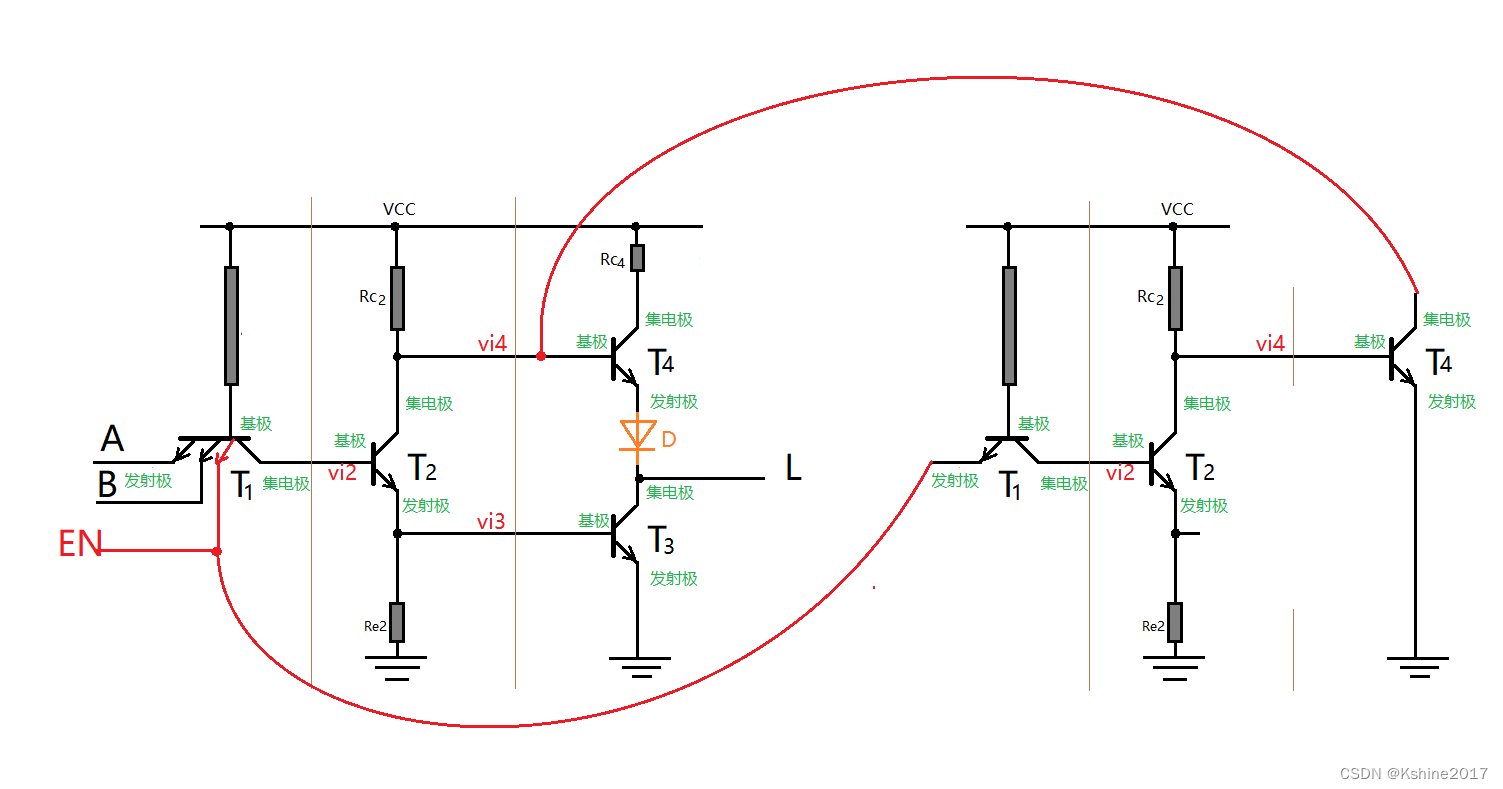

2. 三态(TSL)输出门电路

- 参考3.1.6.2的内容。

- 在普通门电路的基础上,增加控制电路,得到三态输出门电路。

- 即增加一个电路使得 T 3 T 4 T_3T_4 T3T4同时处于截止状态(输出高阻状态,开路状态)。

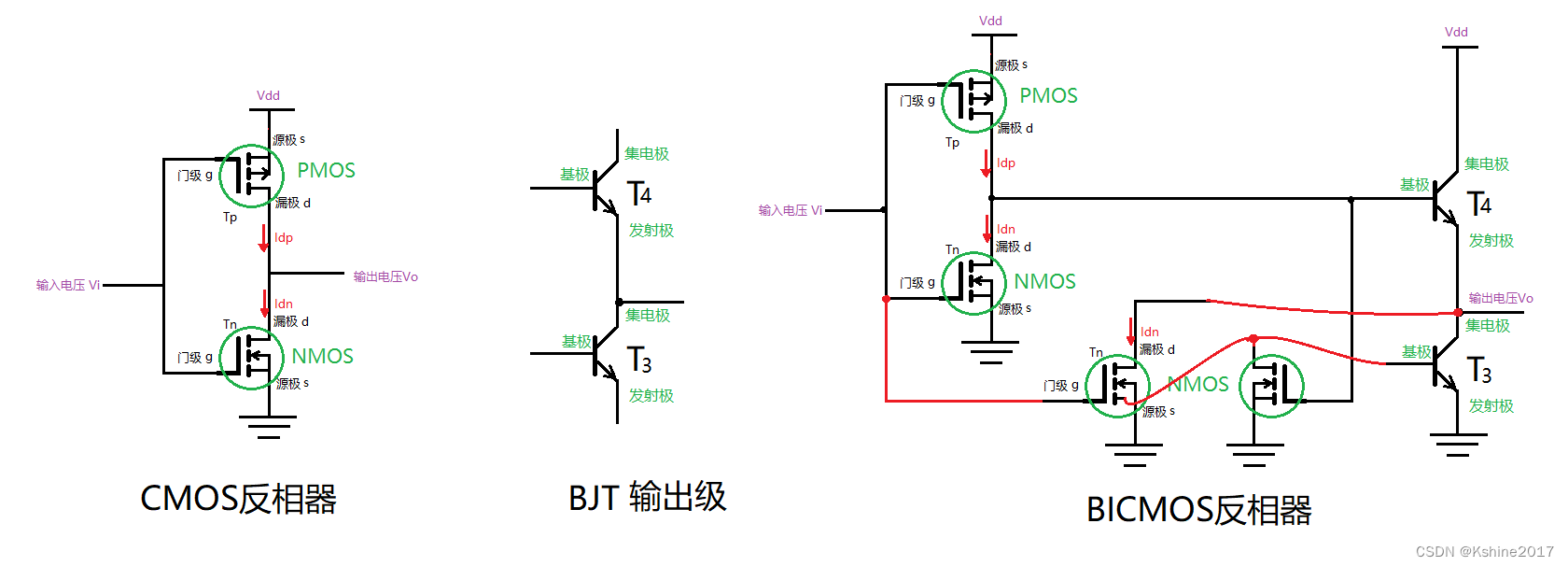

3.2.6 BiCMOS门电路

- 使用双极型BJT管作为CMOS电路的输出级。

- 结合了MOS管的低功耗和双极型管速度快驱动力强的优势。

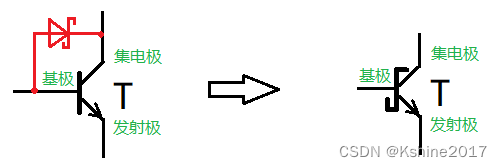

3.2.7 改进型TTL门电路—抗饱和TTL电路

- 为了降低功耗、加快开关速度,对TTL门电路进行改进。

- 改进效果最明显的是抗饱和TTL电路。

(1)抗饱和TTL电路传输速度快,高于一般的TTL电路。

(2)抗饱和TTL电路应用于中小规模集成电路。 - 肖特基系列TTL电路是“抗饱和TTL电路”。

1. 肖特基势垒二极管工作原理

-

肖特基势垒二极管:利用金属和半导体相接触,在交界面形成势垒的二极管。

-

(AL-SiSBD)金属铝+N型硅半导体=>势垒二极管

(1)单向导电性。从硅到铝。

(2)AL-SiSBD导通阈值电压低。约0.4V~0.5V。

(3)势垒二极管从正向导通到反向截止,没有内部电荷建立和消散的过程。转换速度快。 -

利用肖特基二极管抑制BJT的饱和深度。

-

当BJT集电结的正向偏压达到SBD的导通阈值电压时,二极管先导通,将三极管的集电极正向偏压钳制在0.4V。

-

电流继续增大时,一部分电流流过肖特基二极管,流向集电极。不会使BJT的基极电流太大。三极管始终工作在放大区。允许集电极到发射极的电流更大。基极电流小,基极电荷存储与消散时间快。

-

起到抗饱和的功能。电路的开关时间大为减短。

2. 肖特基TTL电路

- TTL与非门, T 1 T 2 T 3 T_1T_2T_3 T1T2T3工作在深度饱和区。基极电流相对较大,存储和释放电荷的过程长。

- 改进后的电路,除了 T 4 T_4 T4之外,BJT均采用SBD钳位,以达到明显的抗饱和效果。开关时间提升。

- 改进后的电路,电阻值减半。开关时间提升。

- 改进后的电路,输出端,使用 T 4 和 T 5 T_4和T_5 T4和T5代组合替原本的 T 4 和 D T_4和D T4和D组合。当输出低电平变为高电平时, T 4 和 T 5 T_4和T_5 T4和T5代组合电流增益很大,输出电阻小,减小了负载充电的时间。

- 改进后的电路,输入端,增加了两个SBD势垒二极管,减小杂散信号,防止信号反向过冲损坏 T 1 T_1 T1。

- 改进后的电路,中间级, R e 2 R_{e2} Re2变成了 T 6 T_6 T6电路。 T 6 T_6 T6导通滞后 T 3 T_3 T3, T 3 T_3 T3快速导通, T 6 T_6 T6分流 T 3 T_3 T3基极电流,减轻 T 3 T_3 T3饱和导通的程度。

3.3 射极耦合逻辑门电路(ECL)

- 射极耦合逻辑门电路是一种非饱和型高速数字集成电路。

- 射极耦合逻辑门电路是目前双极型电路中速度最高的。

- 传输延迟时间<2ns。

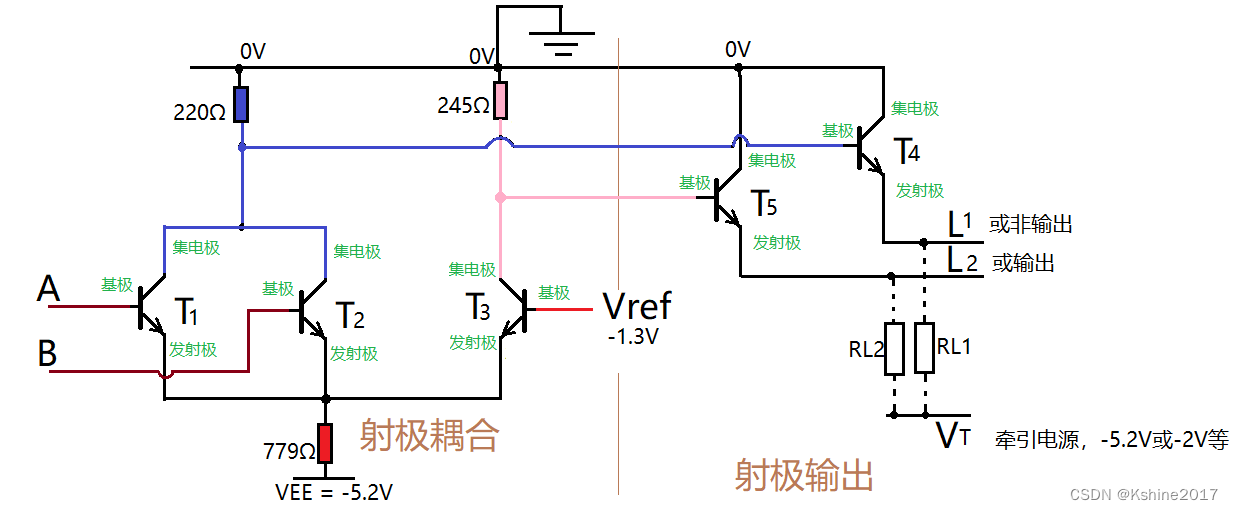

1. ECL门电路的基本结构

- 输入信号A和B,高电平 V I H = − 0.9 V V_{IH}=-0.9V VIH=−0.9V,低电平 V I L = − 1.75 V V_{IL}=-1.75V VIL=−1.75V

(1)当A=-1.75V(逻辑0),且B=-1.75V(逻辑0)。

T 3 T_3 T3基极电位更高, T 3 T_3 T3先导通。 T 3 T_3 T3集电结反偏,工作在放大区。

V E 3 = − 1.3 V − 0.7 V = − 2 V V_{E3}=-1.3V - 0.7V = -2V VE3=−1.3V−0.7V=−2V。此时 T 1 T 2 T_1T_2 T1T2的发射极压降只有-1.75-(-2)=0.25V, T 1 T 2 T_1T_2 T1T2截止。

T 4 T_4 T4的基极电压近似看成0V, V o 1 = − V B E 4 = − 0.7 V V_{o1} = -V_{BE4}=-0.7V Vo1=−VBE4=−0.7V(逻辑高电平), L 1 = 1 L_1=1 L1=1。

T 3 T_3 T3导通,忽略 T 5 T_5 T5基极电流, V C 3 = 0 − i E R C 3 = − ( V E 3 − V E E ) / R e ∗ R C 3 = − 1 V V_{C3}=0-i_ER_{C3}=-(V_E3-V_{EE})/R_e*R_{C3}=-1V VC3=0−iERC3=−(VE3−VEE)/Re∗RC3=−1V。 V o 2 = V C 3 − V B E 5 = − 1 − 0.7 = − 1.7 V V_{o2} = V_{C3}-V_{BE5}=-1-0.7=-1.7V Vo2=VC3−VBE5=−1−0.7=−1.7V(逻辑低电平), L 2 = 0 L_2=0 L2=0。

(2)当A=-0.9V(逻辑1),或B=-0.9V(逻辑1)。

T 1 或 T 2 T_1或T_2 T1或T2有一个优先导通, V E 123 = − 0.9 − 0.7 = − 1.6 V V_{E123}=-0.9-0.7=-1.6V VE123=−0.9−0.7=−1.6V。公共发射极上的电流值 I E 123 = ( V E 12 − V E E ) / R E 123 I_{E123}=(V_{E12}-V_{EE})/R_{E123} IE123=(VE12−VEE)/RE123。

V C 12 = I E 123 ∗ R C 1 ≈ − 1 V V_{C12} = I_{E123}*R_{C1}≈-1V VC12=IE123∗RC1≈−1V , T 4 ,T_4 ,T4发射结压降满足导通。 V o 1 = − 1 − 0.7 = − 1.7 V V_{o1}=-1-0.7=-1.7V Vo1=−1−0.7=−1.7V(逻辑低电平), L 1 = 0 L_1=0 L1=0。

T 3 T_3 T3发射结压降只有-1.3-(-1.6)=0.3V。 T 3 T_3 T3截止。 V C 3 ≈ 0 V V_{C3}≈0V VC3≈0V。

T 5 T_5 T5发射结压降满足导通, V o 2 = 0 − 0.7 = − 0.7 V V_{o2}=0-0.7=-0.7V Vo2=0−0.7=−0.7V(逻辑高电平), L 2 = 1 L_2=1 L2=1。

- ECL门同时具有或非/或输出,“互补逻辑输出”。

- L 1 = A + B ‾ L_1 = \overline{A+B} L1=A+B

- L 2 = A + B L_2 = A + B L2=A+B

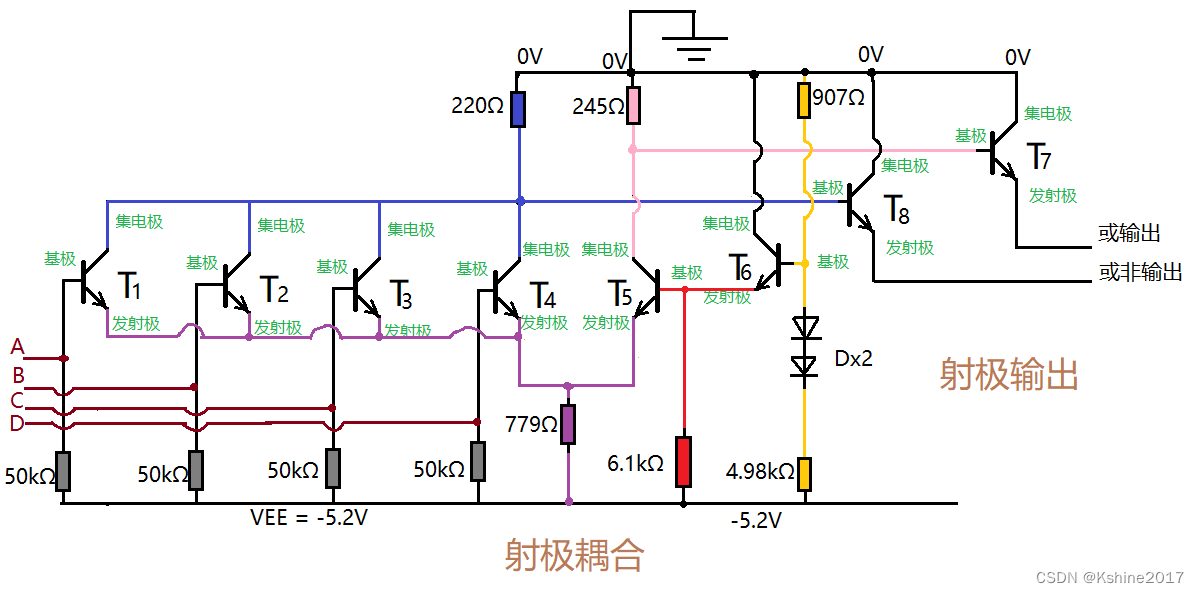

2. ECL门电路的实际电路

- T 1 T 2 T 3 T 4 T_1T_2T_3T_4 T1T2T3T4组成多端输入。与 T 5 T_5 T5射极耦合。

- T 6 T_6 T6的基极回路,有两个二极管,用于补偿温度漂移。

- T 7 T_7 T7和 T 8 T_8 T8组成电压跟随器。

3. ECL门电路的工作特点

(1)BJT只工作在“截止区”或“放大区”。基极电荷存储和释放的时间短,开关速度快。

(2)逻辑电平电压摆幅小,只有0.8V。集电极输出电压变化小,有利于电路快速转换。输出端集电极电阻(负载电阻)采用小值,充放电时间快。

(3)常用与高速系统中。

(4)缺点,制造工艺要求高,功耗大,(电压摆幅小)抗干扰能力差。输出电压为负值,需要专门的电平移动电路。

3.4 砷化镓逻辑门电路

- 金属-半导体场效应管:MESFET,由砷化镓GaAs 制成的 N沟道场效应管。

- 金属-半导体场效应管(MESFET),有肖特基势垒区。

- 砷化镓器件中,载流子迁移率非常高。砷化镓器件速度比硅器件快很多。

- 缺点,功耗大,逻辑摆幅小,噪声容限低,抗干扰能力差。

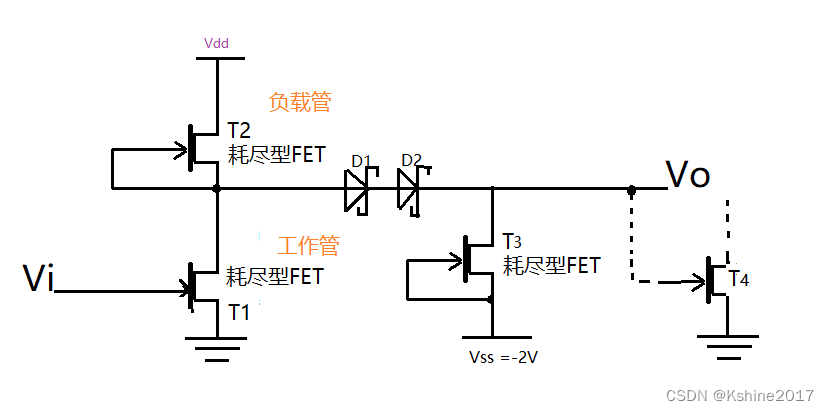

1. 直接耦合FET逻辑电路

- 参考3.1.9 NMOS门电路,下图为结构对比。

- 同时生产“增强型”和“耗尽型”两种管子,工艺要求高。

2. 耗尽型FET逻辑门电路

- 参考3.1.9 NMOS门电路

- 工作管和负载管都使用“耗尽型”MESFET。

- T 3 T_3 T3始终工作在饱和区。为D1D2提供固定的偏置电流。

3.5 逻辑描述中的几个问题

3.5.1 正负逻辑问题

- 正逻辑体制:高电平等于逻辑1,低电平等于逻辑0。

- 负逻辑体制:高电平等于逻辑0,低电平等于逻辑1。

- 正负逻辑体制的互换规则:

(1)与非 - 或非

(2)与 - 或

(3)非 - 非

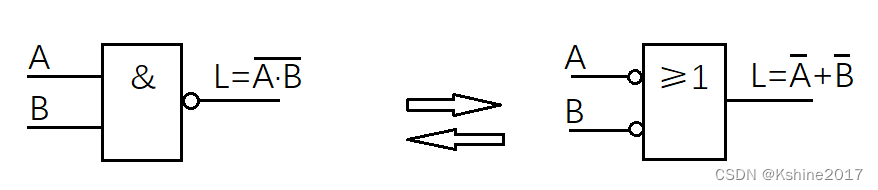

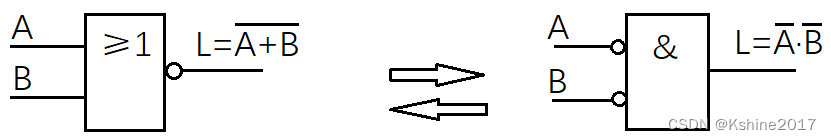

3.5.2 基本逻辑门电路的等效符号及其应用

- 默认都是正逻辑体制。

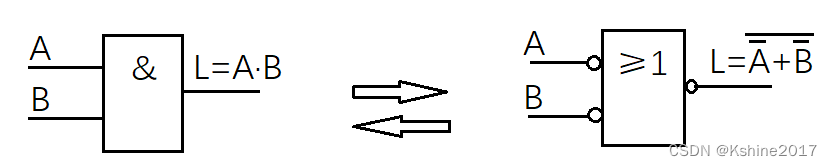

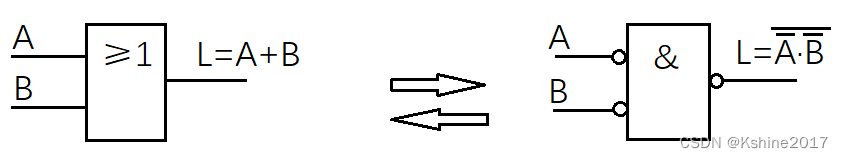

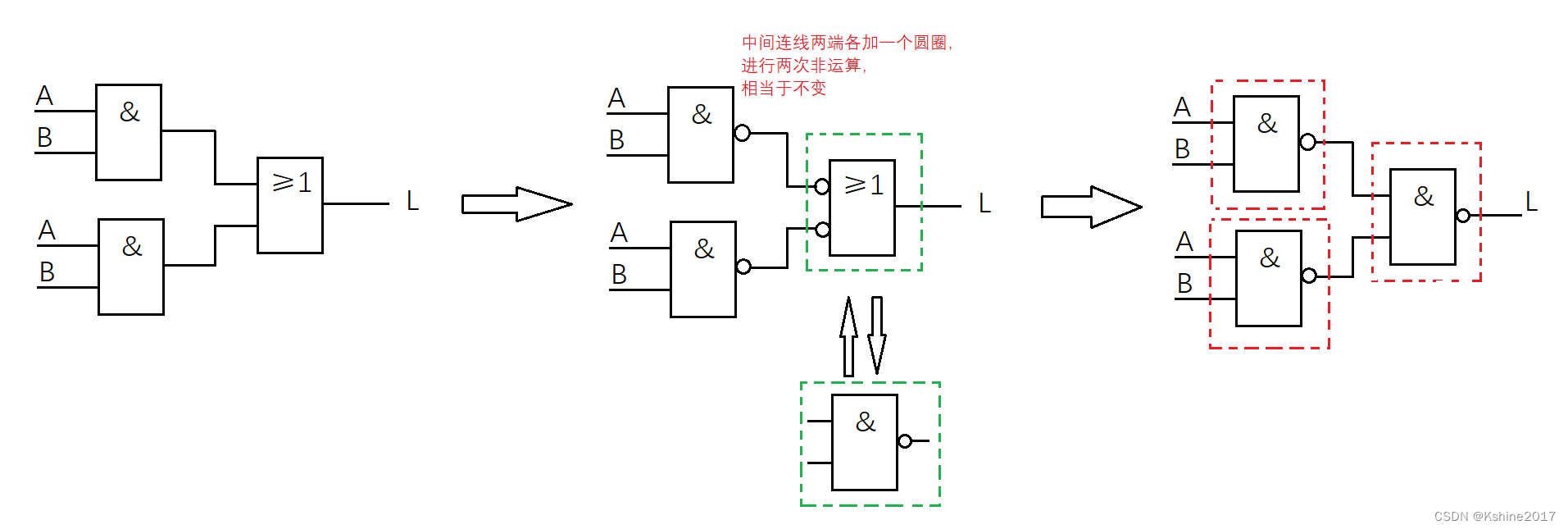

- 利用摩根定律,对基本逻辑运算进行变换。得到等效符号。

- 与非门: L = A B ‾ = A ‾ + B ‾ L=\overline{AB}=\overline{A}+\overline{B} L=AB=A+B。

- 或非门: L = A + B ‾ = A ‾ ⋅ B ‾ L=\overline{A+B} = \overline{A}·\overline{B} L=A+B=A⋅B

- 与门: L = A B = A B ‾ ‾ = A ‾ + B ‾ ‾ L=AB=\overline{\overline{AB}}=\overline{\overline{A}+\overline{B}} L=AB=AB=A+B

- 或门: L = A + B = A + B ‾ ‾ = A ‾ ⋅ B ‾ ‾ L=A+B=\overline{\overline{A+B}}=\overline{\overline{A}·\overline{B}} L=A+B=A+B=A⋅B

- 利用逻辑门的等效电路,在不改变逻辑功能的情况下,可以简化电路,减少电路中使用的门的种类或芯片的种类。

3.6 逻辑门电路使用中的几个实际问题

3.6.1 各种门电路之间的接口问题

- 多种逻辑器件混合使用。CMOS,TTL等等。电压电流参数不同。需要灌电流,拉电流,电平兼容等等。

3.6.2 门电路带负载时的接口电路

- 门电路直接驱动显示器件。LED发光二极管等等。

- 机电性负载。使用继电器等等。

3.6.3 抗干扰措施

1. 多余输入端的处理措施

- 不改变工作状态的前提下,一般不让多余输入端悬空。

- 多余输入端可以与其他输入端并接在一起。

- 上拉接电源。

- 接地。

2. 去耦滤波电容

- 数字电路由一个公共直流电源供电。

- 这个电源非理想,具有一定的内阻抗。

- 当数字电路工作时,高低电平交替变化,会产生脉冲电路或尖峰电流。

- 当变化产生的电流流过电源的内阻抗时,相互之间会产生影响,甚至是逻辑功能错乱。

- 使用10~100uf大电容连接直流电源和地。

- 使用0.1uf电容每个芯片的电源和地之间。

3. 接地与安装工艺

- 电源地和信号低分开,单点连接。

3.7 用Verilog HDL描述逻辑门电路

- 开关级建模(最低层次):使用verilog语言,建模MOS管构成的逻辑电路。

- Quartus II不支持verilog内置的开关级元件。

- 使用ModelSim、Active HDL、Verilog_XL进行verilog语言的仿真。

- 关键词:supply1,supply0。

- 定义电源线和地线。

supply1 Vdd;//定义Vdd为电源线

supply0 GND;//定义GND为地线

3.7.1 CMOS门电路的verilog建模

- 关键词:nmos、pmos。

- 控制栅极=1,nmos开关导通。信号可以从源极传输到漏极。

- 控制栅极=0,nmos开关截止。输出高阻值z。

- 控制栅极=1,pmos开关截止。输出高阻值z。

- 控制栅极=0,pmos开关导通。信号可以从源极传输到漏极。

- 由于nmos和pmos都是基本元件,下面的示例,n1和p1可以省略。

nmos n1(漏极,源极,控制栅极);/调用nmos开关元件

pmos p1(漏极,源极,控制栅极);//调用pmos开关元件nmos(漏极,源极,控制栅极);/调用nmos开关元件

pmos(漏极,源极,控制栅极);//调用pmos开关元件

-

关键词:rnmos,rpmos。

-

rnmos是nmos的另一种模型,输入到输出之间存在阻值,因而信号幅度会下降。整体用法和nmos类似。

-

rpmos是pmos的另一种模型,输入到输出之间存在阻值,因而信号幅度会下降。整体用法和pmos类似。

-

CMOS“与非门”门电路的建模如下:

//CMOS 2-input NAND 二输入与非门

module NAND2(L,A,B)input A,B;output L;supply1 Vdd;//定义Vdd为电源线supply0 GND;//定义GND为地线wire W1; //如上图所示,两个nmos之间的连接点。pmos(L,Vdd,A);//图中T1pmos(L,Vdd,B);//图中T2nmos(L,W1,B);//图中T3nmos(W1,GND,A);//图中T4

endmodule

3.7.2 CMOS传输门电路的verilog建模

- 关键词:cmos传输门

- Tn管控制信号与Tp管控制信号为互补信号。

- Tn=1,Tp=0,cmos传输门导通

- Tn=0,Tp=1,cmos传输门输出端高阻。

- cmos传输门的电源和地默认与MOS管相连,无需额外考虑连接。

- 调用名c1可以省略。

cmos c1(输出信号,输入信号,Tn管控制信号,Tp管控制信号);cmos(输出信号,输入信号,Tn管控制信号,Tp管控制信号);

- 关键词:rcmos传输门。

- 与cmos类似,输出与输入之间存在电阻,信号通过时,会有幅度衰减。

- verilog定义的cmos和rcmos都是单向的。

- 建模示例,二选一数据选择器

//2-to-1 multiplexer with cmos

module mymux2to1(X,Y,C,L)input X,Y,C;output L;wire Cnot;//C的非值inverter v1(Cnot,C);//建模实现的非门cmos(L,X,Cnot,C);cmos(L,Y,C,Cnot);

endmodulemodule inverter(Vo,Vi)input Vi;output Vo;supply1 Vdd;//定义Vdd为电源线supply0 GND;//定义GND为地线pmos(Vo,Vdd,Vi);//漏极,源极,控制栅极nmos(Vo,GND,Vi);//漏极,源极,控制栅极

endmodule

这篇关于【学习笔记】3、逻辑门电路的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!