本文主要是介绍西电计科大三下SOC微体系结构设计作业合集,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

一.VHDL设计作业

1.基于硬件描述语言的3-8译码器逻辑电路设计

2.8位双向移位寄存器设计

3.基于有限状态机的自助售票系统设计

4.按键消抖电路设计

5.同步环形FIFO设计

6.线上实验——时钟模块设计

7.线上实验——原码二位乘法器设计

8.线上实验——布斯乘法器设计

一.VHDL设计作业

源文件、测试文件及仿真结果

1.基于硬件描述语言的3-8译码器逻辑电路设计

根据3-8译码器基本原理,采用硬件描述语言设计一个3-8译码器逻辑电路,并给出仿真结果。

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity decoder3_8 isPort ( OE: in std_logic;X: in std_logic_vector(2 downto 0);Y: out std_logic_vector(7 downto 0));

end decoder3_8;architecture Behavioral of decoder3_8 is

begin

process(OE,X)

beginif OE='0' then Y<="00000000";elsif OE='1'thenCase X isWhen "000" =>Y<="11111110";When "001" =>Y<="11111101";When "010" =>Y<="11111011";When "011" =>Y<="11110111";When "100" =>Y<="11101111";When "101" =>Y<="11011111";When "110" =>Y<="10111111";When "111" =>Y<="01111111";When others =>Y<="11111111";END CASE; end if;

end process;

end Behavioral;

testbench:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity decoder3_8_tb is

-- Port ( );

end decoder3_8_tb;architecture structural of decoder3_8_tb is

component decoder3_8port(OE: in std_logic;X: in std_logic_vector(2 downto 0);Y: out std_logic_vector(7 downto 0));

end component;

signal oe:std_logic;

signal input:std_logic_vector(2 downto 0);

signal output:std_logic_vector(7 downto 0);

begin

d1:decoder3_8 port map(oe,input,output);ensure:processbeginoe<='0';wait for 50ns;oe<='1';wait;

end process;sel:processbegininput<="000";wait for 20ns;input<="001";wait for 20ns;input<="010";wait for 20ns;input<="011";wait for 20ns;input<="100";wait for 20ns;input<="101";wait for 20ns;input<="110";wait for 20ns;input<="111";wait for 20ns;

end process;

end structural;

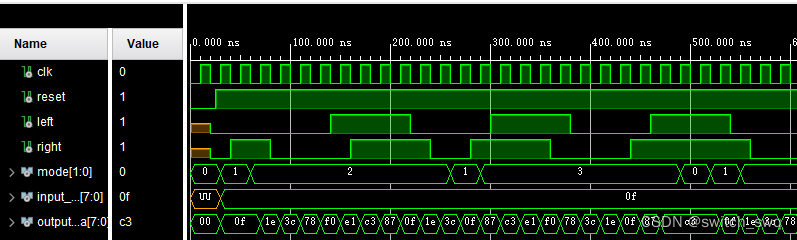

2.8位双向移位寄存器设计

采用硬件描述语言实现8位双向移位寄存器,其功能包括异步置零,同步置数,左移,右移和保持状态不变等5种功能。其中输入端口包括8位并行数据、两位的选择信号和两个1位串行数据,输出是8位并行数据。当RESET信号为低电平时,寄存器的输出被异步置零;否则当RESET=1时,与时钟有关的四种功能由输入信号MODE决定。请给出仿真结果。

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity shift_register isPort (clk,reset,left,right:in std_logic;mode:in std_logic_vector(1 downto 0);input_data:in std_logic_vector(7 downto 0);output_data:inout std_logic_vector(7 downto 0));

end shift_register;architecture Behavioral of shift_register is

begin

process(reset,clk,mode)beginif (reset='0')thenoutput_data<="00000000";elsif(reset='1'and clk='1')thencase mode iswhen "00"=>output_data<=output_data;when "01"=>output_data<=input_data;when "10"=>output_data(0)<=left;output_data(7)<=output_data(6);output_data(6)<=output_data(5);output_data(5)<=output_data(4);output_data(4)<=output_data(3);output_data(3)<=output_data(2);output_data(2)<=output_data(1);output_data(1)<=output_data(0); when "11"=>output_data(0)<=output_data(1);output_data(1)<=output_data(2);output_data(2)<=output_data(3);output_data(3)<=output_data(4);output_data(4)<=output_data(5);output_data(5)<=output_data(6);output_data(6)<=output_data(7);output_data(7)<=right;when others=>output_data<=output_data;end case; end if;

end process;end Behavioral;

testbench:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity shift_register_tb is

-- Port ( );

end shift_register_tb;architecture Behavioral of shift_register_tb is

component shift_register

port(clk,reset,left,right:in std_logic;mode:in std_logic_vector(1 downto 0);input_data:in std_logic_vector(7 downto 0);output_data:inout std_logic_vector(7 downto 0)

);

end component;

signal clk,reset,left,right:std_logic;

signal mode:std_logic_vector(1 downto 0);

signal input_data:std_logic_vector(7 downto 0);

signal output_data:std_logic_vector(7 downto 0);

begin

sr1:shift_register port map(clk,reset,left,right,mode,input_data,output_data);clock_gen:processbeginleft<=output_data(7);right<=output_data(0);clk<='0';wait for 10ns;clk<='1';wait for 10ns;

end process;reset_gen:processbeginreset<='0';wait for 25ns;reset<='1';wait;

end process;mode_test:processbeginmode<="00";wait for 30ns;mode<="01";input_data<="00001111";wait for 30ns;mode<="10";wait for 200ns;mode<="01";input_data<="00001111";wait for 30ns;mode<="11";wait for 200ns;

end process;end Behavioral;

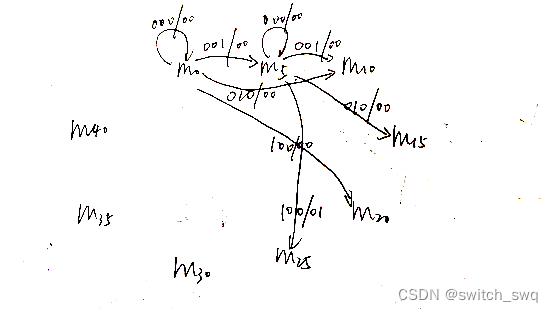

3.基于有限状态机的自助售票系统设计

某自助售票系统只能接收 5元和10元纸币,若一张票的价格设定为 25元。

请利用有限状态机设计该售票系统,

1. 首先给出状态说明,然后画出具体的状态图及说明状态转移关系。

2. 并完成硬件描述语言程序设计。

3.将第1和2题的答案做成word文档上传。

4.扩展要求(加分10分):增加20元纸币输入。

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity ticket_state_machine isPort (clk,reset:in std_logic;input_money:in std_logic_vector(2 downto 0);return_money:out std_logic_vector(2 downto 0);output_ticket:out std_logic);

end ticket_state_machine;architecture Behavioral of ticket_state_machine is

type states is (m0,m5,m10,m15,m20,m25,m30,m35,m40);

signal current_state,next_state:states;

beginstart:process(reset,clk)beginif(reset='1')thencurrent_state<=m0;elsif(reset='0'and clk='1'and clk'event)thencurrent_state<=next_state;end if;

end process;state_machine:process(current_state,input_money)begincase current_state iswhen m0=>output_ticket<='0';return_money<="000";case input_money iswhen"000"=>next_state<=m0;when"001"=>next_state<=m5;when"010"=>next_state<=m10;when"100"=>next_state<=m20;when others=>next_state<=current_state;end case;when m5=>output_ticket<='0';return_money<="000";case input_money iswhen"000"=>next_state<=m5;when"001"=>next_state<=m10;when"010"=>next_state<=m15;when"100"=>next_state<=m25;when others=>next_state<=current_state;end case;when m10=>output_ticket<='0';return_money<="000";case input_money iswhen"000"=>next_state<=m10;when"001"=>next_state<=m15;when"010"=>next_state<=m20;when"100"=>next_state<=m30;when others=>next_state<=current_state;end case; when m15=>output_ticket<='0';return_money<="000";case input_money iswhen"000"=>next_state<=m15;when"001"=>next_state<=m20;when"010"=>next_state<=m25;when"100"=>next_state<=m35;when others=>next_state<=current_state;end case; when m20=>output_ticket<='0';return_money<="000";case input_money iswhen"000"=>next_state<=m20;when"001"=>next_state<=m25;when"010"=>next_state<=m30;when"100"=>next_state<=m40;when others=>next_state<=current_state;end case; when m25=>output_ticket<='1';return_money<="000";case input_money iswhen"000"=>next_state<=m0;when"001"=>next_state<=m5;when"010"=>next_state<=m10;when"100"=>next_state<=m20;when others=>next_state<=current_state;end case; when m30=>output_ticket<='1';return_money<="001";case input_money iswhen"000"=>next_state<=m0;when"001"=>next_state<=m5;when"010"=>next_state<=m10;when"100"=>next_state<=m20;when others=>next_state<=current_state;end case;when m35=>output_ticket<='1';return_money<="010";case input_money iswhen"000"=>next_state<=m0;when"001"=>next_state<=m5;when"010"=>next_state<=m10;when"100"=>next_state<=m20;when others=>next_state<=current_state;end case; when m40=>output_ticket<='1';return_money<="011";case input_money iswhen"000"=>next_state<=m0;when"001"=>next_state<=m5;when"010"=>next_state<=m10;when"100"=>next_state<=m20;when others=>next_state<=current_state;end case; end case;

end process;end Behavioral;

testbench:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity ticket_state_machine_tb is

-- Port ( );

end ticket_state_machine_tb;architecture Behavioral of ticket_state_machine_tb is

component ticket_state_machinePort (clk,reset:in std_logic;input_money:in std_logic_vector(2 downto 0);return_money:out std_logic_vector(2 downto 0);output_ticket:out std_logic);

end component;

signal clk,reset: std_logic;

signal input_money: std_logic_vector(2 downto 0);

signal return_money: std_logic_vector(2 downto 0);

signal output_ticket: std_logic;

begin

tsm:ticket_state_machine port map(clk,reset,input_money,return_money,output_ticket);clock:processbeginclk<='0';wait for 10ns;clk<='1';wait for 10ns;

end process;start:processbeginreset<='1';wait for 20ns;reset<='0';wait;

end process;test:processbeginwait for 50ns;input_money<="001";wait for 20ns;input_money<="000";wait for 50ns;input_money<="010";wait for 20ns;input_money<="000";wait for 50ns;input_money<="100";wait for 20ns;input_money<="000";wait for 50ns;input_money<="010";wait for 20ns;input_money<="000";

end process;end Behavioral;

4.按键消抖电路设计

请使用硬件描述语言设计一个按键消抖电路,假设输入时钟频率为50MHZ。请给出设计方案及仿真验证结果。

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity key_stroke isgeneric(CLK_FRE:integer:=50000000);Port (clk:in std_logic;reset:in std_logic;key_in:in std_logic;output:out std_logic );

end key_stroke;architecture Behavioral of key_stroke istype states is(s0,s1,s2,s3,s4);

signal state:states;begin

process(reset,clk,key_in)

variable count_num:integer:=3*CLK_FRE/1000;

variable count:integer:=0;beginif reset='1'thenstate<=s0;count:=0;output<='0';elsif reset='0'thencase state iswhen s0=>if key_in='1' then state<=s1;end if;when s1=>if clk='1' then count:=count+1;end if;if count=count_num then state<=s2; end if;when s2=>if(key_in='1')then output<='1';state<=s3;elsif(key_in='0')then output<='0';state<=s4;end if;when s3=>output<='0';if(key_in='0')then state<=s4;end if;when s4=>state<=s0;count:=0;output<='0'; end case; end if;

end process;end Behavioral;

testbench:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity key_stroke_tb is

-- Port ( );

end key_stroke_tb;architecture Behavioral of key_stroke_tb is

component key_strokegeneric(CLK_FRE:integer:=50000000);port(clk:in std_logic;reset:in std_logic;key_in:in std_logic;output:out std_logic );

end component;

signal clk:std_logic;

signal reset:std_logic;

signal key_in:std_logic;

signal output:std_logic;

begin

ks:key_stroke generic map(50000000)port map(clk,reset,key_in,output);clock:process

beginclk<='0';wait for 10ns;clk<='1';wait for 10ns;

end process;rst:process

beginreset<='1';wait for 25ns;reset<='0';wait;

end process;test:process

beginkey_in<='1';wait for 50ns;key_in<='0';wait for 70ns;key_in<='1';wait for 100ns;key_in<='0';wait for 40ns;key_in<='1';wait for 120ns;key_in<='0';wait for 30ns;key_in<='1';wait for 40ns;key_in<='0';wait for 70ns;key_in<='1';wait for 30ns;key_in<='0';wait for 100ns;key_in<='1';wait for 50ns;key_in<='0';wait for 20ns;key_in<='1';wait for 1000ns;key_in<='0';wait for 2000ns;

end process;end Behavioral;

5.同步环形FIFO设计

请采用硬件描述语言设计实现一个存储深度M和数据宽度N可以用户配置的同步FIFO存储器,请给出仿真结果。

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;entity FIFO_ring is

generic(depth:positive :=8;width:positive:=8

);Port(clk:in std_logic;rst:in std_logic;data_in:in std_logic_vector(7 downto 0);wr:in std_logic;rd:in std_logic;

-- wr_clr:in std_logic;

-- wr_en:in std_logic;

-- rd_clr:in std_logic;

-- rd_en:in std_logic;empty:out std_logic;full:out std_logic;data_out:out std_logic_vector(7 downto 0));

end FIFO_ring;architecture Behavioral of FIFO_ring is

component duaram

generic(depth:positive :=8;width:positive:=8

);

Port(clka:in std_logic;wr:in std_logic;addra:in std_logic_vector(depth-1 downto 0);datain:in std_logic_vector(width-1 downto 0);clkb:in std_logic;rd:in std_logic;addrb:in std_logic_vector(depth-1 downto 0);dataout:out std_logic_vector(width-1 downto 0)

);

end component;

component write_pointergeneric(depth:positive);Port(clk:in std_logic;rst:in std_logic;wq:in std_logic;wr_pt:out std_logic_vector(depth-1 downto 0));

end component;

component read_pointergeneric(depth:positive);Port(clk:in std_logic;rst:in std_logic;rq:in std_logic;rd_pt:out std_logic_vector(depth-1 downto 0));

end component;

component judge_statusgeneric(depth:positive);port(clk:in std_logic;rst:in std_logic;wr_pt:in std_logic_vector(depth-1 downto 0);rd_pt:in std_logic_vector(depth-1 downto 0);empty:out std_logic;full:out std_logic);

end component;signal rp_line:std_logic_vector(depth-1 downto 0);

signal wp_line:std_logic_vector(depth-1 downto 0);begin

duaram_inst:duaram generic map(depth,width)port map(clka=>clk,clkb=>clk,datain=>data_in,dataout=>data_out,addra=>wp_line,addrb=>rp_line,rd=>rd,wr=>wr);

write_pointer_inst:write_pointer generic map(depth)port map(clk=>clk,rst=>rst,wq=>wr,wr_pt=>wp_line);

read_pointer_inst:read_pointer generic map(depth)port map(clk=>clk,rst=>rst,rq=>rd,rd_pt=>rp_line);

judge_status_inst:judge_status generic map(depth)port map(clk=>clk,rst=>rst,wr_pt=>wp_line,rd_pt=>rp_line,full=>full,empty=>empty);end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;entity duaram is

generic(depth:positive :=8;width:positive:=8

);

Port(clka:in std_logic;wr:in std_logic;addra:in std_logic_vector(depth-1 downto 0);datain:in std_logic_vector(width-1 downto 0);clkb:in std_logic;rd:in std_logic;addrb:in std_logic_vector(depth-1 downto 0);dataout:out std_logic_vector(width-1 downto 0)

);

end duaram;architecture Behavioral of duaram istype ram is array(2**depth-1 downto 0)of std_logic_vector(width-1 downto 0);

signal dualram:ram;beginprocess(clka,clkb)

beginif(clka'event and clka='1')thenif(wr='0')then dualram(conv_integer(addra))<=datain;end if;end if;

end process;process(clkb)

beginif(clkb'event and clkb='1')thenif(rd='0')then dataout<=dualram(conv_integer(addrb));end if;end if;

end process;end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;entity write_pointer isgeneric(depth:positive);Port(clk:in std_logic;rst:in std_logic;wq:in std_logic;wr_pt:out std_logic_vector(depth-1 downto 0));

end write_pointer;architecture Behavioral of write_pointer issignal wr_pt_t:std_logic_vector(depth-1 downto 0);begin

process(rst,clk)

beginif(rst='0')thenwr_pt_t<=(others=>'0');elsif(clk'event and clk='1')thenif wq='0'then wr_pt_t<=wr_pt_t+1;end if;end if;

end process;

wr_pt<=wr_pt_t;

end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;entity read_pointer isgeneric(depth:positive);Port(clk:in std_logic;rst:in std_logic;rq:in std_logic;rd_pt:out std_logic_vector(depth-1 downto 0));

end read_pointer;architecture Behavioral of read_pointer issignal rd_pt_t:std_logic_vector(depth-1 downto 0);begin

process(rst,clk)

beginif(rst='0')thenrd_pt_t<=(others=>'0');elsif(clk'event and clk='1')thenif rq='0'then rd_pt_t<=rd_pt_t+1;end if;end if;

end process;

rd_pt<=rd_pt_t;

end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;entity judge_status isgeneric(depth:positive);port(clk:in std_logic;rst:in std_logic;wr_pt:in std_logic_vector(depth-1 downto 0);rd_pt:in std_logic_vector(depth-1 downto 0);empty:out std_logic;full:out std_logic);

end entity judge_status;architecture Behavioral of judge_status isbeginprocess(rst,clk)

beginif(rst='0')then empty<='1';elsif clk'event and clk='1'thenif wr_pt=rd_pt then empty<='1';else empty<='0';end if;end if;

end process;process(rst,clk)

beginif(rst='0')then full<='0';elsif clk'event and clk='1'thenif wr_pt>rd_pt thenif(depth+rd_pt)=wr_pt then full<='1';else full<='0';end if;end if;end if;

end process;end Behavioral;testbench:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity FIFO_ring_tb is

-- Port ( );

end FIFO_ring_tb;architecture Behavioral of FIFO_ring_tb iscomponent FIFO_ring

generic(depth:positive :=8;width:positive:=8

);Port(clk:in std_logic;rst:in std_logic;data_in:in std_logic_vector(7 downto 0);wr:in std_logic;rd:in std_logic;

-- wr_clr:in std_logic;

-- wr_en:in std_logic;

-- rd_clr:in std_logic;

-- rd_en:in std_logic;empty:out std_logic;full:out std_logic;data_out:out std_logic_vector(7 downto 0));

end component;signal clk:std_logic;

signal rst:std_logic;

signal data_in:std_logic_vector(7 downto 0);

signal wr:std_logic;

signal rd:std_logic;

signal empty:std_logic;

signal full:std_logic;

signal data_out:std_logic_vector(7 downto 0);beginFIFO_ring_inst:FIFO_ring generic map(8,8)port map(clk,rst,data_in,wr,rd,empty,full,data_out);clock:process

beginclk<='0';wait for 10ns;clk<='1';wait for 10ns;

end process;reset:process

beginrst<='0';wait for 25ns;rst<='1';wait;

end process;test:process

beginrd<='1';wr<='1';data_in<="00000000";wait for 50ns;data_in<="00000001";wr<='0';wait for 20ns;wr<='1';wait for 30ns;data_in<="00000010";wr<='0';wait for 20ns;wr<='1';wait for 30ns;data_in<="00000100";wr<='0';wait for 20ns;wr<='1';wait for 30ns;data_in<="00001000";wr<='0';wait for 20ns;wr<='1';wait for 30ns;data_in<="00010000";wr<='0';wait for 20ns;wr<='1';wait for 30ns;data_in<="00100000";wr<='0';wait for 20ns;wr<='1';wait for 30ns;data_in<="01000000";wr<='0';wait for 20ns;wr<='1';wait for 30ns;data_in<="10000000";wr<='0';wait for 20ns;wr<='1';wait for 50ns;rd<='0';wait for 20ns;rd<='1';wait for 30ns;rd<='0';wait for 20ns;rd<='1';wait for 30ns;rd<='0';wait for 20ns;rd<='1';wait for 30ns;rd<='0';wait for 20ns;rd<='1';wait for 30ns;rd<='0';wait for 20ns;rd<='1';wait for 30ns;rd<='0';wait for 20ns;rd<='1';wait for 30ns;rd<='0';wait for 20ns;rd<='1';wait for 30ns;rd<='0';wait for 20ns;rd<='1';wait for 30ns;wait;end process;end Behavioral;

6.线上实验——时钟模块设计

采用硬件描述语言设计实现CPU时钟模块,输出信号包括四个节拍信号(每两个时钟周期一个节拍),时钟反相信号,时钟2分频信号及其反相信号,完成逻辑功能设计及仿真验证,并给出仿真结果。

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity clock isPort(clk,rst:in std_logic;clk1,nclk1:out std_logic; --clkclk2,nclk2:out std_logic; --clk二分频w0,w1,w2,w3:out std_logic --节拍信号);

end clock;architecture Behavioral of clock is

beginprocess(clk)

variable count_clk2:integer:=0;

variable count_w:integer:=0;

beginif(rst='0')thenw0<='0';w1<='0';w2<='0';w3<='0';clk1<='0';nclk1<='1';clk2<='0';nclk2<='1';count_clk2:=0;count_w:=0;elsif(rst='1')thenclk1<=clk;nclk1<=not clk;if(clk'event and clk='1')thenif(count_clk2=0)then count_clk2:=1;clk2<='1';nclk2<='0';elsif(count_clk2=1)then count_clk2:=0;clk2<='0';nclk2<='1';end if;if(count_w>=0 and count_w<=3)then w0<='1';else w0<='0';end if;if(count_w>=4 and count_w<=7)then w1<='1';else w1<='0';end if;if(count_w>=8 and count_w<=11)then w2<='1';else w2<='0';end if;if(count_w>=12 and count_w<=15)then w3<='1';else w3<='0';end if;if(count_w<15)then count_w:=count_w+1;else count_w:=0;end if;end if;end if;

end process;end Behavioral;

testbench:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity clock_tb is

-- Port ( );

end clock_tb;architecture Behavioral of clock_tb is

component clockPort(clk,rst:in std_logic;clk1,nclk1:out std_logic; --clkclk2,nclk2:out std_logic; --clk二分频w0,w1,w2,w3:out std_logic --节拍信号);

end component;signal clk,rst:std_logic;

signal clk1,nclk1:std_logic; --clk

signal clk2,nclk2:std_logic; --clk二分频

signal w0,w1,w2,w3:std_logic; --节拍信号begin

clock_inst:clock port map(clk,rst,clk1,nclk1,clk2,nclk2,w0,w1,w2,w3);clock_gen:process

beginclk<='0';wait for 10ns;clk<='1';wait for 10ns;

end process;reset_gen:process

beginrst<='0';wait for 25ns;rst<='1';wait;

end process;end Behavioral;

7.线上实验——原码二位乘法器设计

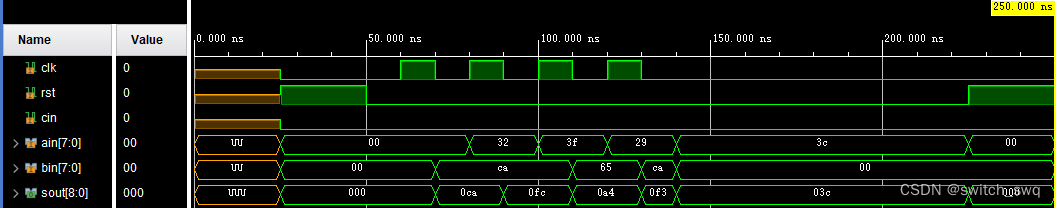

请用硬件描述语言设计一个原码二位乘法器,其中两个操作数位宽为8,请给出仿真结果。

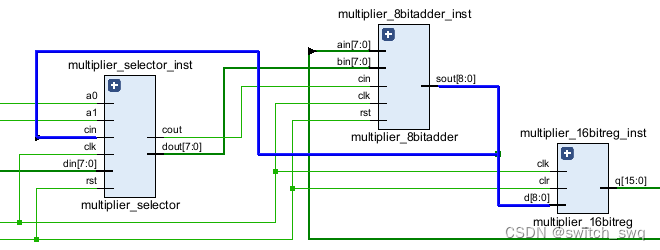

顶层——multiplier_2bit:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity multiplier_2bit isPort(clk,start:in std_logic;ain,bin:in std_logic_vector(7 downto 0);done:out std_logic;sout:inout std_logic_vector(15 downto 0));

end multiplier_2bit;architecture Behavioral of multiplier_2bit iscomponent multiplier_ctrlPort (clk,start:in std_logic;clkout,rstall,done:out std_logic);

end component;

component multiplier_8bitshiftregPort (clk,load:in std_logic;din:in std_logic_vector(7 downto 0);qb0,qb1:out std_logic);

end component;

component multiplier_16bitregPort (clk,clr:in std_logic;d:in std_logic_vector(8 downto 0);q:out std_logic_vector(15 downto 0));

end component;

component multiplier_selectorPort (clk,rst:in std_logic;a0,a1,cin:in std_logic;din:in std_logic_vector(7 downto 0);cout:out std_logic;dout:out std_logic_vector(7 downto 0));

end component;

component multiplier_8bitadderPort (clk,rst:in std_logic;cin:in std_logic;ain,bin:in std_logic_vector(7 downto 0);sout:out std_logic_vector(8 downto 0));

end component;signal clk_line:std_logic;

signal rst_line:std_logic;

signal cin_line:std_logic;

signal qb1_line,qb0_line:std_logic;

signal bin_line:std_logic_vector(7 downto 0);

signal sout_line:std_logic_vector(8 downto 0);

signal test_line:std_logic_vector(8 downto 0);begin

multiplier_ctrl_inst:multiplier_ctrl port map(clk=>clk,start=>start,clkout=>clk_line,rstall=>rst_line,done=>done);

multiplier_8bitshiftreg_inst:multiplier_8bitshiftreg port map(clk=>clk_line,load=>rst_line,din=>ain,qb0=>qb0_line,qb1=>qb1_line);

multiplier_16bitreg_inst:multiplier_16bitreg port map(clk=>clk_line,clr=>rst_line,d=>sout_line,q=>sout);

multiplier_selector_inst:multiplier_selector port map(clk=>clk_line,rst=>rst_line,a0=>qb0_line,a1=>qb1_line,cin=>sout_line(8),din=>bin,cout=>cin_line,dout=>bin_line);

multiplier_8bitadder_inst:multiplier_8bitadder port map(clk=>clk_line,rst=>rst_line,cin=>cin_line,ain=>sout(15 downto 8),bin=>bin_line,sout=>sout_line);end Behavioral;

testbench:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity multiplier_2bit_tb is

-- Port ( );

end multiplier_2bit_tb;architecture Behavioral of multiplier_2bit_tb is

component multiplier_2bitPort(clk,start:in std_logic;ain,bin:in std_logic_vector(7 downto 0);done:out std_logic;sout:inout std_logic_vector(15 downto 0));

end component;

signal clk,start: std_logic;

signal ain,bin: std_logic_vector(7 downto 0);

signal done: std_logic;

signal sout: std_logic_vector(15 downto 0);

begin

multiplier_2bit_inst:multiplier_2bit port map(clk,start,ain,bin,done,sout);clock_gen:process

begin clk<='1';wait for 10ns;clk<='0';wait for 10ns;

end process;test:process

beginain<="10011010";bin<="01100101";wait for 25ns;start<='1';wait for 25ns;start<='0'; wait for 150ns;

end process;end Behavioral;

模块:

multiplier_2bit_ctrl :

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity multiplier_ctrl isPort (clk,start:in std_logic;clkout,rstall,done:out std_logic);

end multiplier_ctrl;architecture Behavioral of multiplier_ctrl issignal cnt3b:std_logic_vector(2 downto 0);beginprocess(clk,start)

beginrstall<=start;if(start='1')then cnt3b<="000";elsif clk'event and clk='1'then if cnt3b<=4 then cnt3b<=cnt3b+1;end if;end if;

end process;process(clk,cnt3b,start)

beginif (start='1')thenclkout<='0';done<='0'; elsif(start='0')then if cnt3b<=4 then clkout<=clk;else clkout<='0';done<='1';end if; end if;

end process;end Behavioral;

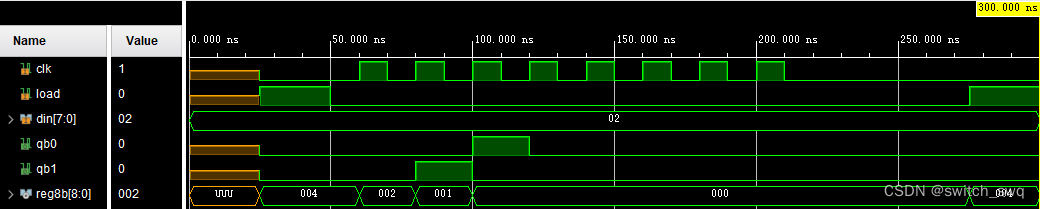

multiplier_2bit_8bitshiftreg:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity multiplier_8bitshiftreg isPort (clk,load:in std_logic;din:in std_logic_vector(7 downto 0);qb0,qb1:out std_logic);

end multiplier_8bitshiftreg;architecture Behavioral of multiplier_8bitshiftreg issignal reg8b:std_logic_vector(7 downto 0);beginprocess(clk,load)

beginif load='1'then reg8b<=din;qb0<='0';qb1<='0';end if;if(load='0'and clk='1')then qb0<=reg8b(0);qb1<=reg8b(1);reg8b(5 downto 0)<=reg8b(7 downto 2);reg8b(7 downto 6)<="00"; end if;

end process;end Behavioral;

multiplier_2bit_16bitreg:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity multiplier_16bitreg isPort (clk,clr:in std_logic;d:in std_logic_vector(8 downto 0);q:out std_logic_vector(15 downto 0));

end multiplier_16bitreg;architecture Behavioral of multiplier_16bitreg isbeginprocess(clk,clr)

variable sr16b:std_logic_vector(15 downto 0);

beginif clr='1'thensr16b:="0000000000000000";elsif(clr='0'and clk'event and clk='1')then sr16b(15 downto 8):=d(7 downto 0);sr16b(13 downto 0):=sr16b(15 downto 2);sr16b(15):=d(8);sr16b(14):=d(8);end if; q<=sr16b;

end process;end Behavioral;

multiplier_2bit_selector:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity multiplier_selector isPort (clk,rst:in std_logic;a0,a1,cin:in std_logic;din:in std_logic_vector(7 downto 0);cout:out std_logic;dout:out std_logic_vector(7 downto 0));

end multiplier_selector;architecture Behavioral of multiplier_selector isbeginprocess(clk,a0,a1,cin,din)

beginif(rst='1')then cout<='0';dout<="00000000";elsif(rst='0'and clk'event and clk='0')thenif(a0=a1 and a0=cin)then dout<="00000000";cout<=cin;elsif(a1='0'and (a0 xor cin)='1')then dout<=din;cout<='0';elsif((a1 xor a0)='1'and a0=cin)thendout(7 downto 1)<=din(6 downto 0); dout(0)<='0';cout<='0';elsif(a1='1'and(a0 xor cin)='1')thendout<=(not din)+1;cout<='1'; end if;end if;

end process;end Behavioral;

multiplier_2bit_8bitadder:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity multiplier_8bitadder isPort (clk,rst:in std_logic;cin:in std_logic;ain,bin:in std_logic_vector(7 downto 0);sout:out std_logic_vector(8 downto 0));

end multiplier_8bitadder;architecture Behavioral of multiplier_8bitadder is

beginprocess(clk,rst,ain,bin,cin)

beginif(rst='1')then sout<="000000000";elsif(rst='0'and clk='0')thensout<=('0'& ain)+(cin & bin);end if;

end process;end Behavioral;

设计注意点:

0.设计顺序:控制器-8b移位寄存器-16位缓存器-选择器-加法器

1.输入位8位无符号数,若输入有符号数需修改位宽并另外计算符号位。

2.共用总线需注意时序,防止总线冲突以及数据读取错误

共用总线sout时序设计:

3.process内语句顺序执行的次序。

4.变量的使用:mulitiplier_16bitreg中

variable sr16b:std_logic_vector(15 downto 0);若使用 signal sr16b,则 q<=sr16b; 无效

5.位拓展:

sout<=('0'& ain)+(cin & bin); 使用 & 符拓展位宽

8.线上实验——布斯乘法器设计

采用硬件描述语言设计实现布斯乘法器,完成逻辑功能设计及仿真验证,并给出仿真结果。

按照7中的设计顺序对7中设计文件进行修改:

ctrl模块发出时钟周期数改为8;8bitshiftreg和16bitreg模块每个时钟周期移动1位,且8;8bitshiftreg输出的是a0和a-1;16bitreg和selector模块载入数值后求补;selector模块删去cin和cout信号并修改规则;adder无cin...

顶层模块——multiplier_booth:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity multiplier_booth isPort(clk,start:in std_logic;ain,bin:in std_logic_vector(7 downto 0);done:out std_logic;sout:inout std_logic_vector(15 downto 0));

end multiplier_booth;architecture Behavioral of multiplier_booth iscomponent multiplier_booth_ctrlPort (clk,start:in std_logic;clkout,rstall,done:out std_logic);

end component;

component multiplier_booth_8bitshiftregPort (clk,load:in std_logic;din:in std_logic_vector(7 downto 0);qb0,qb1:out std_logic);

end component;

component multiplier_booth_16bitregPort (clk,clr:in std_logic;d:in std_logic_vector(8 downto 0);q:out std_logic_vector(15 downto 0));

end component;

component multiplier_booth_selectorPort (clk,rst:in std_logic;a0,a1:in std_logic;din:in std_logic_vector(7 downto 0);dout:out std_logic_vector(7 downto 0));

end component;

component multiplier_booth_8bitadderPort (clk,rst:in std_logic;ain,bin:in std_logic_vector(7 downto 0);sout:out std_logic_vector(8 downto 0));

end component;signal clk_line:std_logic;

signal rst_line:std_logic;

signal qb1_line,qb0_line:std_logic;

signal bin_line:std_logic_vector(7 downto 0);

signal sout_line:std_logic_vector(8 downto 0);

signal test_line:std_logic_vector(8 downto 0);begin

multiplier_booth_ctrl_inst:multiplier_booth_ctrl port map(clk=>clk,start=>start,clkout=>clk_line,rstall=>rst_line,done=>done);

multiplier_booth_8bitshiftreg_inst:multiplier_booth_8bitshiftreg port map(clk=>clk_line,load=>rst_line,din=>ain,qb0=>qb0_line,qb1=>qb1_line);

multiplier_booth_16bitreg_inst:multiplier_booth_16bitreg port map(clk=>clk_line,clr=>rst_line,d=>sout_line,q=>sout);

multiplier_booth_selector_inst:multiplier_booth_selector port map(clk=>clk_line,rst=>rst_line,a0=>qb0_line,a1=>qb1_line,din=>bin,dout=>bin_line);

multiplier_booth_8bitadder_inst:multiplier_booth_8bitadder port map(clk=>clk_line,rst=>rst_line,ain=>sout(15 downto 8),bin=>bin_line,sout=>sout_line);end Behavioral;

testbench:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity multiplier_booth_tb is

-- Port ( );

end multiplier_booth_tb;architecture Behavioral of multiplier_booth_tb is

component multiplier_boothPort(clk,start:in std_logic;ain,bin:in std_logic_vector(7 downto 0);done:out std_logic;sout:inout std_logic_vector(15 downto 0));

end component;

signal clk,start: std_logic;

signal ain,bin: std_logic_vector(7 downto 0);

signal done: std_logic;

signal sout: std_logic_vector(15 downto 0);

begin

multiplier_booth_inst:multiplier_booth port map(clk,start,ain,bin,done,sout);clock_gen:process

begin clk<='1';wait for 10ns;clk<='0';wait for 10ns;

end process;test:process

beginain<="00000010";bin<="10000010";wait for 25ns;start<='1';wait for 25ns;start<='0'; wait for 200ns;

end process;end Behavioral;

模块:

multiplier_booth_ctrl:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity multiplier_booth_ctrl isPort (clk,start:in std_logic;clkout,rstall,done:out std_logic);

end multiplier_booth_ctrl;architecture Behavioral of multiplier_booth_ctrl issignal cnt4b:std_logic_vector(3 downto 0);beginprocess(clk,start)

beginrstall<=start;if(start='1')then cnt4b<="0000";elsif clk'event and clk='1'then if cnt4b<=8 then cnt4b<=cnt4b+1;end if;end if;

end process;process(clk,cnt4b,start)

beginif (start='1')thenclkout<='0';done<='0'; elsif(start='0')then if cnt4b<=8 then clkout<=clk;else clkout<='0';done<='1';end if; end if;

end process;end Behavioral;

multiplier_booth_8bitshiftreg:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity multiplier_booth_8bitshiftreg isPort (clk,load:in std_logic;din:in std_logic_vector(7 downto 0);qb0,qb1:out std_logic);

end multiplier_booth_8bitshiftreg;architecture Behavioral of multiplier_booth_8bitshiftreg issignal reg8b:std_logic_vector(8 downto 0);beginprocess(clk,load)

beginif load='1'then if(din(7)='1')then reg8b(8 downto 1)<=(din(7)&(not din(6 downto 0)))+1;else reg8b(8 downto 1)<=din;end if; --取补码reg8b(0)<='0';qb0<='0';qb1<='0';end if;if(load='0'and clk='1')then qb0<=reg8b(0);qb1<=reg8b(1);reg8b(7 downto 0)<=reg8b(8 downto 1);reg8b(8)<='0'; end if;

end process;end Behavioral;

multiplier_booth_16bitreg:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity multiplier_booth_16bitreg isPort (clk,clr:in std_logic;d:in std_logic_vector(8 downto 0);q:out std_logic_vector(15 downto 0));

end multiplier_booth_16bitreg;architecture Behavioral of multiplier_booth_16bitreg isbeginprocess(clk,clr)

variable sr16b:std_logic_vector(15 downto 0);

beginif clr='1'thensr16b:="0000000000000000";elsif(clr='0'and clk'event and clk='1')then sr16b(15 downto 8):=d(7 downto 0);sr16b(14 downto 0):=sr16b(15 downto 1);sr16b(15):=d(8); --移位复制符号位end if; q<=sr16b;

end process;end Behavioral;

multiplier_booth_selector:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity multiplier_booth_selector isPort (clk,rst:in std_logic;a0,a1:in std_logic;din:in std_logic_vector(7 downto 0);dout:out std_logic_vector(7 downto 0));

end multiplier_booth_selector;architecture Behavioral of multiplier_booth_selector isbeginprocess(clk,a0,a1,din)

variable complement_x:std_logic_vector(7 downto 0);

variable complement_x_negative:std_logic_vector(7 downto 0);

beginif(rst='1')then dout<="00000000";elsif(rst='0'and clk'event and clk='0')thenif(din(7)='1')then complement_x:=(din(7)&(not din(6 downto 0)))+1;else complement_x:=din;end if; --取X补码if((not din(7))='1')then complement_x_negative:=((not din(7))&(not din(6 downto 0)))+1;else complement_x_negative:=(not din(7))&din(6 downto 0);end if; --取-X补码if(a1=a0)then dout<="00000000";elsif(a0='1'and a1='0')then dout<=complement_x;elsif(a0='0'and a1='1')then dout<=complement_x_negative;end if;end if;

end process;end Behavioral;

multiplier_booth_8bitadder:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity multiplier_booth_8bitadder isPort (clk,rst:in std_logic;ain,bin:in std_logic_vector(7 downto 0);sout:out std_logic_vector(8 downto 0));

end multiplier_booth_8bitadder;architecture Behavioral of multiplier_booth_8bitadder is

beginprocess(clk,rst,ain,bin)

beginif(rst='1')then sout<="000000000";elsif(rst='0'and clk='0')thensout<=(ain(7) & ain)+(bin(7) & bin); --符号位扩展加法end if;

end process;end Behavioral;

设计注意点:

1.求补码的方法:

if(din(7)='1')then reg8b(8 downto 1)<=(din(7)&(not din(6 downto 0)))+1;

else reg8b(8 downto 1)<=din;

end if;

--取补码2.求和时符号位拓展:

sout<=(ain(7) & ain)+(bin(7) & bin); --符号位扩展加法这篇关于西电计科大三下SOC微体系结构设计作业合集的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!