本文主要是介绍存储器层次结构(1),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

我们知道,一个简单的计算机系统模型是CPU执行指令,而存储器为CPU存放指令和数据。

在简单模型中,存储器系统是一个线性的字节数组,CPU能够在常数时间范围内访问每个存储器位置。这样的一个简单模型并不能有效地反映现代系统实际工作的方式。

实际上,存储器系统是一个具有不同容量,成本和访问时间的存储设备的层次结构。CPU寄存器保存着最常用的数据。靠近CPU的小的快速的高速缓存存储器作为一部分存储在相对慢速的主存储器(简称主存)中的数据和指令的缓冲区。主存暂时存放 存储在容量较大的慢速的磁盘上的数据。而这些磁盘又常常作为存储在通过网络连接的其他机器的磁盘或磁带上的的数据的缓冲区域。

值得注意的是,高速缓存存储器是作为CPU和主存之间的缓存区域,它们对应用程序的性能影响最大。

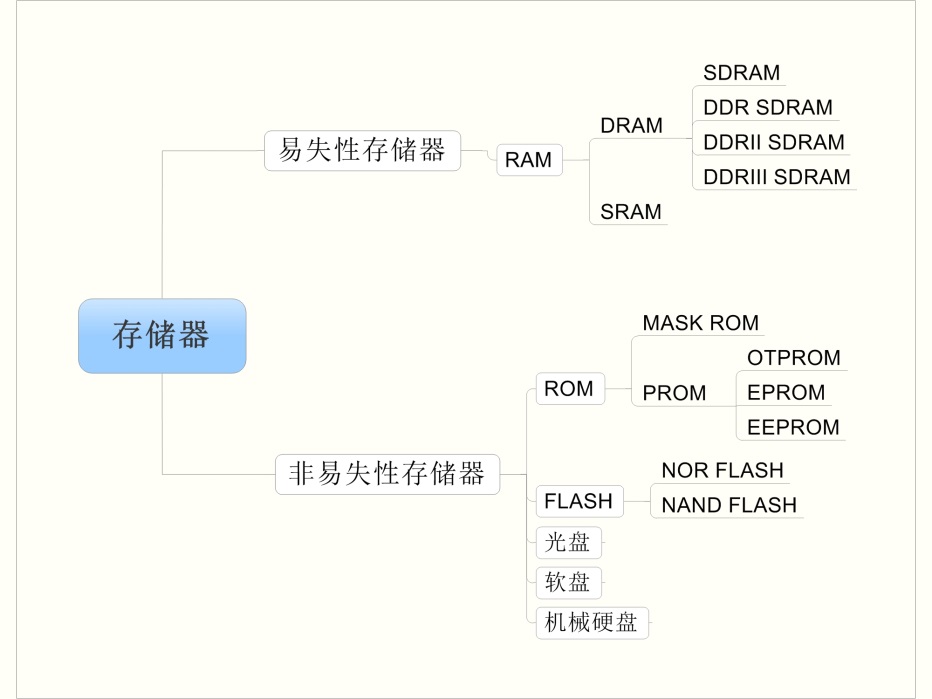

存储技术:

1.随机访问存储器(RAM): 随机访问存储器分为两类,静态的(SRAM)和动态的(DRAM)。静态的比动态的快,但是也贵的多。

SRAM用来作为高速缓存存储器,既可以在CPU上,也可以在CPU下。 DRAM用来作为主存,也用来作为图形系统的帧缓冲区。典型地,一个桌面系统的SRAM不会超过几兆,但是DRAM却有几百兆或者几千兆。

为了更好的说明DRAM和SRAM的特性和差异,在这里做个对比:

a. SRAM将每个位存储在一个双稳态的存储器单元里。每个单元是用一个六晶体管电路来实现的。这个电路有这样一个属性,它可以无限期地保持在两个不同的电压配置或状态之一。它的稳定性很好,也就是说,只要有电,它就会永远保持地保持它的值。即使有干扰(例如电子噪音),来扰乱电压,当干扰消除时,电路就会恢复到稳定值。

b. DRAM 将每个位存储为对一个电容的充电,这个电容非常的小。DRAM存储器可以制造得非常密集: 每个单元由一个电容和一个访问晶体管组成。但是,与SRAM不同,DRAM存储器单元对干扰非常敏感,当电容的电压被扰乱之后,它就永远不会恢复了。暴露在光线下会导致电容电压改变。很多原因导致漏电,使得DRAM过阵子又会失去电荷,所以它是不连续的。存储器系统必须周期性地通过读出,然后重写来刷新存储器的每一位。

c.SRAM 不需要刷新,它的存取比DRAM快,对诸如光和电噪声这样的干扰不敏感。代价是,SRAM比DRAM使用更多的晶体管,因而密集度更低而且更贵功耗更大。

好了,基于上面的简单介绍,下面我们来讨论一下传统的DRAM:

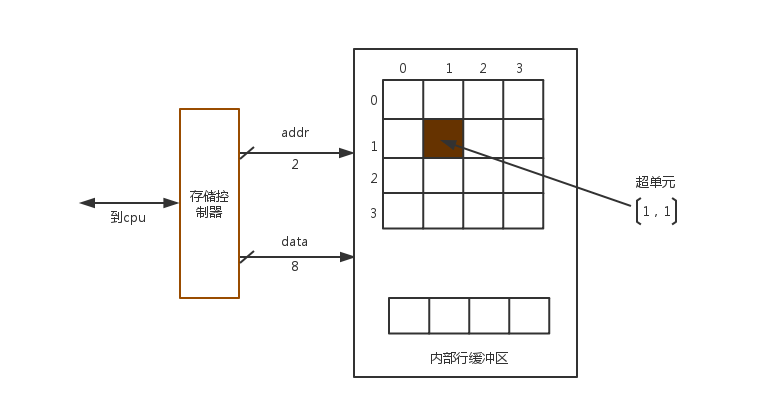

DRAM 芯片中的单元是 :位.

DRAM中的所有位被分成d个超单元.

每个超单元都由w个位组成.

也就是说,一个d×w的DRAM总共存储了dw位信息.每个超单元有形如(i,j)的地址,这里i表示行,j表示列。

信息通过引脚的外部连接器流入和流出芯片,每个引脚携带一个位的信号。2位的行和列超单元地址由2个addr引脚携带。

下面一个128位的16×8的DRAM芯片的高级视图,带阴影的方框表示(1,1)处的超单元:

其中,有d=16个超单元,每个超单元有w=8位。

每个DRAM芯片被连接到某个称为 存储控制器的电路,这个电路可以一次传送w位(一个超单元的内容)到每个DRAM芯片或一次从每个DRAM传出w位。

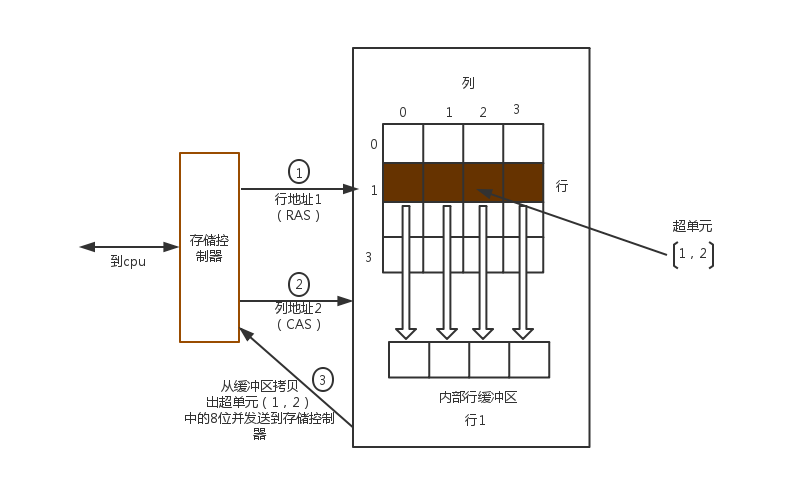

为了描述这个传送和传出过程,我简单做了一个过程说明图,如下:

存储控制器将行地址发送DRAM,然后是列地址。DRAM把超单元(1,2)的内容发给控制器作为响应。

另外,注意RAS和CAS请求共享相同的DRAM地址引脚。电路设计者们将DRAM组织成二维阵列而不是线性数组的一个原因是降低芯片上引脚的数量,它的缺点是必须分两步发送地址,这增加了访问时间。

这篇关于存储器层次结构(1)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!