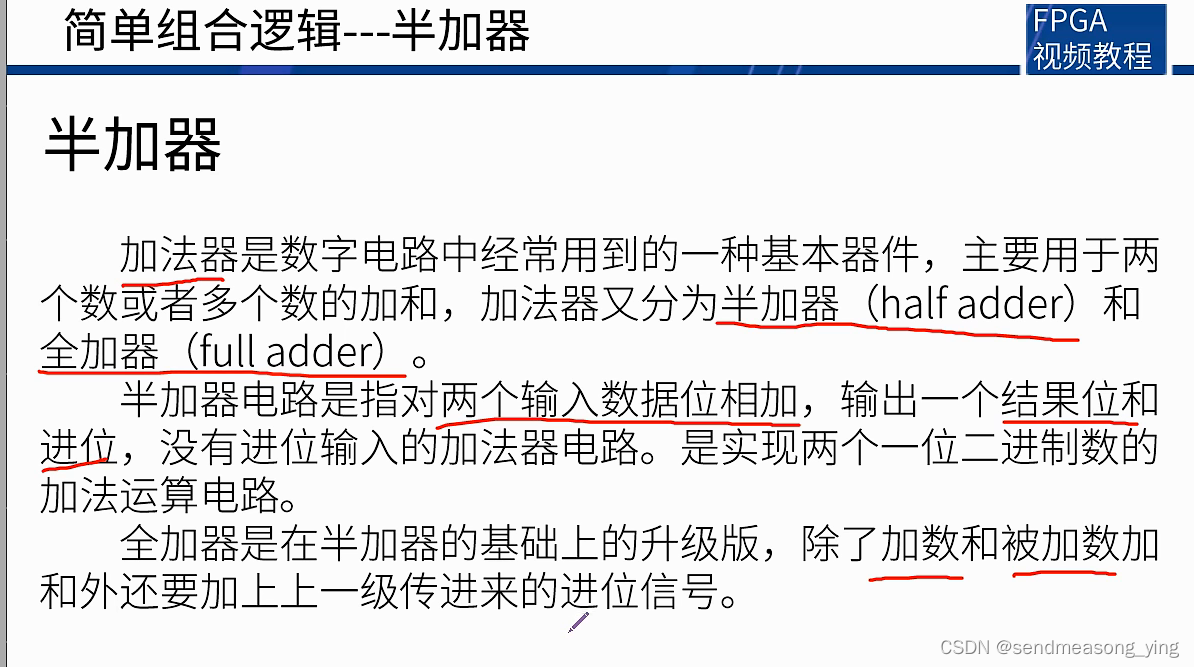

本文主要是介绍半加器___,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1.原理

2.代码

2.1 half_adder.v

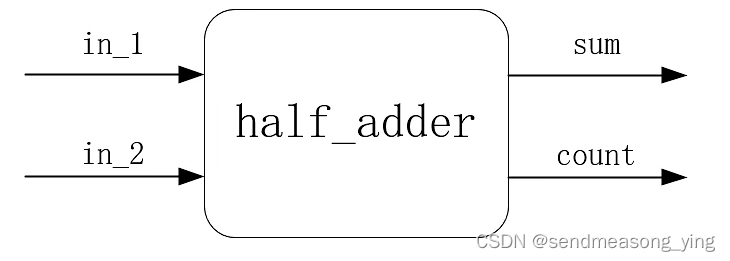

module half_adder

(input wire in_1 ,input wire in_2 ,output wire sum ,output wire count );assign {count,sum}=in_1+in_2;endmodule2.2 tb_half_adder.v

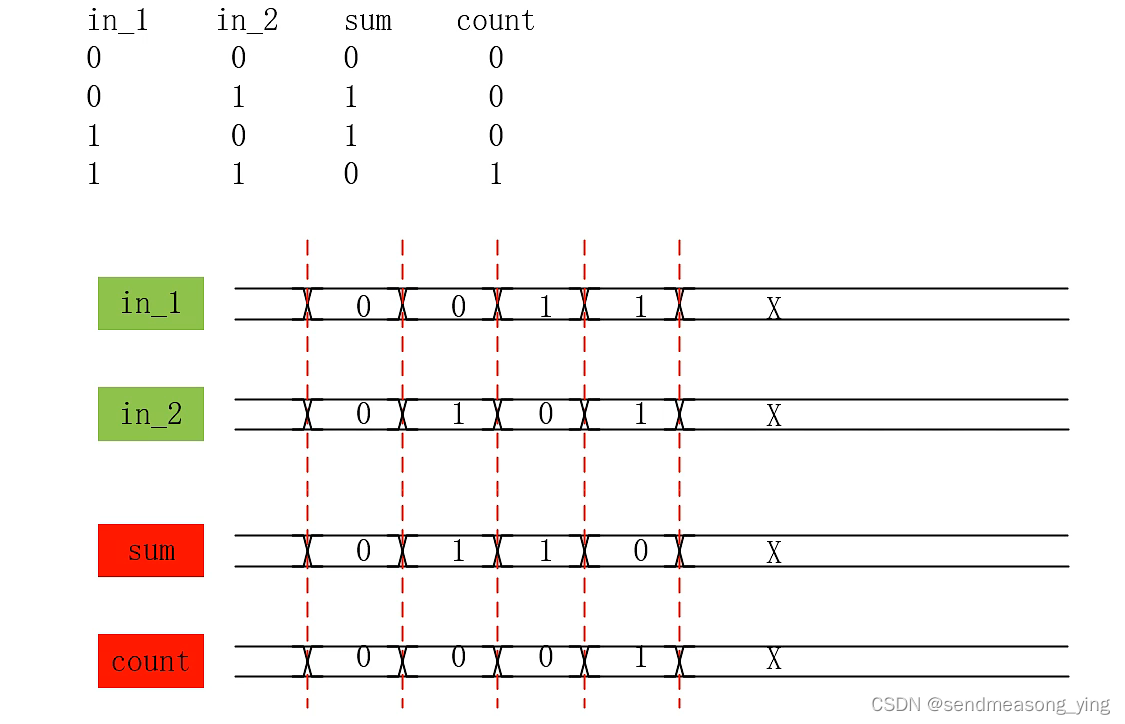

`timescale 1ns/1nsmodule tb_half_adder();reg in_1;

reg in_2;wire sum;

wire count;initial beginin_1<=1'b0;in_2<=1'b0;endalways# 10 in_1={$random}%2;

always# 10 in_2={$random}%2;initialbegin$timeformat(-9,0,"ns",6);$monitor("@time %t:in_1=%b,in_2=%b,sum=%b,count=%b",$time,in_1,in_2,sum,count);endhalf_adder half_adder_inst

(.in_1 (in_1),.in_2 (in_2),.sum (sum),.count (count)

);endmodule

这篇关于半加器___的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!