本文主要是介绍【STA】多场景时序检查学习记录,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

单周期路径

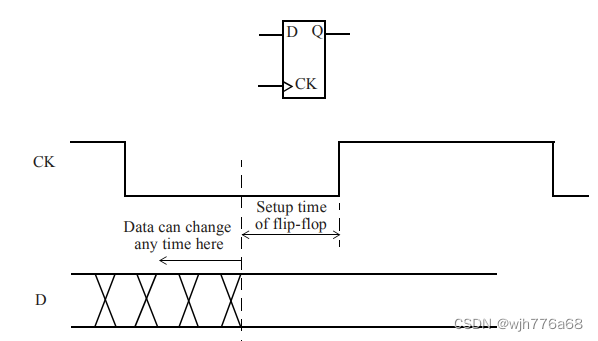

建立时间时序检查

在时钟的有效沿到达触发器之前,数据应在一定时间内保持稳定,这段时间即触发器的建立

时间。满足建立时间要求将确保数据可靠地被捕获到触发器中。

建立时间检查是从发起触发器中时钟的第一个有效沿到捕获触发器中时钟后面最接近的那个有效沿。

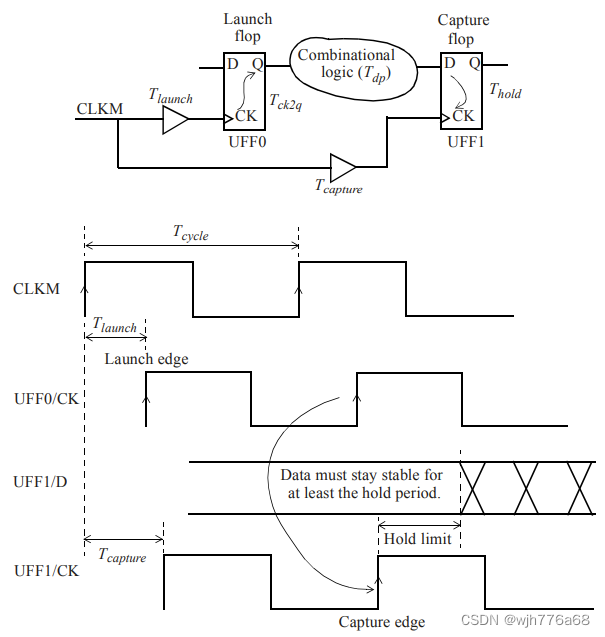

触发器到触发器路径

建立时间检查可以用数学公式表示:

Tlaunch + Tck2q + Tdp < Tcapture + Tcycle - Tsetup

其中Tlaunch是发起触发器UFF0的时钟树延迟,Tdp是组合逻辑数据路径的延迟,Tcycle是时钟周期,Tcapture是捕获触发器UFF1的时钟树延迟。

触发器间可能存在多条路径,每条路径均需满足建立时间的要求,这等价于在延时最高的工作条件(PVT)下,触发器间的最长时序路径需要满足建立时间的要求。因此在时序报告中建立时间用-max表示。

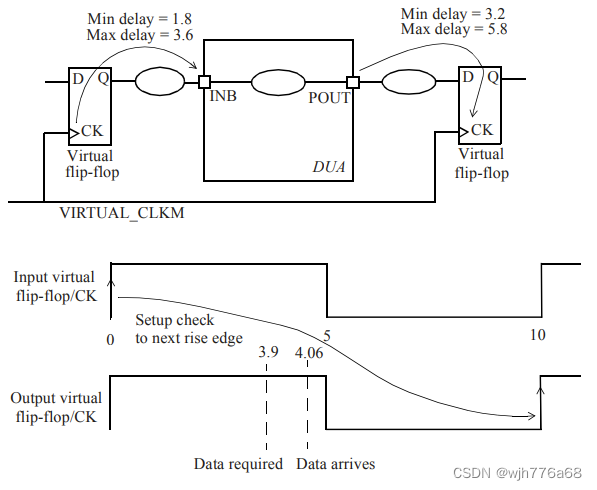

输入引脚到触发器路径

输入引脚数据采用虚拟时钟发出

输入引脚数据采用实际时钟发出

触发器到输出引脚路径

输出引脚数据采用虚拟时钟捕获

输入引脚到输出引脚路径(组合逻辑路径)

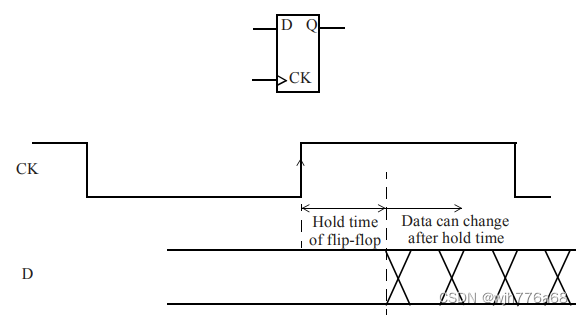

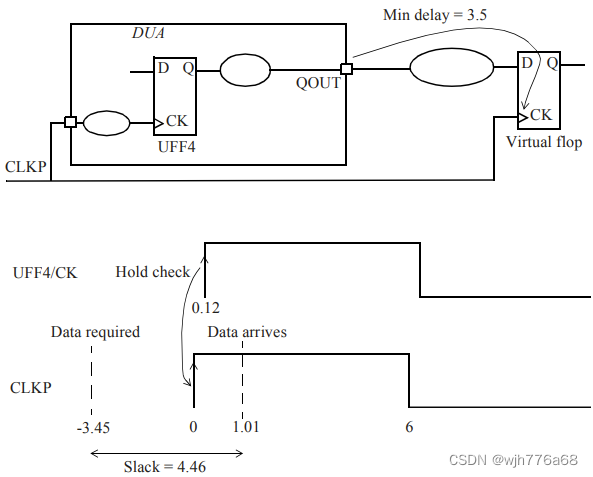

保持时间时序检查

触发器的保持时间要求规定在时钟的有效沿之后的指定时间段内,被锁存的数据应保持稳定。

保持时间检查可确保正在变化的触发器输出值不会传递到捕获触发器,并在捕获触发器有机会捕获其原始值之前覆盖其输出。

触发器到触发器路径

保持时间检查可以用数学公式表示为:

Tlaunch + Tck2q + Tdp > Tcapture + Thold

其中Tlaunch是发起触发器的时钟树延迟,Tdp是组合逻辑数据路径中的延迟,Tcapture是捕获触发器的时钟树延迟。换句话说,由时钟边沿发起的数据到达捕获触发器D引脚所需的总时间必须大于时钟同一边沿到达捕获触发器所需的时间加上保持时间。这样可以确保UFF1 / D保持稳定状态,直到触发器的时钟引脚UFF1 / CK时钟上升沿之后的保持时间为止。

触发器间可能存在多条路径,每条路径均需满足保持时间的要求,这等价于在延时最低的工作条件(PVT)下,触发器间的最短时序路径需要满足保持时间的要求。因此在时序报告中建立时间用-min表示。

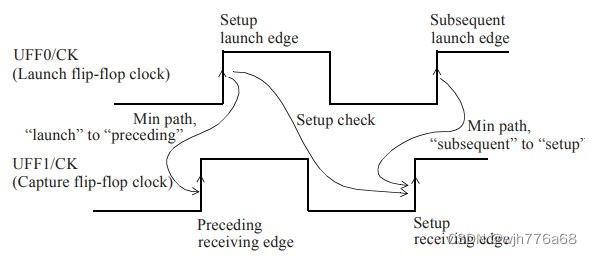

保持时间检查需要确保:

- 当前数据发起时钟沿(Setup launch edge)的下一个(subsequent)时钟沿发起的数据不被当前数据捕获时钟沿(Setup receiving edge)所捕获。

- 当前数据发起时钟沿发起的数据不被当前数据捕获时钟沿的前一个(Preceding)时钟沿所捕获。

触发器到输出引脚路径

输出引脚数据采用已知时钟捕获

多周期路径

两个触发器之间的数据路径可能需要一个以上的时钟周期才能传播通过逻辑。在这种情况下,这条组合逻辑路径会被定义为多周期路径。这意味着设计中后继触发器每隔多个周期才会使用一次前级触发器输出引脚上的数据,而不是每个周期都使用。

create_clock -name CLKM -period 10 [get_ports CLKM]

set_multicycle_path 3 -setup -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

set_multicycle_path 2 -hold -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

伪路径

-

利用已知/可预测时钟对信号采样时,尽量用多周期路径代替伪路径约束。

-

尽量不用-through复杂性高。

-

若要在两个时钟域之间设置伪路径,使用get_clocks效率更高:

set_false_path -from [get_clocks clockA] -to [get_clocks clockB]

代替

set_false_path -from [get_pins {regA_ * }/CK] -to [get_pins {regB_ * }/D]

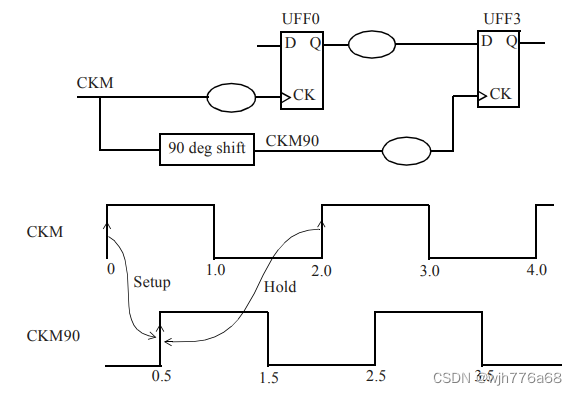

半周期路径

设计中同时具有负边沿触发的触发器(有效时钟沿为下降沿)和正边沿触发的触发器(有效时钟沿为上升沿),则设计中可能存在半周期路径。

半周期路径的建立时间、保持时间捕获时钟沿与发起时钟沿偏移均为半个时钟周期。

撤销时间检查

撤销时间检查用于确保在有效时钟沿与释放异步控制信号之间有足够的时间。类似于保持时间检查。

恢复时间检查

恢复时间检查用于确保异步信号变为无效状态的时刻与下一个有效时钟沿之间的时间间隔大于一个最

小值。类似于建立时间检查。

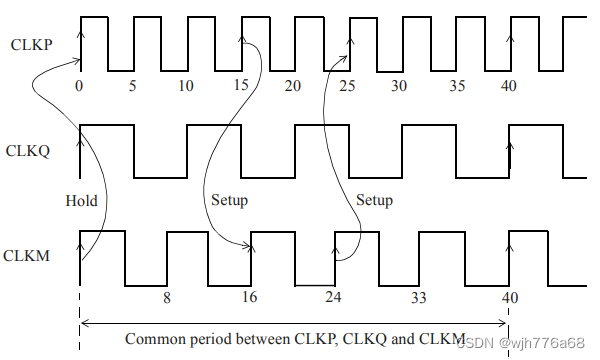

跨时钟域

当数据发起触发器和捕获触发器的时钟频率不同时,STA会首先确定一个公共基本周期(common base period)。快时钟的时钟周期会被延拓,以便获得两个时钟的一段公共周期。

慢时钟到快时钟

对于nMHz的慢时钟到4nMHz的快时钟数据传输:

假设该设计的目的是在CLKP的每隔第4个捕获沿上捕获数据,且数据发起沿后数据会发生变动,即需要将保持时间检查一直移回到数据发起沿所在位置,对应波形图如下:

对应上述波形图可使用的多周期约束如下。

set_multicycle_path 4 -setup -from [get_clocks CLKM] -to [get_clocks CLKP] -end

set_multicycle_path 3 -hold -from [get_clocks CLKM] -to [get_clocks CLKP] -end

其中-end表示依照捕获时钟沿,默认情况下-setup使用-start即发起时钟沿,-hold使用-end即捕获时钟沿。使用-end时会从默认的捕获时钟沿开始前移指定倍数周期,使用-start会从默认的发起时钟沿后移指定倍数周期。

快时钟到慢时钟

如果设计能够支持放宽建立时间检查要求,为数据路径提供两个快时钟周期,此时波形图如下:

此时多周期路径约束如下:

set_multicycle_path 2 -setup -from [get_clocks CLKP] -to [get_clocks CLKM] -start

set_multicycle_path 1 -hold -from [get_clocks CLKP] -to [get_clocks CLKM] -start

多时钟域

不同频率

- 整数倍:设计中多个时钟的频率是彼此的整数倍。在这种情况下,会通过计算所有相关时钟之间的公共基本周期,以便所有时钟同步。

- 非整数倍:对于两个频率不是彼此整数倍的时钟域之间存在数据路径的情况,时序分析会先计算相关时钟的公共周期,然后再将时钟扩展到该公共周期。之后,建立时间检查在时钟发起沿和捕获沿之间的最短时间内进行(根据建立时间不等式,两沿最短时检查最严格)。保持时间检查在发起时钟沿对应捕获时钟沿的前一周期与当前发起时钟沿最小时进行。

不同相位

这篇关于【STA】多场景时序检查学习记录的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!