本文主要是介绍《低功耗方法学》翻译——附录A:睡眠晶体管设计,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

附录A:睡眠晶体管设计

休眠晶体管是PMOS或NMOS高VT晶体管,用于在待机模式下关闭设计部件的电源。PMOS休眠晶体管用于切换VDD电源,因此被称为“header开关”。NMOS休眠晶体管控制VSS电源,因此被称为“footer开关”。在90 nm及以下的设计中,由于同时实施header和footer开关时,电压裕度较小且面积太大,因此使用header或footer开关。

虽然休眠晶体管的概念是直截了当的,但由于休眠晶体管及其实现对设计性能、面积、布线性、总体功耗和信号/功率完整性的各种影响,最佳休眠晶体管的设计和实现是一个挑战。

优化的休眠晶体管设计还取决于设计的具体目标和选择的CMOS技术和工艺。需要做出许多决定,包括选择header或footer开关、正向或反向体偏置、最佳晶体管尺寸以及布局实现细节,例如用于永久电源连接的单行或双行和额外导轨或直接通孔柱(via pillar)。

这一章是关于不同选择的优点和权衡的指南,而不是晶体管设计者非常了解的设计程序。在功率门控设计背景下,对各种休眠晶体管特性的研究都是基于SPICE分析,而不是理论和方程。在小于90 nm的技术中,器件建模变得如此复杂,因此基于工艺参数的器件模型是高质量工业试验设计的最佳分析工具。

A.1 睡眠晶体管设计指标

睡眠晶体管的设计质量有三个测量标准:开关效率,面积效率以及IR降。睡眠晶体管可以在栅极长度,宽度,通道数量(finger size)和体偏压等方面优化以达到高的开关和面积效率,以及较低的泄漏电流和IR降。

A.1.1 开关效率

睡眠晶体管的效率(开关效率)由漏极开启和关闭状态下的电流比值来定义,即 Ion/Ioff。期望最大化效率以在正常操作中实现高驱动并且在睡眠模式中实现低泄漏。休眠晶体管效率随栅极长度(L)、宽度(W)和体偏压(Vbb)而变化。L、W和Vbb的最佳值随技术和工艺的不同而变化。通过在SPICE中通过扫描L、W和Vbb并在每种情况下测量Ion/Ioff的开关效率分析来获得这些最优值。

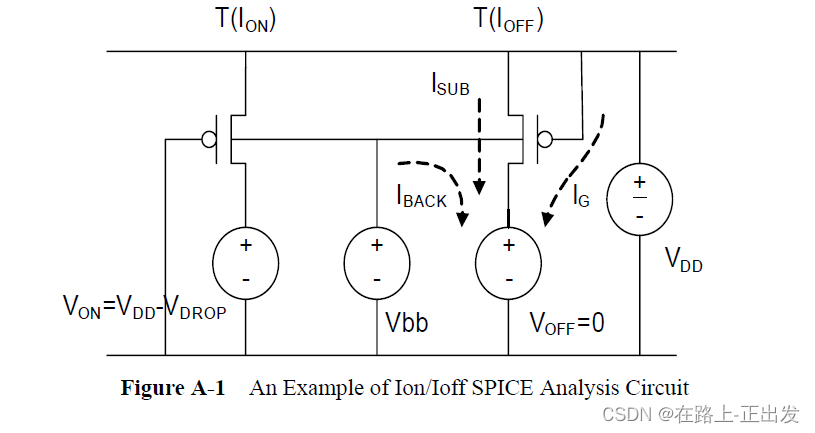

Ion/Ioff 的SPICE分析电路示例如图A-1所示。

该电路由两个高VT晶体管组成,这两个晶体管分别配置在导通和截止状态。两个晶体管的主体都被偏置在Vbb,这在SPICE分析中被扫频。导通状态晶体管T(Ion)配置用于Ion分析。电压源Von被添加到特定IR下降目标(例如10mV)处的偏置Vds。它还用于测量Ion的漏极电流。栅极漏电流不包括在Ion中,因为它对电源门控设计中的逻辑操作的驱动电流没有贡献。在导通状态晶体管上设置125°C的高温,以模拟工作模式下的高芯片温度。

截止状态晶体管被配置用于截止分析。在这种情况下,插入一个零电压源Voff来测量漏电流作为Ioff。由于在截止配置中,晶体管的源极、栅极和体(body,【附】关与晶体管的body:简述NMOS和PMOS晶体管的区别差异-IC先生 (mrchip.cn))都偏置在Vdd或以上,所以漏电流收集所有主要的泄漏电流,包括栅隧道电流Ig、亚阈值沟道电流、栅感应漏极泄露(GIDL)电流和漏-衬底带到带隧道电流(BTBT)。在设计处于休眠模式时,关断状态晶体管的室温被设置为25℃以反映冷却情况。

在功率门控设计中,晶体管的栅极可以由反相器在逻辑“1”和“0”状态下驱动,反映了功率门控设计中的实际驱动情况,但这不是NEC必需的。反相器的极小VDS(约10 mV)对导通和关断晶体管的VGS几乎没有影响,因此仿真结果的误差可以忽略不计。

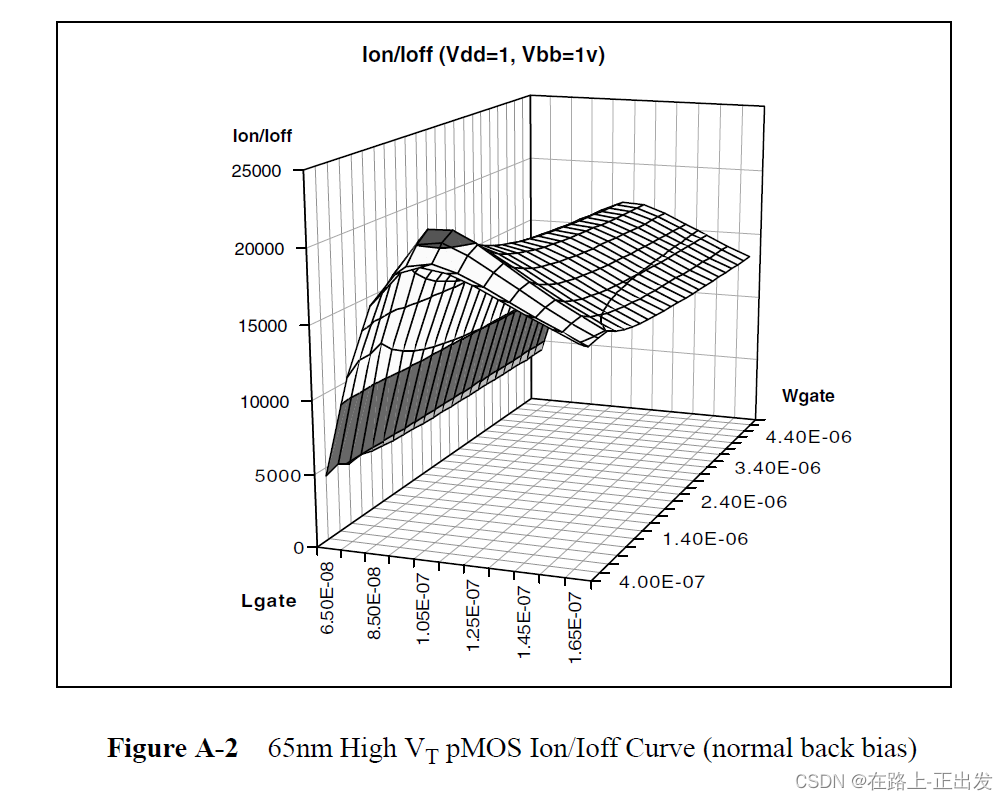

图A-2展示了一个开关效率曲线的例子。这条曲线显示了一个65 nm高VT的PMOS晶体管在标称或普通工艺中。在SoC设计中,Vbb被偏置在对应于正常体偏压条件的Vdd处。栅极长度和宽度分别从65 nm扫描到165 nm和0.4um扫描到5um。

开关效率随L的增大而增大,在L=105 nm时达到峰值,这主要是由于随着L的增大,阈值以下漏电流呈指数级减小,Ion线性减小(在线性区域)。

然而,当L的长度超过105 nm时,效率下降,这是因为L进入了Vth增加饱和但沟道电阻继续增加的区域,因此Ioff的降低变得不如Ion的下降显著。

效率还取决于栅宽。图A-2中的Ion/Ioff曲线显示,在1.4um以下的窄栅宽时,Ion/Ioff相对较高,峰值在W=1um处。这主要是由于窄栅宽对VT的边缘效应。在亚微米窄栅宽晶体管中,窄宽效应变得复杂,导致亚微米窄栅宽晶体管中出现异常的Ion/Ioff行为。在1.8um以下,Ion/Ioff对栅宽变得不敏感。

开关效率还取决于体偏压。反转体偏压(RBB)提高了VR,从而减少了亚阈值泄漏,从而导致更高的开关效率。RBB的影响因技术和工艺而异,特别是在亚90 nm节点。通过对图A-1中电路在不同体偏压下的SPICE分析,评估体偏压对所选技术和工艺中开关效率的影响是很重要的。图A-3给出了1.4V体偏压下65 nm高VT PMOS晶体管的分析结果。

结果表明,与正常体偏压情况下的最大Ion/Ioff相比,1.4V体偏压下的Ion/Ioff增加了16%。此外,与正常体偏置情况下的105nm相比,最大Ion/Ioff发生在85nm的较小栅极宽度处。因此,在反向体偏压的情况下,相同驱动电流的休眠晶体管更小、更高效。然而,增加体偏置超过最佳值将导致Ion/Ioff减少。这是因为在高RBB下VT降低变得不那么显著,这导致亚阈值泄漏电流的降低较慢。另一方面,BTBT漏电流随着RBB的增加而增加,并且由于RBB在头部基底连接处产生的高电场而在高RBB时占主导地位。

A.1.2 面积效率

休眠晶体管的面积效率是由其驱动电流与硅面积之比定义的,即Ion/Asleep。Ion是当晶体管处于导通状态时的漏电流,并且偏置在等于IR下降目标的VDS处。Asleep是睡眠晶体管的硅面积,取决于栅极长度(L)、宽度(W)和布局实现。为了产生所需的驱动电流,睡眠晶体管通常通过以多指方式连接多个小晶体管来设计。由于设计规则,如热阱间距和扩散间距规则,应用于休眠晶体管的版图实现,并影响面积效率。本章后面将详细讨论面积效率的设计。

A.1.3 IR降

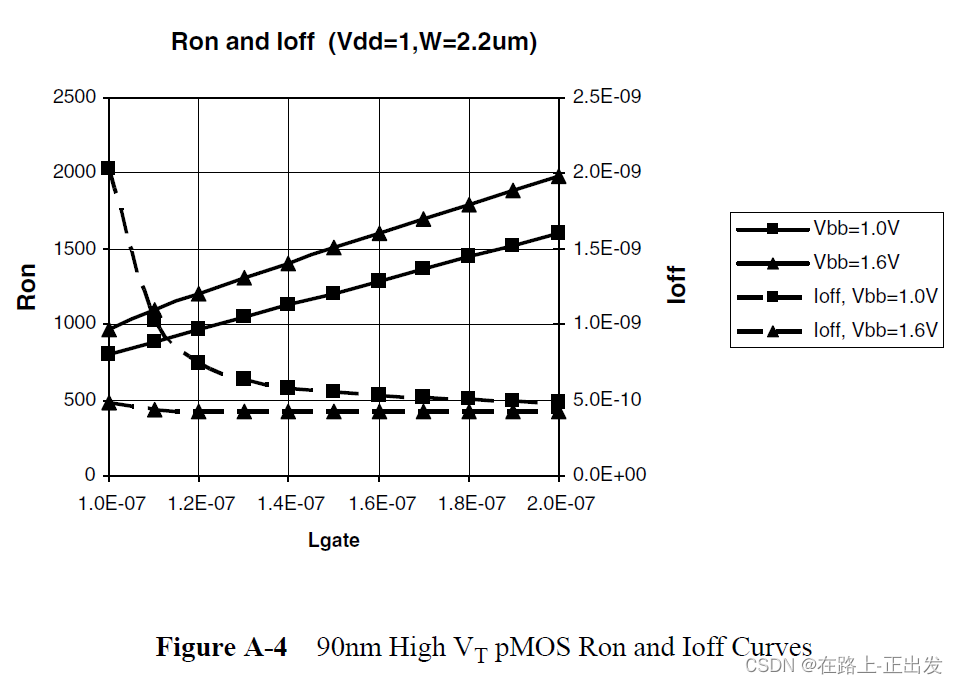

休眠晶体管导通时的IR降主要由等效沟道电阻(RON VDS/Ion)决定,RON越小,IR降越小,栅宽是决定RON的主要参数。在对应于休眠晶体管导通状态的亚50 mV VDS区域中,RON随栅长度和体偏压线性增加,如图A-4中的实线所示。这是在典型工艺中的2.2um宽PMOS高VT晶体管的结果。

从图A-4中的RON和漏电流曲线可以看出,在相同的漏电流0.5nA(三角形和正方形标记的虚线)下,100 nm Lgate和1.6V体偏压的睡眠晶体管的RON为1K欧姆(三角形标记的实线),而180 nm Lgate和正常(1V)体偏压的睡眠晶体管的RON为1.5K欧姆(正方形标记的实线),这表明在正常体偏压下,反向体偏压下短栅的RON通常比长栅的RON小。

A.1.4 正向体偏置与反向体偏置

通过在PMOS休眠晶体管的永久Vdd导轨和NMOS晶体管的永久Vss导轨上连接衬底或阱,可以正常地偏置休眠晶体管的衬底,也可以通过连接到高于PMOS晶体管的Vdd和低于NMOS晶体管的Vss的单独的偏置电压来进行反向偏置。

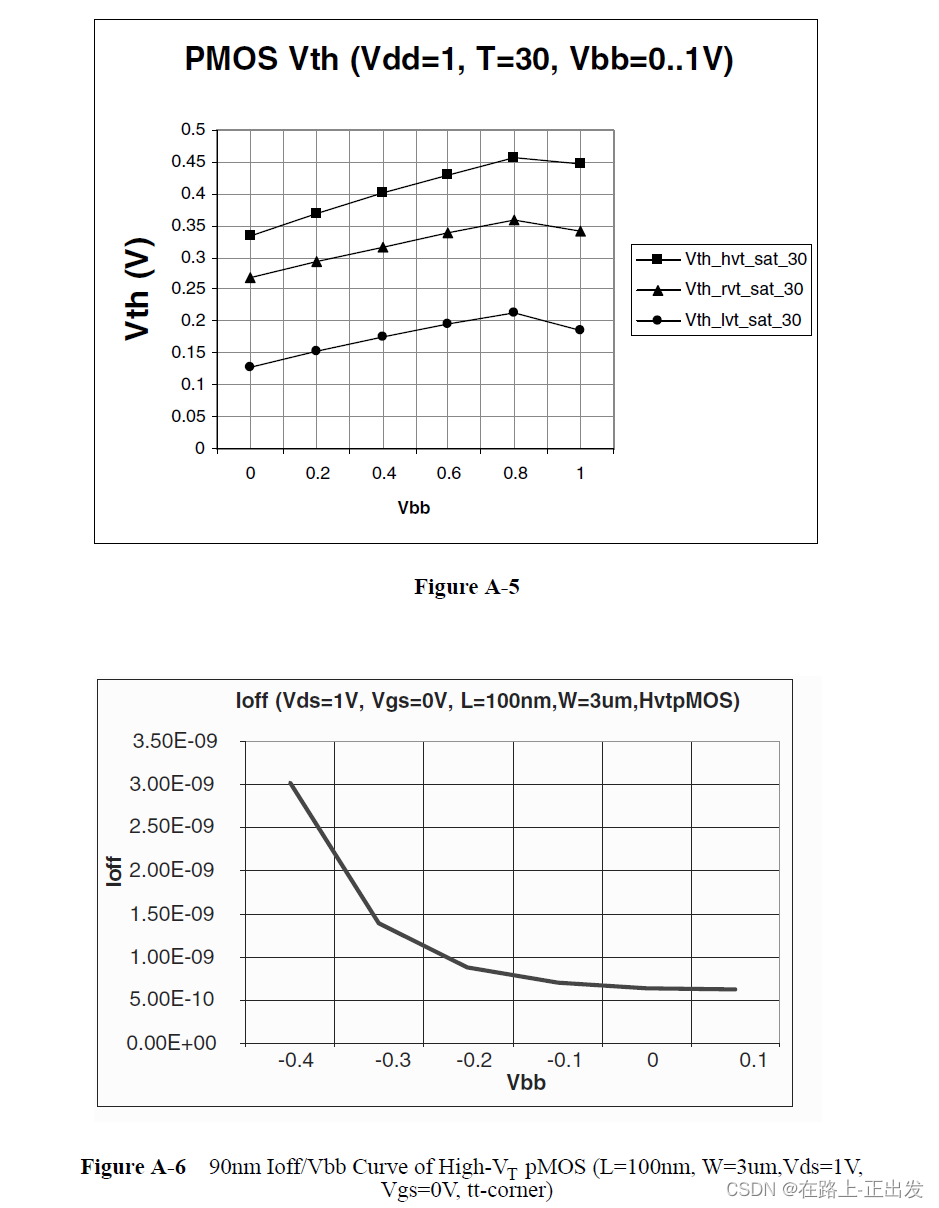

如图A-6中的Ioff/Vbb曲线所示,晶体管的漏电流随着反向体偏压的增加而减小。漏电流的减少主要是由于保留体偏压使Vth增加所致。

正向体偏置的主要优点是实现简单。不需要特殊的偏置电压源或偏置电源分布。另一方面,在分接单元实现中,反向体偏置通常导致更高的开关效率、更低的漏电和更小的面积。正向或反向体偏置的选择取决于下面讨论的设计目标和折衷。

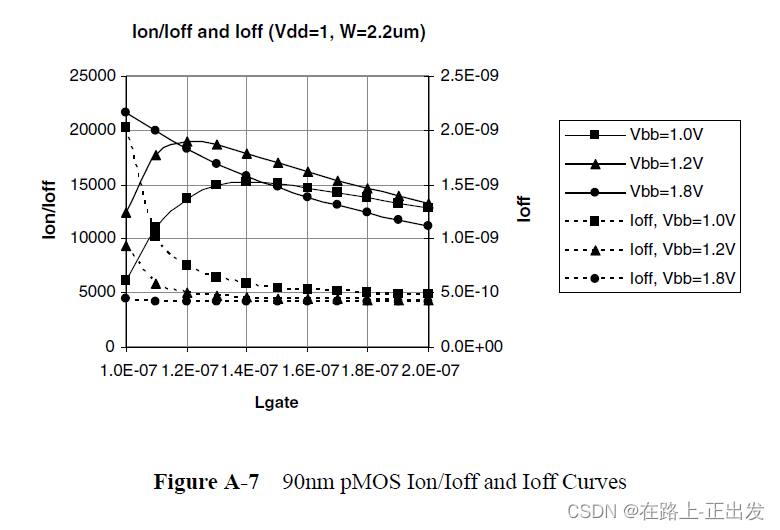

Ioff随VT的增大而指数减小,而Ion随Vth的增大而线性减小。因此,对于给定的技术和工艺,我们可以找到获得最大开关效率(Ion/Ioff)的最佳VT。VT随着栅长(L)和反向体偏置(VBB)的增加而增加。最佳Vth可以由L和Vbb的最佳组合产生。找到最佳Vbb和L的最佳方法是进行SPICE模拟,并分析不同Vbb和L下的Ion/Ioff。图A-6和图A-7分别显示了高Vth PMOS晶体管在90 nm工艺和65 nm工艺下的开关效率和Ioff曲线。晶体管宽度为2.2 um,VDS偏置为1.0V。

在一个典型的工艺中(图A-7),最大Ion/Ioff随着Vbb的增加而增加,在Vbb为1.8V、栅长为100 nm时达到峰值~22,000。与L=140 nm的正常体偏压下的最大Ion/Ioff约15,000相比,提高了43%。Ioff也降低了23%。在这种情况下,反向体偏压下的短沟道休眠晶体管比正常体偏压下的长沟道晶体管是更好的选择。

然而,在65 nm的PMOS晶体管中,施加反向体偏置的优势变得非常小,如图A-8所示。与在反向体偏压(Vbb=1.4V,L=85 nm)下的最大Ion/Ioff为21000和在正正体偏压(Vbb=1.0V,L=105 nm)下的~18000相比,开关效率的提高下降到15%,Ioff减少率也降低到9.8%。这种影响减小的主要原因是65 nm工艺中BTBT的泄漏电流显著增加,在BTBT的代价增加的情况下,通常使用强晕状掺杂技术来减少短沟效应和亚阈值泄漏电流随着工艺规模的扩大。Tox的减少会导致更高的GIDL,而GIDL不会随着RBB而下降。因此,BTBT和GIDL泄漏电流正在成为RBB的主要漏电流,并且在亚45 nm工艺中,应用RBB对改善Ion/Ioff的效果将越来越差。

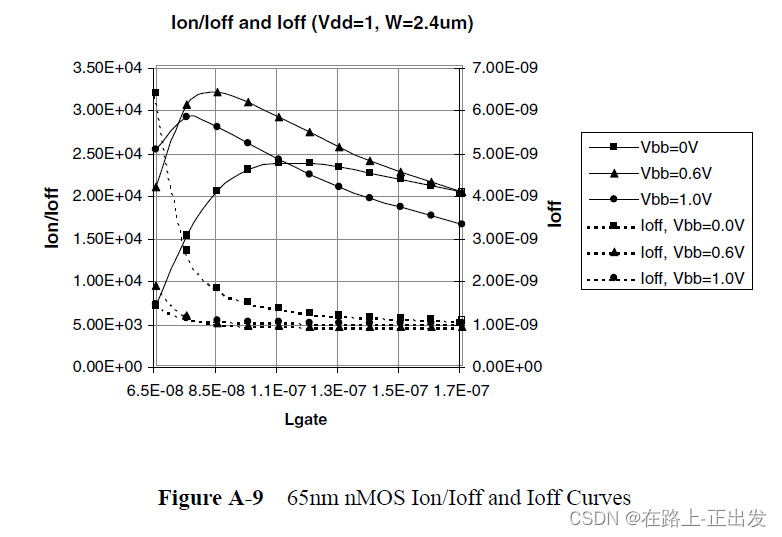

值得一提的是,nMOS晶体管表现不同。图A-9显示了65nm工艺的nMOS开关效率曲线。将栅极长度为85nm的反向体偏置晶体管的Ion/Ioff与栅极长度为105nm的正常体偏置晶体管进行比较,表明反向体偏置仍然产生比正常体偏置高34%的Ion/Iff。Ioff也提高了33%。随着技术规模在65nm以下,越来越多的复杂工艺,如NMOS/PMOS沟道工程和晕掺杂,已被应用于器件,以解决短沟道效应、泄漏控制和功率延迟产品改进等领域的关键问题。这种复杂的过程显著地改变了晶体管的行为并使器件建模复杂化。因此,对设计特定的器件进行SPICE分析以获得真实的晶体管特性是至关重要的。

反向体偏置休眠晶体管的优点包括比正常偏置休眠晶体管更小的尺寸,因为它具有更高的Ion/(L*W)比。

此外,在相同的漏电流下,反向体偏压睡眠晶体管具有更小的RON,因此比正常体偏压对应部分具有更小的IR降。

反向体偏置技术的另一个优点是,它适用于在不同模式下调节偏置电压以优化漏电流和性能,例如在待机模式下施加反向体偏置以最小化泄漏电流,在正常工作模式下施加正常或正向体偏压以产生最大驱动电流。这种自适应体偏置方法进一步显著地提高了Ion/Ioff。

然而,反向主体偏置方法引入了以下显著的权衡:

首先,它需要在设计的电源电压范围之外的单独的VBB电压源,例如在header开关实现中的VBB>Vdd。

其次,它需要在设计中为每个休眠晶体管提供专用的Vbb分布。需要仔细规划Vbb网络,以防止噪声对其造成影响,因为Vbb中的噪声会导致显著的Vth和小区域性能变化。

第三,在footer开关实现中需要昂贵的三阱工艺来在NMOS休眠晶体管中创建单独的P阱。这在header开关中不是问题。

最后,在休眠晶体管和相邻的标准单元之间施加热阱间隔规则,这一边界在小型休眠晶体管的设计中变得非常重要。

另一方面,正常的体偏压应用不需要体偏压源和偏置分布,只需简单地抽头连接到永久电压,在无抽头标准单元设计中,睡眠晶体管和标准单元可以很好地共享,从而消除了井间距的限制,睡眠晶体管的阱与标准单元的阱抽头互相间隔。

A.1.5 建议

- 我们建议在选定的库中对高VT晶体管运行SPICE,以分析体偏压效应,该效应在不同的技术、工艺和铸造厂中有很大差异。

- 如果最大限度地减少泄漏是首要考虑的问题,那么反向体偏置是正确的选择。

- 在90 nm工艺中,反向偏置通常是一个很好的选择,因为它比正常偏置更低的漏电和面积开销。在65 nm工艺中,优势变得非常小,其中正常体偏压下的长栅睡眠晶体管可能比反向体偏压选择更好。在正常和反向体偏压设计中,应该根据设计特定目标和权衡的总体考虑来做出决定。

- 如果很难获得单独的电压源,无论是片上还是片外,那么应该选择正常的体偏压。

- 如果电源门控设计选择了footer开关,则应使用正常体偏压,除非标准单元库支持NMOS休眠晶体管中的单独P阱连接以施加反向体偏压。

- 如果使用无抽头的标准单元库,则正常体偏压睡眠晶体管因其比反向体偏压睡眠晶体管更高的面积效率而变得可观。

- 在反转体偏置休眠晶体管应用中,休眠晶体管的主体(例如PMOS的N阱)必须与其相邻的标准单元的主体具有良好的间隔(热井间隔规则),以防止由于休眠晶体管和标准单元处的主体偏置电位不同而可能发生的闭锁事件。

- 在使用无抽头标准单元库的正常体偏置休眠晶体管应用中,当设计处于休眠模式时,标准单元中的PMOS和NMOS晶体管的主体必须分别分接到永久VDD和VSS以保持作为休眠晶体管的安全偏置电压。另一方面,对于那些使用标准单元库的应用,其中主体已经连接到标准单元中的晶体管的源极,休眠晶体管的主体必须以与反转主体偏置休眠晶体管设计相同的方式与标准单元分开,这是因为标准单元的主体将在footer门控设计中浮动到VDD,并且在休眠模式中在header门控设计中浮动到Vss,从而在休眠晶体管和标准单元之间产生较大的偏置电势差。

A.2 为面积效率进行的布局设计

面积效率取决于休眠晶体管的尺寸(L*W)和版图实现。最优的L由开关效率决定,并可以从SPICE分析产生的开关效率曲线中获得。一旦定义了L,面积效率主要由晶体管宽度W和布局实现决定。为获得高面积效率的最优休眠晶体管尺寸(L*EW)的方法已在第四章中描述,因此这里不再重复。一旦休眠晶体管的尺寸(L*EW)确定,休眠晶体管的面积效率取决于下文描述的布局实现。

版图实现中有两个影响面积效率的设计规则。第一个规则是有源区间距规则,它定义了两个晶体管扩散区之间的最小间距。这在版图实现中引入了并行小W晶体管行之间的面积开销。第二个规则是热阱间距规则,它定义了由于休眠晶体管和标准单元中不同的井偏置电压,从反向体偏置睡眠晶体管中的N沟道到相邻标准单元中的N沟道的最小距离。在休眠晶体管中引入面积开销的间距规则如图A-10所示。

为了减少间隔开销对面积效率的影响,我们可以增加休眠晶体管的尺寸以减小间隔开销与休眠晶体管的比率。这意味着休眠晶体管的水平尺寸需要足够大以减轻单元两侧的间隔开销的影响,而W应该足够大以避免多行以消除扩散间隔开销。如果标准单元库被设计为在单元中没有单独的阱抽头(无抽头单元),那么,由于休眠晶体管和标准单元共享良好抽头并且在相同电压(永久Vdd)下偏置,所以势垒间隔规则变得不适用于正常体偏压休眠晶体管。

值得注意的是,如图A-8中的虚线所示,Ion随W线性增加。因此,在给定的L和Vbb时,Ion/W变得恒定,这意味着一旦L和Vbb被定义,面积效率主要由休眠晶体管的版图实现决定。

A.2.1 建议

- 如果面积效率很关键,则在休眠晶体管布局实现中,对于给定的单元高度,应选择尽可能大的W,以形成单行并行晶体管。

- 如果最小待机漏电流是首要目标,那么最优的W(通常较小)应该被考虑以获得高开关效率和低泄漏。值得一提的是,随着W的减小,开关效率和漏电流都变得对工艺变化更加敏感,特别是在800 nm以下的区域。

- 对于折衷面积和漏极目标,通过SPICE分析研究不同W的休眠晶体管的面积和漏极权衡,可以得到最优的W。

- 更大的休眠晶体管(L*ΣW)更具面积效率,因为上方的间隔对面积效率的影响较小。

- 如果在电源网络中将休眠晶体管实现为菊花链(稍后详细描述),则优选地将控制休眠晶体管的中继器与休眠晶体管一起实现为单个开关单元以提高面积效率,因为休眠晶体管和中继器之间的间隔不需要遵循热井间隔规则。

- 休眠晶体管通常在两个菊花链中实现,这将在本章的休眠晶体管实现一节中详细说明。在唤醒时,弱休眠晶体管链被打开,对虚拟电源网络进行涓滴充电,直到主链打开时,对网络进行完全充电。在这种情况下,我们建议在同一开关单元中实现弱休眠晶体管和主休眠晶体管,以避免因两个晶体管单独实现而产生的额外边界间隔开销。

A.3 单行与双行

为了高区域效率,休眠晶体管可以被设计为标准单元的两倍高。双行实现具有两个优点。首先,它消除了由两行之间的势垒间隔规则施加的空间,因为这两行被休眠晶体管的相同势垒占据。这在反转体偏置实现中尤其有效,在该反向体偏置实现中,“热阱”间隔是显著的。

其次,W可以延伸到两行高度,形成宽的单行晶体管阵列,因此具有高的面积效率。

双行实现的权衡是电池与标准电源和地线对齐的要求,这通常不难通过后端流程来处理。

单行和双行实现的选择还取决于休眠晶体管在设计的电源网络中的实现方式。在粗粒度的电网中放置较大的休眠晶体管通常比放置在细粒度网格中的较小的休眠晶体管更具面积效率,因为在较大的晶体管中间隔开销变得不那么显著。最大休眠晶体管尺寸和布局网格受本地休眠晶体管驱动的电网中心的布线性和IR降的影响。

A.3.1 建议

- 如果选择反向体偏置休眠晶体管,双行实现是正确的选择。Vdd应该在两行的中间,以便W可以扩展到两行。

- 在无抽头标准单元设计中,如果睡眠晶体管是正常偏置的,并且放置在小电网上,那么单行布局是一个很好的选择。

- 然而,如果使用分接单元标准单元库,那么即使使用正常的体偏置休眠晶体管,双行实现通常也会产生更高的区域效率。这是因为分接单元的N阱连接到虚拟电源网络,而休眠晶体管的N阱连接到永久电源网络。在休眠模式中,标准单元和休眠晶体管的阱在不同的电压下被偏置。因此,在反向偏置休眠晶体管应用中,以相同的方式对休眠晶体管和相邻标准单元之间的空间施加热井间距规则。

A.4 过冲电流和潜伏期分析

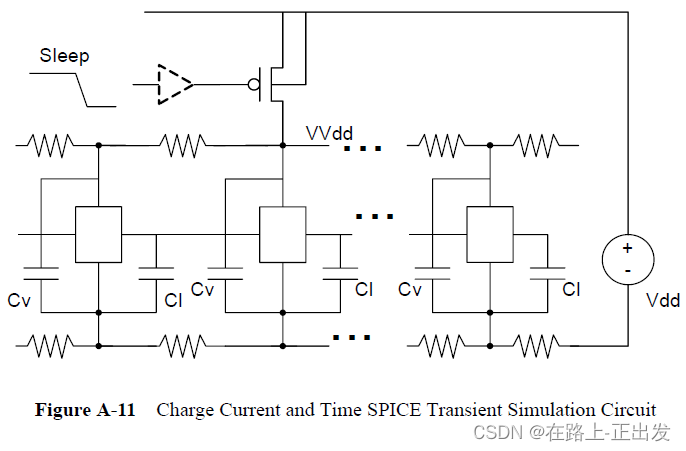

一种在滴流链和滴流链结构中获得所需尺寸的弱休眠晶体管的实用方法是运行SPICE暂态模拟来评估在定义的涓流电荷链中由不同栅宽的滴流充电晶体管驱动的单元块的充电电流和时间。然后,我们可以产生过冲电流和充电时间曲线,并从曲线中选择满足过冲电流和唤醒延迟要求的合适的栅宽。图A-11显示了这样一个评估电路的例子。

逻辑单元(如图A-11中框所示)是各种类型标准单元的集合。为了模拟唤醒期间休眠晶体管的瞬变行为和逻辑单元的电路,在评估电路中应使用逻辑单元的晶体管级模型。单元的数量由休眠晶体管驱动的休眠晶体管网络网格(如2行1列电源网格)的区域决定。电网电阻可以从具有类似电源线的现有设计的轨道提取获得。Cv对电源电容建模包括De-Cap。CI是单元驱动的负载电容。充电时间可以通过测量VVdd电压从0到99%Vdd的变化来获得。值得一提的是,在工业设计中,decap往往是电网电容的主导因素。因此,唤醒时间和过冲电流随decap的变化而变化很大。建议对decap进行较好的估计,并将其包含在唤醒过冲电流仿真中,以便仿真结果与最终设计相关联。

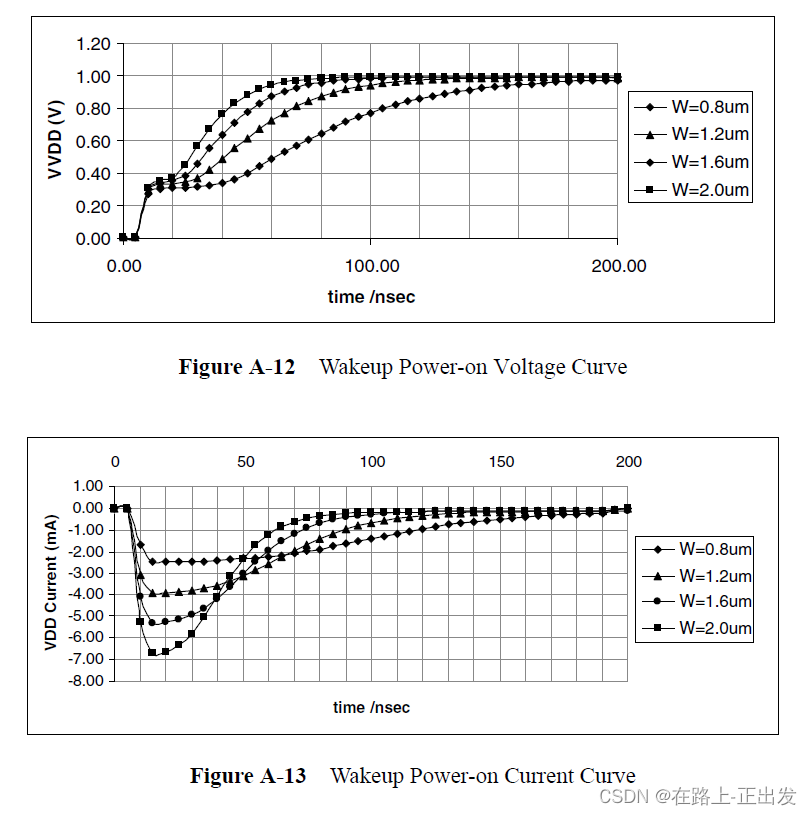

基于单网络的休眠晶体管评估模型对于初始评估是小而有效的。然而,它并不能准确地代表全尺寸功率门控,其中睡眠晶体管按顺序导通,每个导通晶体管驱动整个电力网络。因此,一旦完成初始评估,通常会建立一个更大尺寸的接近全尺寸设计的模型来进行最终功率门控评估。更大的模型可以通过将单个网格模型配置为具有缓冲链的休眠晶体管网络来构建,该缓冲链以定义的序列驱动休眠晶体管。图A-12和图A-13中的电压和电流曲线是这种电路的SPICE模拟结果,该电路具有由12个休眠晶体管驱动的6行乘40列的逻辑单元,每个休眠晶体管配置为驱动2行乘10列的逻辑单元格。结果表明,较小的晶体管具有较低的电流峰值,但需要更长的时间才能完全充电。基于过冲电流约束,可以从W扫描结果中获得最佳晶体管尺寸。

唤醒上电序列响应的小SPICE评估的缺点是它可能不能准确地反映芯片设计的上电行为,而芯片设计通常要大得多。幸运的是,先进的动态电力网络分析工具能够执行大型设计的暂态分析。对实际设计进行唤醒上电时序分析变得很实用,在这种情况下,电源网络、休眠晶体管和逻辑单元都可以从带有寄生的版图中提取出来,以便准确地分析唤醒过冲电流和充电时间。

这篇关于《低功耗方法学》翻译——附录A:睡眠晶体管设计的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!