本文主要是介绍FPGA IO命名与Bank划分,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- IO的命名

- IO物理命名

- IO功能命名

- Bank简介

- FPGA器件功能命名与Bank划分查找

- XILINX

- Intel

- LATTICE

IO的命名

IO物理命名

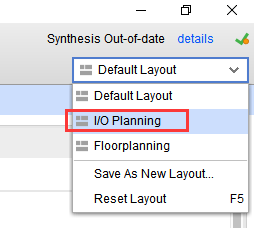

FPGA的IO物理命名规则,也就是我们做管脚约束时候的命名。芯片通常是长方体或者正方体,所以命名通常采用字母+数字组合的方式,从上到下是字母(A,B,C,D```),从左到右是数字(1,2,3```),所以诸如:W3(见下图,在Vivado中右上角选择l/O Planning即可调出封装图),就是图上箭头的位置。

IO功能命名

FPGA的功能命名规则。功能命名规则每个厂家都会自己的一套规则,但都大同小异,我们重点来讲述一下xilinx的命名。

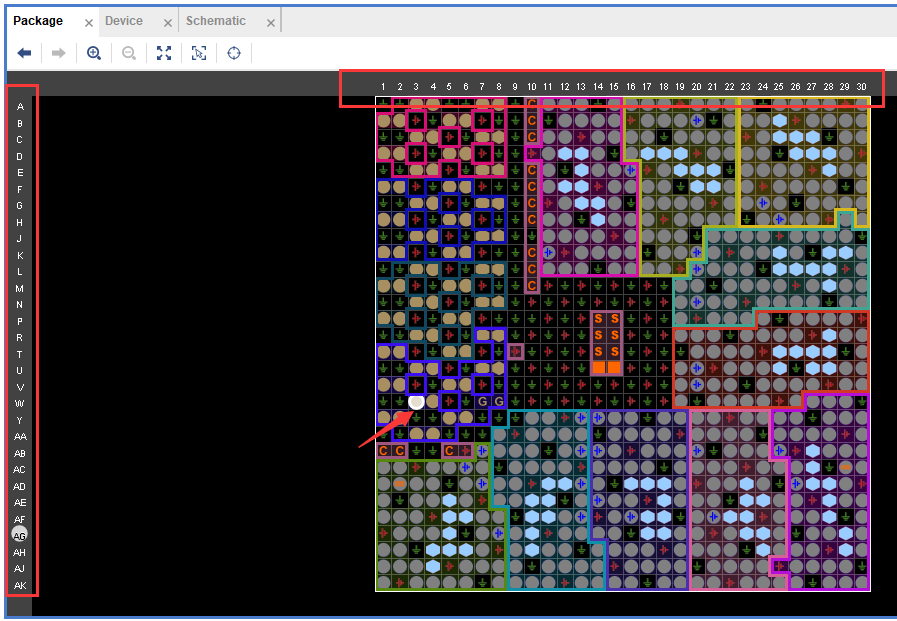

Xilinx 7系列FPGA的HR和HP bank,每个bank有50个I/O管脚,每个I/O管脚都可配置成输入、输出。每个bank的首尾管脚只能作为单端I/O,其余48个I/O则可配置成24对差分I/O。在差分信号的实现过程中,管脚分配应选择相应电平标准的bank中除首尾以外的其他48个IO。Xilinx 7系列的差分信号的实现主要通过IBUFDS、OBUFDS、IOBUFDS等原语的调用,在程序中直接进行原语的例化。【FPGA I/O之差分信号】

在下图中,我们可以看到红色圈住的两个单端信号,绿色线条圈住的_CC时钟管脚不用作时钟输入时可以作为用户I/O来使用,另外,还可以看到蓝色标记的VREF管脚,当该BANK I/O用作DDR内存接口时,需要提供伪差分所需的阈值电压,此时_VREF_管脚需要接DDR外设要求的参考电压。 Xilinx 7系列 FPGA硬件知识系列(三)—— Bank划分及引脚定义

通常xilinx 的功能命名格式为:

差分IO命名:IO_LXXXP_XXXX_#。其中:

(1) IO代表用户IO;

(2) L代表差分,XX代表在当前Bank下的唯一标识号,差分对编号不同的差分对具有不同的编号,P或N表示LVDS信号的差分正端或差分负端;

(3)XXXX位置表示该IO的一些功能;

(4) #表示Bank号,由于FPGA的IO参考电平是按照Bank进行供电的,所以差分对所在的Bank应尤其注意。

举例:IO_L13P_T2_MRCC_12,那通过功能命名的规则我们就可以知道,这是一个用户IO,支持差分信号,是Bank12的第13对差分的P端口,与此同时它也是全局时钟网络输入管脚(MRCC是全局时钟网络)。

单端IO命名:IO_#_#。其中:第1个#代表单端IO的编号;第2个#代表单端IO所在的Bank。

举例:IO_25_12,代表第25个单端IO,IO位于第12BANK。

Bank简介

为了便于管理和适应多种电器标准,FPGA 的 IOE 部分被划分为若干个组(Bank),Bank是一组物理位置和特性相近的IO的总称, 每个 Bank 的接口标准由其接口电压 VCCIO 决定,一个 Bank 只能有一种 VCCIO,但不同 Bank 的 VCCIO 可以不同。只有相同电气标准和物理特性的端口才能连接在一起,VCCIO 电压相同是接口标准的基本条件。同一Bank的电压的基准是一致的,因此,通常如果我们需要各种不同标准的电压,可以通过给到Bank的电压基准不同的方式来实现多种电平标准的输入输出。通常封装越大,Bank数量也越多,可以支持电压标准也越多。

HP Bank、HR Bank和HD Bank, 这几个概念都是在7系列之后才有的,其中7系列的FPGA中有HP Bank和HR Bank,UltraScale FPGA有HP Bank、HR Bank和HD Bank,但并不是一个FPGA中会同时包含HP/HR/HD Bank。

| Bank | 说明 |

|---|---|

| HP:High Performance | 应用于高性能也就是速度比较高的场景,比如DDR或者其它高速差分总线(不是gtx),由于速率比较高,Bank电压最高也只能到1.8V。 |

| HR:High Range | 表示支持wider range of I/O standards,最高能够支持到3.3V的电压。 |

| HD:High Density | 应用于低速I/O的场景,最高速率限制在250M以内,最高电压也是支持到3.3V。 |

FPGA器件功能命名与Bank划分查找

方法一:浏览器检索:器件名+ pinout。如:XC7K325T pinout,点击对应的官网链接进入。

方法二:在官网查找

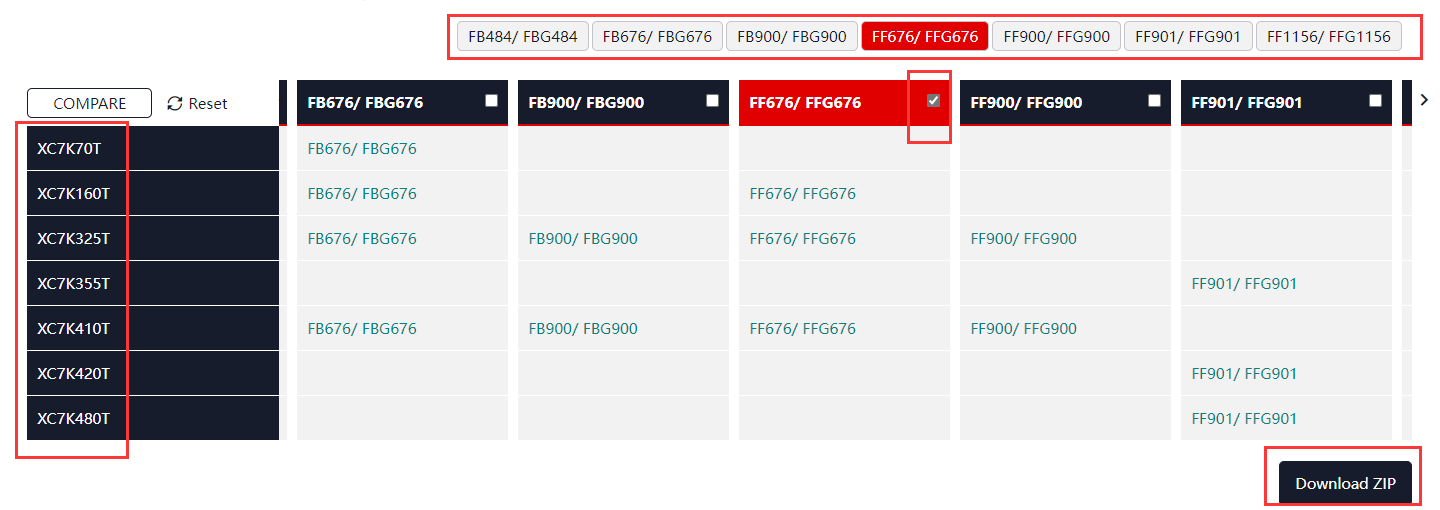

XILINX

XILINX:Package Files (xilinx.com)

Intel

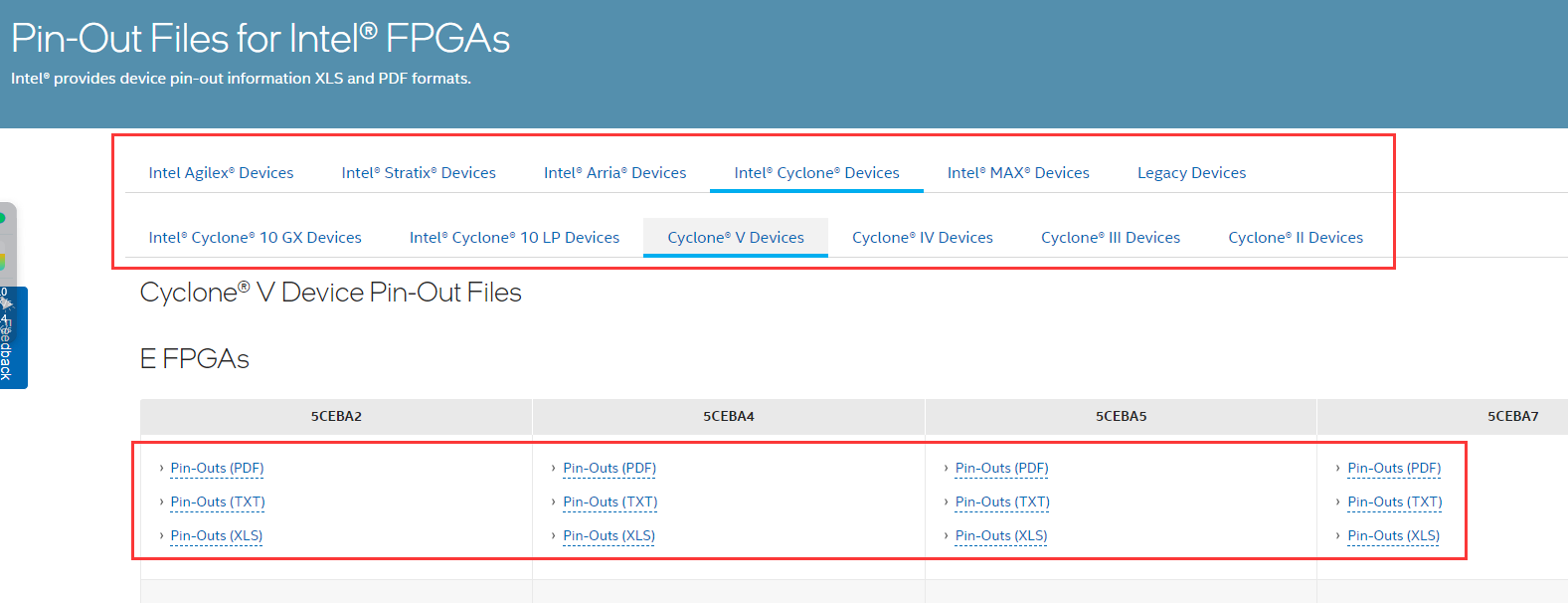

Intel:Pin-Out Files for Intel Field Programmable Gate Arrays (FPGAs) | Intel

LATTICE

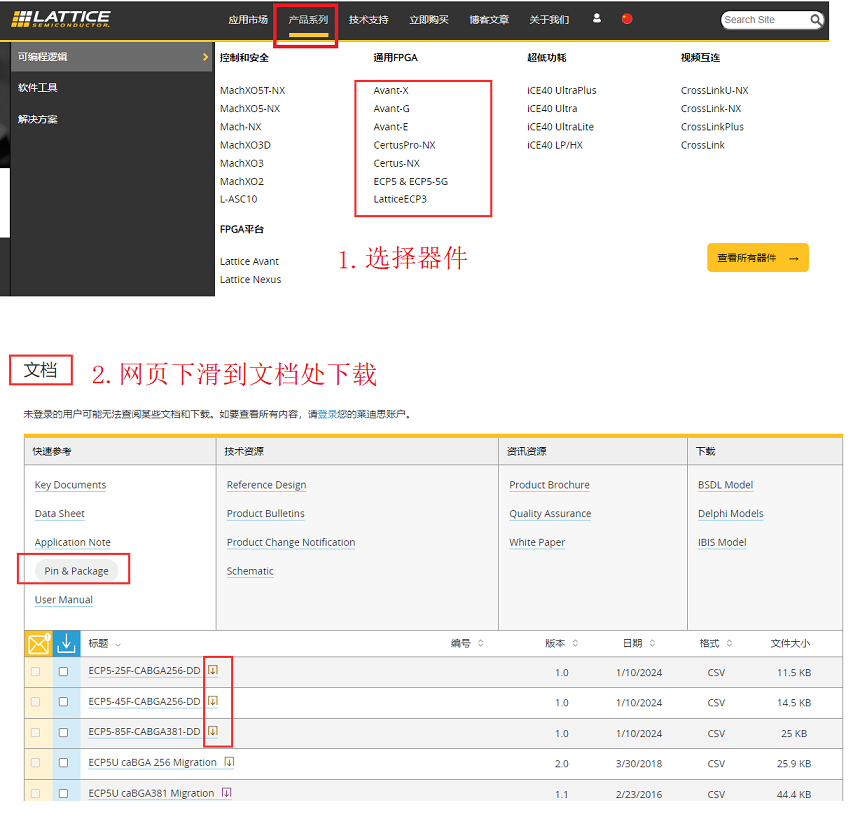

LATTICE:莱迪思产品 (latticesemi.com)

这篇关于FPGA IO命名与Bank划分的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!