本文主要是介绍1904_ARM Cortex M系列芯片特性小结,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1904_ARM Cortex M系列芯片特性小结

全部学习汇总: g_arm_cores: ARM内核的学习笔记 (gitee.com)

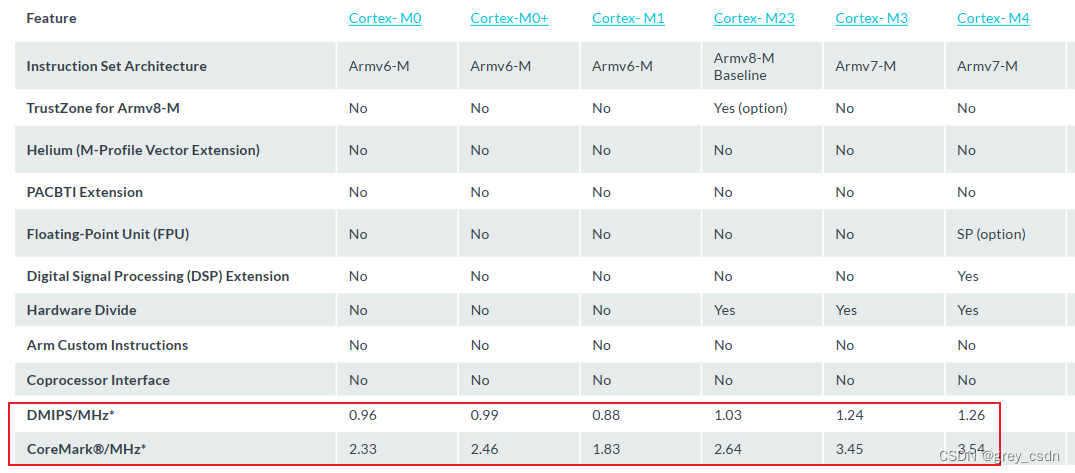

ARM Cortex M系列的MCU用过好几款了,也涉及到了不同的内核。不过,关于这些内核的基本的特性还是有些不了解。从ARM的官方网站上找来了一个对比表,结合我用过的一些体验做一个知识增补整理。

这个系列的MCU主要是面向功耗以及能耗比进行优化而设计出来的。具有低延迟以及高度的运行可确定性。

涉及到的指令集有v6m、v7m、v8m、v8.1m等。

以前听到过一个说法是M3与M4的软件兼容性好,可能是说指令集是相同的?或许,在满足了一定的使用条件约束之后,两者在二进制上都能够做到一定的通用度。

有两个Mx3的型号,以前看到这个以为M33是M3的加强版,现在看似乎是完全不同的设计。

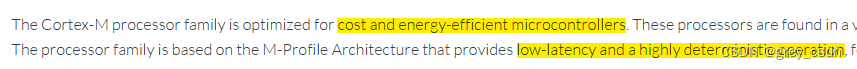

浮点处理单元FPU只有部分处理器上有。我接触过的架构现在有M0、M0+、M3、M4、M33、M7等。这几个接触过的内核中,只有M4、M33以及M7是有FPU可以选配的,而且只有M7可能选配双精度的支持。不过,M7的内核必然会有一个单精度的FPU支持。

这里增加一下浮点运算单元的几个缩写的解释。

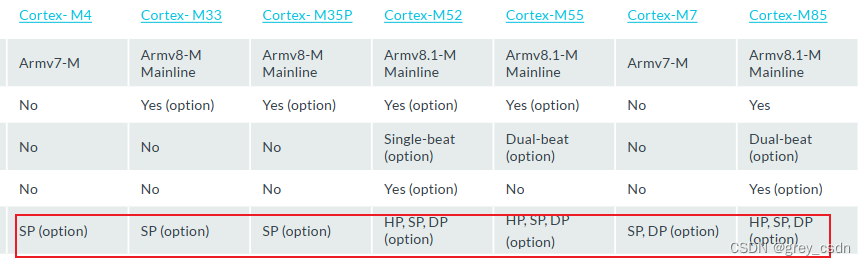

DSP的功能支持,在我用过的架构中,M4以及M7是支持的。而M33可能支持,这个是选配的。由此,M4、M7架构的MCU在我接触到的应用中使用很广泛,看起来也是有很多资本背书的。

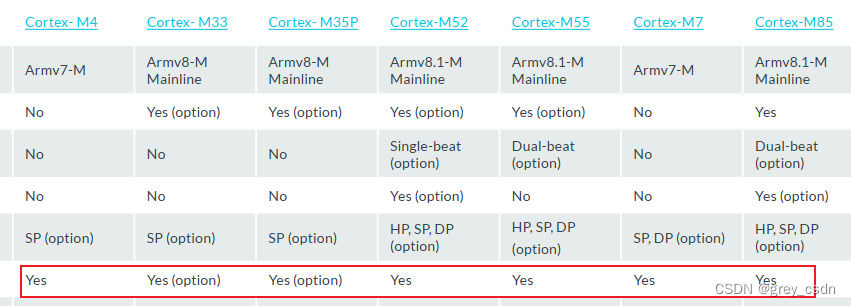

协处理器接口方面,我接触过的架构中只有M33是选配的。暂且不是很明确这种协处理器能够实现的作用是什么,都可以完成什么功能?

DMIPS以及CoreMark都是衡量MCU处理能力的参数,从这里看,其实并不是M后面的序号越大算力就越强。当然,从普遍规律上来看,大的趋势的确是如此。

还有几个其他的参数,分别是MPU、数据缓存双核锁步的支持。我用过的好几个架构都有MPU的支持,只是不同架构支持的保护区数目不同。M0+、M3、M4是支持8个保护区,而M33、M7支持16个保护区。数据缓存,在之前接触的这些MCU中,只有M7的存在数据缓存。锁步核的支持,也只存在于M7之上,这样很多功能安全的设计要求高的就只能选择M7内核的MCU了。

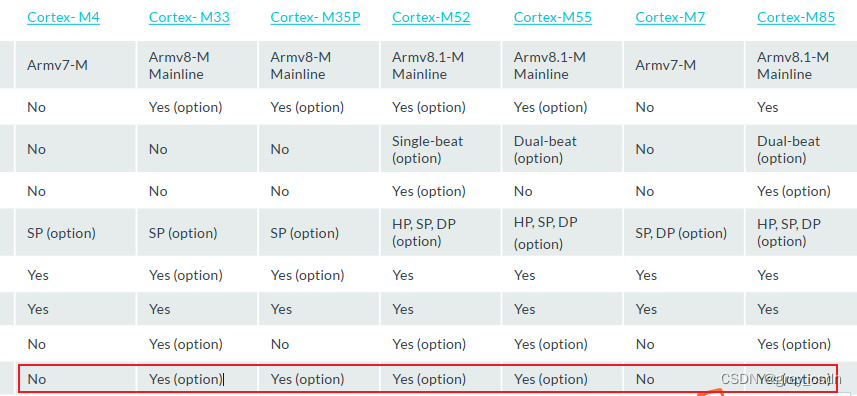

最后还有一个通用的认证,不知道跟加密验签等是否是一回事儿。不过我用过的芯片里面只有M33内核是支持的,而且实际的使用中并没有用到对应的功能。

以前整理过一个M0内核的了解资料,这样通过对这个表格的信息的整理,对我之前用过的一部分MCU的内核信息的了解算是又多了一些完善了。

这篇关于1904_ARM Cortex M系列芯片特性小结的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!