本文主要是介绍linux drm mipi dsi lcd 点屏之设备树配置,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

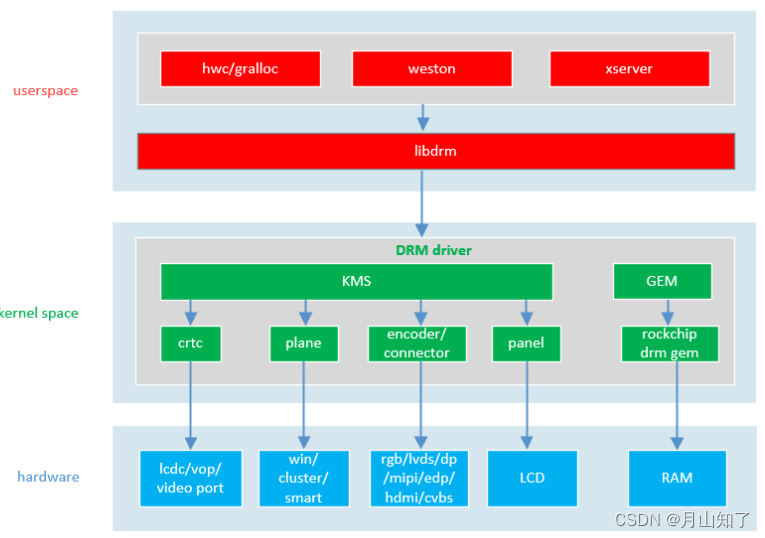

linux drm mipi dsi lcd 点屏之设备树配置

设备树文档:

https://elixir.bootlin.com/linux/v6.8-rc5/source/Documentation/devicetree/bindings/display/dsi-controller.yaml

https://elixir.bootlin.com/linux/v6.8-rc5/source/Documentation/devicetree/bindings/display/panel/display-timings.yaml

https://elixir.bootlin.com/linux/v6.8-rc5/source/Documentation/devicetree/bindings/display/panel/panel-timing.yaml

https://blog.csdn.net/lonely_fireworks/article/details/129362860

Android画面显示流程分析(1)–LCD时序

https://cloud.tencent.com/developer/article/1867373

Linux MIPI DSI LCD设备驱动开发调试细节学习笔记(一)

https://blog.csdn.net/qq_37858386/article/details/123705548

2022-03-24 RK3566 MIPI屏 调试记录,panel-init-sequence 命令格式介绍

驱动点屏:

1)屏幕pin引脚定义

2)panel-init-sequence初始化code

3)屏幕上电时序

4)display timing

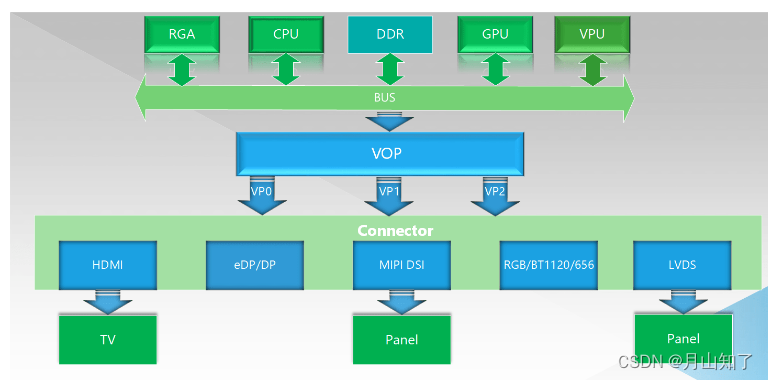

显示接口有:HDMI,eDP/DP,MIPI DSI,RGB、BT1120/656,LVDS等等

在android 设备上用的比较多的是MIPI DSI。

不同的显示接口点屏,需要参考相应设备树文档进行配置。

下面以mipi dsi接口连接lcd点屏进行举例。

panel-timing.yaml内容:

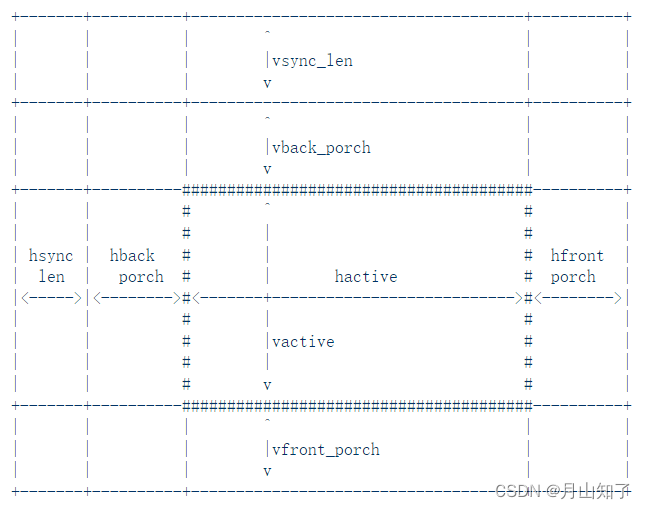

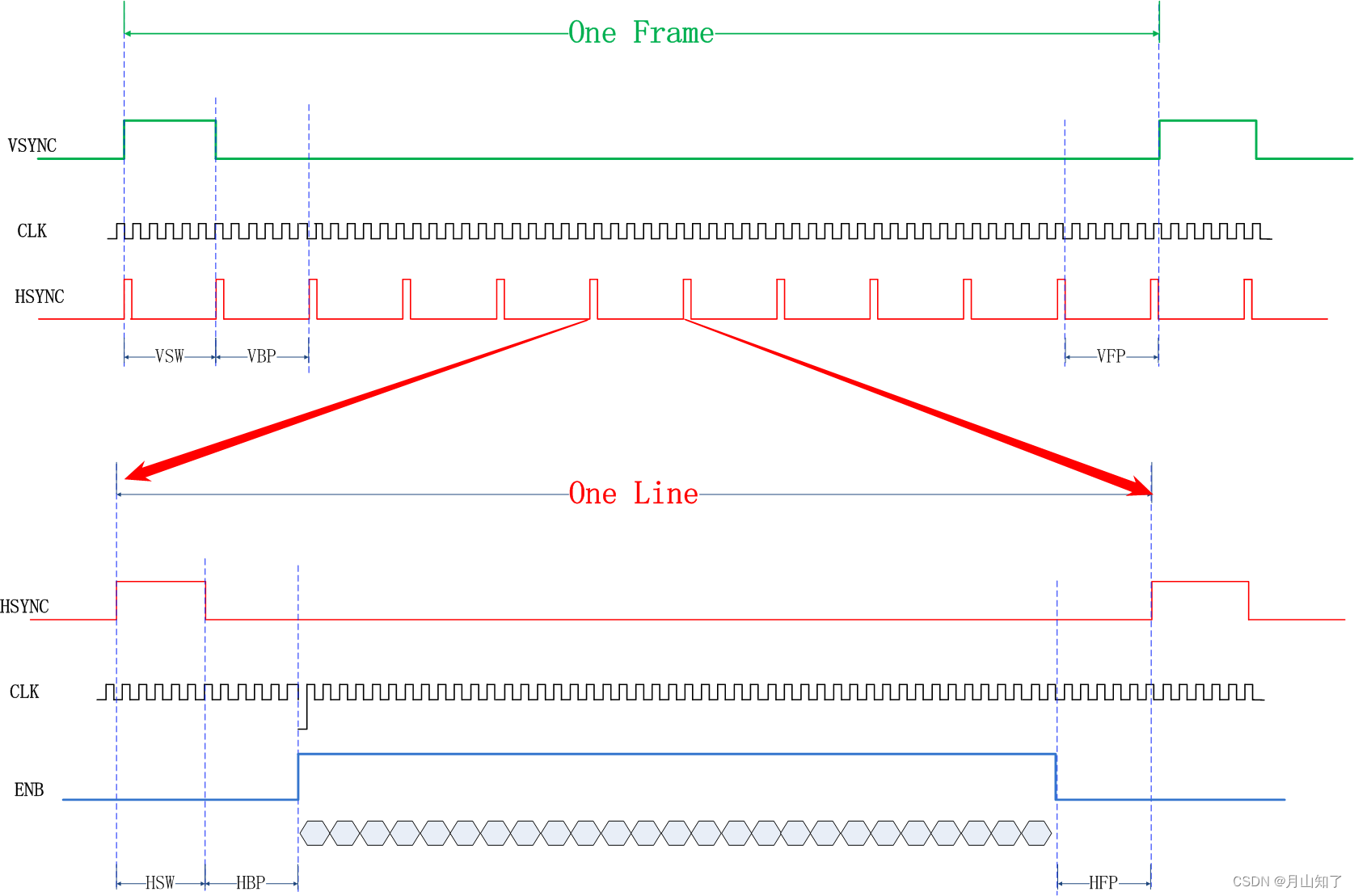

hback-porch (HBP):行信号左边沿无效信号时间范围

hfront-porch (HFP): 行信号右边沿无效信号时间范围

hsync-len (HPW): 行信号电子枪回扫时间 即 水平同步时间 Hsyc

vback-porch(VBP) :帧信号上边沿无效信号时间范围

vfront-porch(VFP):帧信号下边沿无效信号时间范围

vsync-len(VPW):帧信号电子枪回扫时间 即垂直同步时间 Vsync

hactive(HVD):有效像素信号纵向分辨率

vactive(VVD):有效像素信号横向分辨率

如下LCD时序图参考文档:https://blog.csdn.net/lonely_fireworks/article/details/129362860 LCD时序

1,计算clock-frequency方法:

htotal: (一行数据)hsync水平同步信号需要的总的像素时钟周期个数

vtotal: (一列数据)vsync垂直同步s信号需要的总的像素时钟周期个数

hsync-len: hsync水平同步信号的低电平(非有效电平)持续的时间,即需要的像素时钟周期个数

clock-frequency: panel clock in Hz

htotal = (hback-porch + hactive + hfront-porch + hsync-len)

vtotal = (vback-porch + vactive + vfront-porch + vsync-len)

clock-frequency = htotal * vtotal * 刷新率

2,计算rockchip,lane-rate方法:

rockchip,lane-rate = htotal * vtotal * 刷新率 * 3(RGB) * 8(bit位) / dsi,lanes(lane数)/ 0.9

或者:

rockchip,lane-rate = htotal * vtotal * 刷新率 * 3(RGB) * 8(bit位) * 10 / dsi,lanes(lane数)/ 9

3(RGB):是每一个 pixel 有 RGB 3 个分量;

0.9:是考虑 mipi 时序的传输效率;

例子:

clock-frequency = <57153600>; // 计算:默认andoid手机屏幕fps = 60, (5 + 5 + 720 + 5) * (2 + 1 + 1280 + 13) * 60 = (735 * 1296) * 60 = 57153600

例子:

clock-frequency = <57153600>; // 计算:默认andoid手机屏幕fps = 60, (5 + 5 + 720 + 5) * (2 + 1 + 1280 + 13) * 60 = (735 * 1296) * 60 = 57153600

examples:- |dsi {#address-cells = <1>;#size-cells = <0>;panel@0 {compatible = "samsung,s6e8aa0";reg = <0>;vdd3-supply = <&vcclcd_reg>;vci-supply = <&vlcd_reg>;reset-gpios = <&gpy4 5 0>;power-on-delay= <50>;reset-delay = <100>;init-delay = <100>;panel-width-mm = <58>;panel-height-mm = <103>;flip-horizontal;flip-vertical;display-timings {timing0: timing-0 {clock-frequency = <57153600>; // 默认andoid手机屏幕fps = 60, (5 + 5 + 720 + 5) * (2 + 1 + 1280 + 13) * 60 = (735 * 1296) * 60 = 57153600hactive = <720>;vactive = <1280>;hfront-porch = <5>;hback-porch = <5>;hsync-len = <5>;vfront-porch = <13>;vback-porch = <1>;vsync-len = <2>;};};};};

如下内容参考文档:https://blog.csdn.net/LinuxArmbiggod/article/details/83277035 LCD点屏杂记

关于像素时钟和lane传输速率的计算

像素时钟:clock-frequency 即DCLK(dot clock), PCLK(pixel clock).

clock-frequency = (h_active + hfp + hbp + h_sync) * (v_active + vfp + vbp + v_sync) * fps

clock-frequency = 水平信号总周期垂直信号总周期帧率

fps为帧率,一般为60,表示每秒刷新60帧图像

lane传输速率:表示一条数据 lane 的传输速率,单位为 Mbits/s

lane_clk = 100 + H_total×V_total × fps × 3 × 8 / lanes_nums

total 这里指的是 水平 垂直信号总周期

fps 为帧率 取60

3 × 8 代表一个 RGB 为 3 个字节,每个字节 8 bit

lanes 代表 data 通道数

如:

rockchip,lane-rate = 100 + H_total×V_total × fps × 3 × 8 / lanes_nums / 0.9

0.9:是考虑mipi时序的传输效率

如下内容参考文档:http://www.nnewn.com/page226?article_id=281 Rockchip_Developer_Guide_DRM_Display_Driver_CN.pdf

带宽的计算方法

1)图像的带宽

以1080P ARGB格式的图像数据为例:

ARGB格式一个像素占用的内存大小:4 Byte

1080P ARGB格式的数据占用内存:1920 x 1080 x 4Byte/pixel = 8,100 Kbyte

如果按 60fps 刷新,占用的带宽是: 8,100 x 60fps = 474.6 Mbyte/s

2)显示接口的带宽

Bandwidth

MIPI DSI 驱动中会自动按如下公式根据不同的工作模式进行带宽的计算,当然在调试过程中也许对计算

的结果想做些微调可以通过 DTS dsi 节点下 rockchip,lane-rate 属性进行指定,单位可以是

Kbps/Mbps(D-PHY) 或 Ksps/Msps (C-PHY)

display-timings {native-mode = <&dsi0_timing0>;dsi0_timing0: timing0 {clock-frequency = <132000000>;hactive = <1920>;vactive = <1080>;hback-porch = <30>;hfront-porch = <15>;hsync-len = <2>;vback-porch = <15>;vfront-porch = <15>;vsync-len = <2>;hsync-active = <0>;vsync-active = <0>;de-active = <0>;pixelclk-active = <0>;};

hsync-active 行同步信号有效电平,0表示低电平有效,1表示高电平有效

vsync-active 帧同步信号有效电平,0表示低电平有效,1表示高电平有效

pixelclk-active:数据采样的方式

配置为1:上升沿驱动像素数据/下降沿采样数据

配置为0:下降沿驱动像素数据/上升沿采样数据

如panel-timing.yaml说明:

hsync-active:

description: |

Horizontal sync pulse.

0 selects active low, 1 selects active high.

If omitted then it is not used by the hardware

de-active:

description: |

Data enable.

0 selects active low, 1 selects active high.

If omitted then it is not used by the hardware

以上面设备树配置的时序为例,当前这个时序下,按 60 帧刷新需要的 dclk 是:131994240 hz,dts 实际按取整 132000000 hz 配

置:

htotal = hfp + hsync + hbp + hactive = 15 + 2 + 30 + 1080 = 1,127

vtotal = vfp + vsync + vbp + vactive = 15 + 2 + 15 + 1920 = 1,952

dclk = htotal x vtotal x fps = 1127 x 1952 x 60fps = 131,994,240

MIPI 接口上传输的频率是:

rockchip,lane-rate = 132M x 3(RGB) x 8(bpc) / 4(lane) / 0.9 = 880 Mbps

其中:

x3(RGB):是每一个 pixel 有 RGB 3 个分量;

x8(bpc):是每一个分量的位深是 8bit;

/4(lane):是这么多数据量在 4 lane 上传输,/4 是计算每 lane 的数据量;

/0.9:是考虑 mipi 时序的传输效率;

如下内容参考文档:https://blog.csdn.net/qq_37858386/article/details/123705548

2022-03-24 RK3566 MIPI屏 调试记录,panel-init-sequence 命令格式介绍

dts配置:

&dsi1 {status = "okay";rockchip,lane-rate = <xxxx>;panel@0 {compatible = "simple-panel-dsi";reg = <0>;backlight = <&backlight>;//power-supply=<&vcc_3v3>;enable-gpios = <&gpio0 RK_PC7 GPIO_ACTIVE_HIGH>;reset-gpios = <&gpio0 RK_PC5 GPIO_ACTIVE_LOW>;pinctrl-names = "default";pinctrl-0 = <&lcd_enable_gpio>, <&lcd_rst_gpio>;prepare-delay-ms = <120>;reset-delay-ms = <120>;init-delay-ms = <120>;stbyb-delay-ms = <120>;enable-delay-ms = <120>;disable-delay-ms = <120>;unprepare-delay-ms = <120>;width-mm = <229>;height-mm = <143>;dsi,flags = <(MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST |MIPI_DSI_MODE_LPM | MIPI_DSI_MODE_EOT_PACKET)>;dsi,format = <MIPI_DSI_FMT_RGB888>;dsi,lanes = <8>;panel-init-sequence = [39 00 06 FF 77 01 00 00 1039 00 03 C0 E9 0339 00 03 C1 08 0239 00 03 C2 31 0815 00 02 CC 1039 00 11 B0 00 0B 10 0D 11 06 01 08 08 1D 04 10 10 27 30 1939 00 11 B1 00 0B 14 0C 11 05 03 08 08 20 04 13 10 28 30 1939 00 06 FF 77 01 00 00 1115 00 02 B0 3515 00 02 B1 3815 00 02 B2 0215 00 02 B3 8015 00 02 B5 4E15 00 02 B7 8515 00 02 B8 2015 00 02 B9 1015 00 02 C1 7815 00 02 C2 7815 64 02 D0 8839 00 04 E0 00 00 0239 00 0C E1 05 00 00 00 04 00 00 00 00 20 2039 00 0E E2 00 00 00 00 00 00 00 00 00 00 00 00 0039 00 05 E3 00 00 33 0039 00 03 E4 22 0039 00 11 E5 07 34 A0 A0 05 34 A0 A0 00 00 00 00 00 00 00 0039 00 05 E6 00 00 33 0039 00 03 E7 22 0039 00 11 E8 06 34 A0 A0 04 34 A0 A0 00 00 00 00 00 00 00 0039 00 08 EB 02 00 10 10 00 00 0039 00 03 EC 02 0039 00 11 ED AA 54 0B BF FF FF FF FF FF FF FF FF FB B0 45 AA39 00 06 FF 77 01 00 00 0015 00 02 36 0005 78 01 1105 14 01 29];panel-exit-sequence = [05 00 01 2805 00 01 10];display-timings {native-mode = <&timing0>;timing0: timing0 {clock-frequency = <27000000>;hactive = <480>;vactive = <854>;hfront-porch = <150>;hsync-len = <10>;hback-porch = <10>;vfront-porch = <14>;vsync-len = <4>;vback-porch = <6>;hsync-active = <1>;vsync-active = <1>;de-active = <0>;pixelclk-active = <1>;};};ports {#address-cells = <1>;#size-cells = <0>;port@0 {reg = <0>;panel_in_dsi: endpoint {remote-endpoint = <&dsi_out_panel>;};};};};ports {#address-cells = <1>;#size-cells = <0>;port@1 {reg = <1>;dsi_out_panel: endpoint {remote-endpoint = <&panel_in_dsi>;};};};};&dsi1_in_vp0 {status = "disabled";

};&dsi1_in_vp1 {status = "okay";

};

port配置参考文档:linux设备树:phandle和port

这篇关于linux drm mipi dsi lcd 点屏之设备树配置的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!