本文主要是介绍曼彻斯特解码,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

曼彻斯特解码 verilog

`timescale 1ns / 1ps

//

module decode

(input dou_sys_clk,input sys_rst_n,input sys_clk,input data_man,output wire data_out

); reg start_flag ; // 开始解码标志

reg decode_flag ; // 正常解码标志,一次刚好取到一个码

reg [1:0]data_fifo ; // 暂存2位曼彻斯特码用以解码

reg error ; // 曼彻斯特码不符合正确信息报1

reg data_out_reg;always @(posedge dou_sys_clk ) begindata_fifo <= {data_fifo[0],data_man};if(data_fifo == 2'b00 || data_fifo == 2'b11)beginstart_flag <= 1'b1;end

endalways @(posedge dou_sys_clk) beginif(!sys_rst_n) beginstart_flag <= 1'b0;decode_flag <= 1'b0;error <= 1'b0;endelse beginif(start_flag == 1'b1)decode_flag <= !decode_flag;end

endalways @(posedge decode_flag) beginif(!sys_rst_n) beginstart_flag <= 1'b0;decode_flag <= 1'b0;error <= 1'b0;endelse beginif ( data_fifo == 2'b01) begindata_out_reg <= 1'b0;error <= 1'b0;endelse if( data_fifo == 2'b10) begindata_out_reg <= 1'b1;error <= 1'b0;endelse if(data_fifo == 2'b11 || data_fifo == 2'b00) beginerror <= 1'b1;endelse begindata_out_reg <= data_out_reg;endend

endassign data_out = data_out_reg;endmodule[tb]

`timescale 1ns / 1ps

//

module tb_decode();

reg dou_sys_clk;

reg sys_rst_n;

reg data_man;

wire data_out;

reg [4:0] count;

reg sys_clk = 0;

reg [31:0] data ;

initial begindou_sys_clk = 0;sys_rst_n = 0;

#12 sys_rst_n = 1;end

always@(*)beginif(!sys_rst_n)data <= 32'b0;elsedata <= 32'b10011001011001100101100110010101;

endalways @(posedge dou_sys_clk or negedge sys_rst_n) beginif (!sys_rst_n) begincount <= 31;data_man <= 0; end else beginif(count == 0) count <= 31;else data_man <= data[count];count <= count - 1; end

endalways #5 dou_sys_clk = !dou_sys_clk;

always #10 sys_clk = !sys_clk;decode u_decode(.dou_sys_clk(dou_sys_clk),.sys_clk(sys_clk),.sys_rst_n(sys_rst_n),.data_man(data_man),.data_out(data_out)

);

endmodule

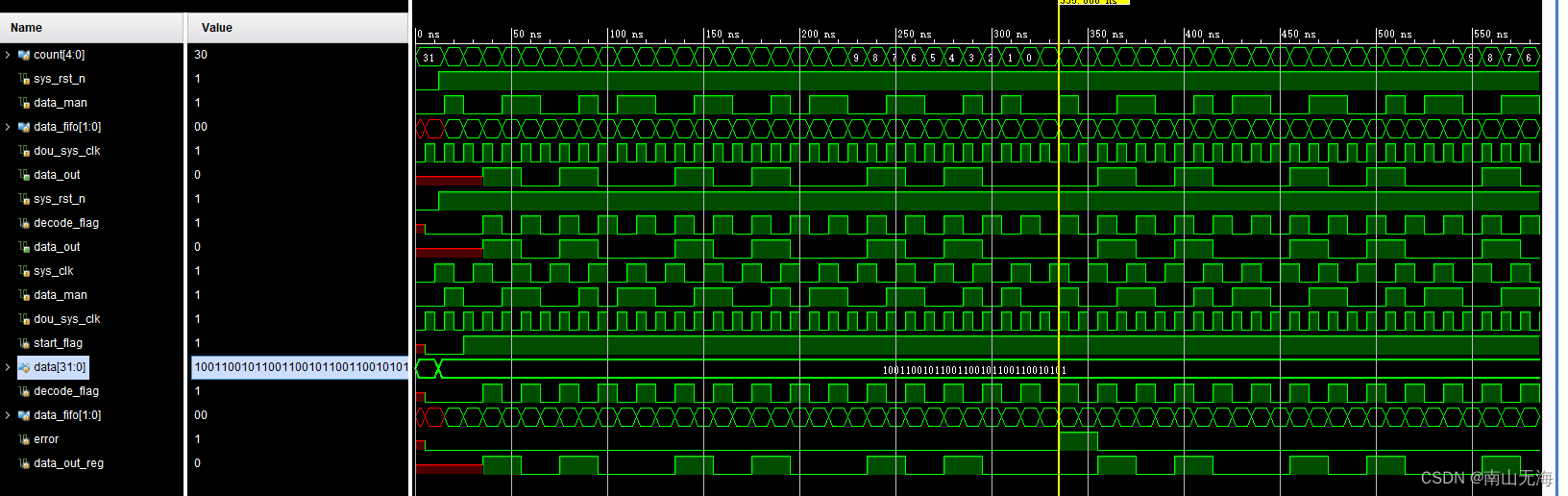

[运行结果]

这篇关于曼彻斯特解码的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!