本文主要是介绍基于FPGA的数字电路实验(一):实验准备及示例项目,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

最近在做数字电路的实验,写点文章记录下过程:

我们的教学开发板是Nexys3,淘宝上要1000多。。基于FPGA,开发语言是VerilogHDL,开发平台是ISE Design Suite,调试工具使用的是Digilent Adept。

FPGA

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。 —— [ 百度百科 ]

Nexys3

Nexys 开发板是基于最新技术Spartan-6 FPGA的数字系统开发平台。它拥有48M字节的外部存储器(包括2个非易失性的相变存储器),以及丰富的I/O器件和接口,可以适用于各式各样的数字系统。 板上自带AdeptTM高速USB2接口可以为开发板提供电源,也可以烧录程序到FPGA,用户数据的传输速率可以达到38M字节/秒。

Nexys3开发板可以通过添加一些低成本的外设Pmods (可以多达30几个)和Vmods (最新型外设)来实现额外的功能,例如A/D和D/A转换器,线路板,电机驱动装置,和实现装置等等。另外,Nexys3完全兼容所有的赛灵思工具,包括免费的WebPackTM,ChipscopeTM,EDKTM(嵌入式处理器设计套件),以及其他工具。 —— [ 百度百科 ]

Verilog HDL

Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 Verilog HDL和VHDL是世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。前者由Gateway Design Automation公司(该公司于1989年被Cadence公司收购)开发。两种HDL均为IEEE标准。 —— [ 百度百科 ]

ISE Design Suite

Xilinx ISE Design Suite是利用新技术来降低总设计成本的电子设计套件软件,并且实现了比任何其它 PLD 解决方案更高的性能。借助 Xilinx ISE Design Suite 的突破性技术提高系统级设计效率并加快产品投产。 ISE Design Suite 采用各种方法来实现团队设计、功耗优化以及简化 IP 集成,从而分发挥 Xilinx 目标设计平台在配置逻辑、嵌入式和 DSP 设计方面的潜力。 所有这一切均可通过紧密集成的设计流程来实现。

ISE Design Suite: Logic Edition —— [ 百度百科 ]

软件下载安装就不说了,记得给ISE添加证书。之后开始第一个示例项目

创建项目

输入项目名称,Next

Project Settings里记得在Family里选择Spartan6,然后在Device里选择XC6SLX16,Package里选择CSG324,Next

新建工程的信息,Finish

至此,项目创建完毕,然后是编写代码

工程管理区任意位置单击鼠标右键,选择New Source

选择Verilog Module,输入文件名,Next

Define Module是端口定义对话框,可以直接在这里定义输入输出信号,信号最高位最低位,可以跳过在之后的源程序中添加,Next

Finish

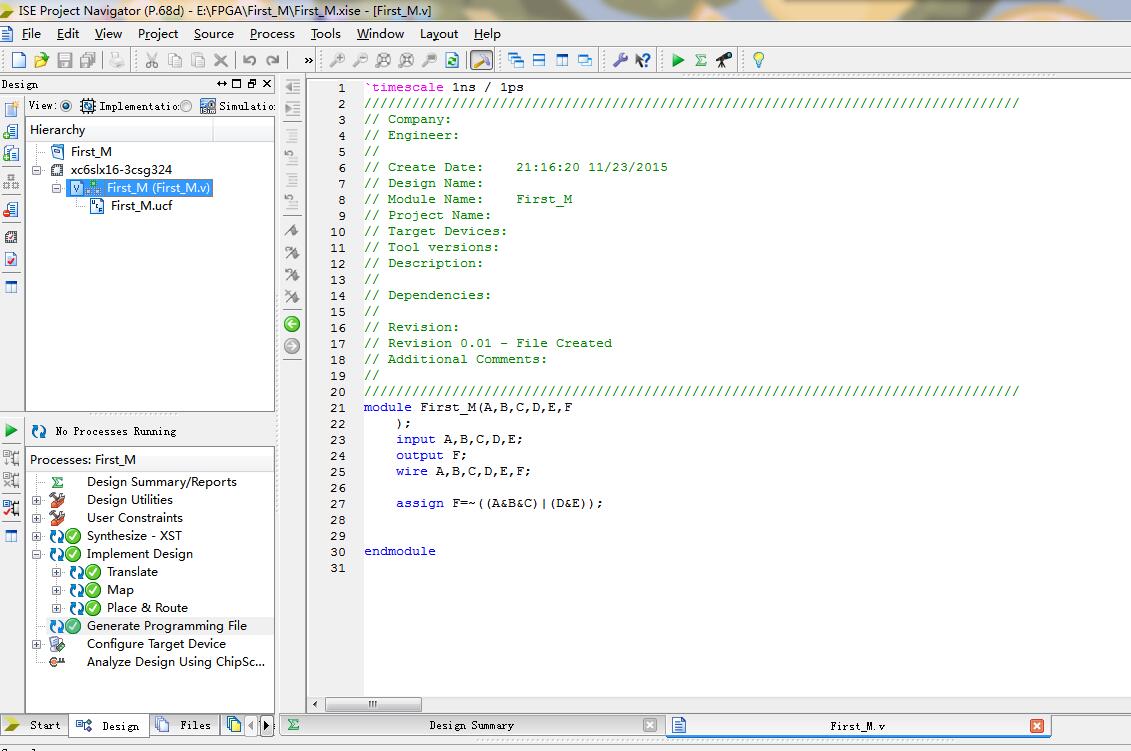

输入代码

module First_M(A,B,C,D,E,F

);

input A,B,C,D,E;

output F;

wire A,B,C,D,E,F;

assign F=~((A&B&C)|(D&E));

endmodule语法检查,双击Check Syntax,变为绿色的勾即为正确

在工程管理去将View设置为Simulation,右键,选择Verilog Test Fixture编写测试文件,Next

Next

ISE自动生成基本的信号并对被测模块做了例化,在//Add stimulus here 后添加测试代码。

A = 1;

B = 0;

C = 1;

D = 0;

E = 1;双击Behavioral Check Syntax检查语法

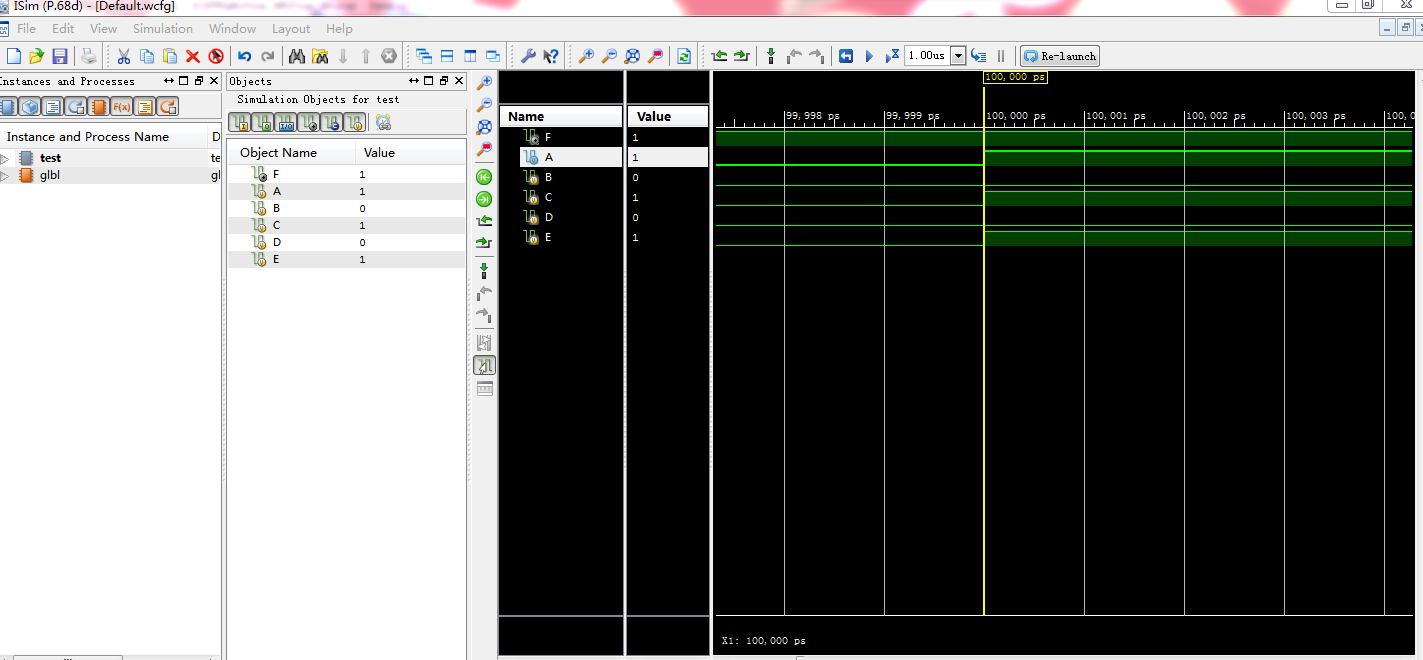

双击Simulate Behavior Model启动行为级仿真

可以看到在100ns的时候,A,C,E的波形从0变为1将View切换为Implementation,双击Synthesize-XST,看逻辑综合是否有错,如没有语法错误,XST能够给出初步的资源消耗情况,点击Design Summary即可查看

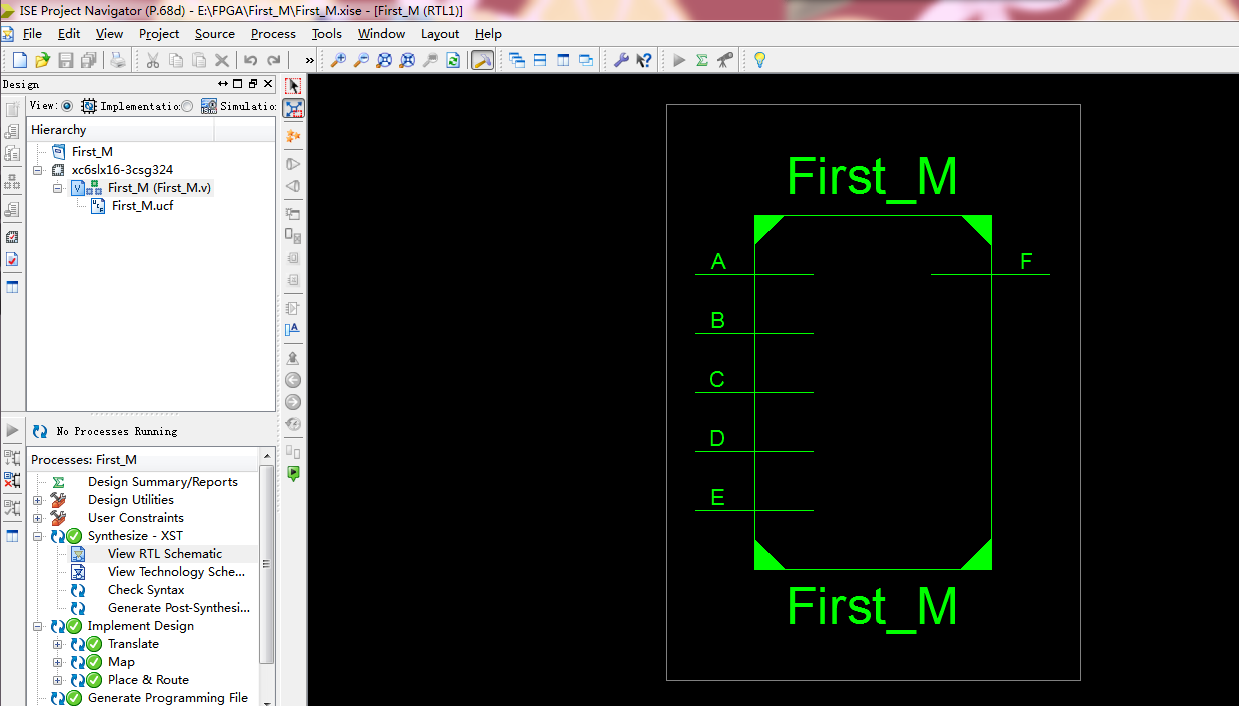

双击Synthesize-XST下的View RTL Schematic,打开设计综合后的寄存器传输级(RTL)视图。弹出的对话框中选择Start with a schematic of the top-level block,点击OK

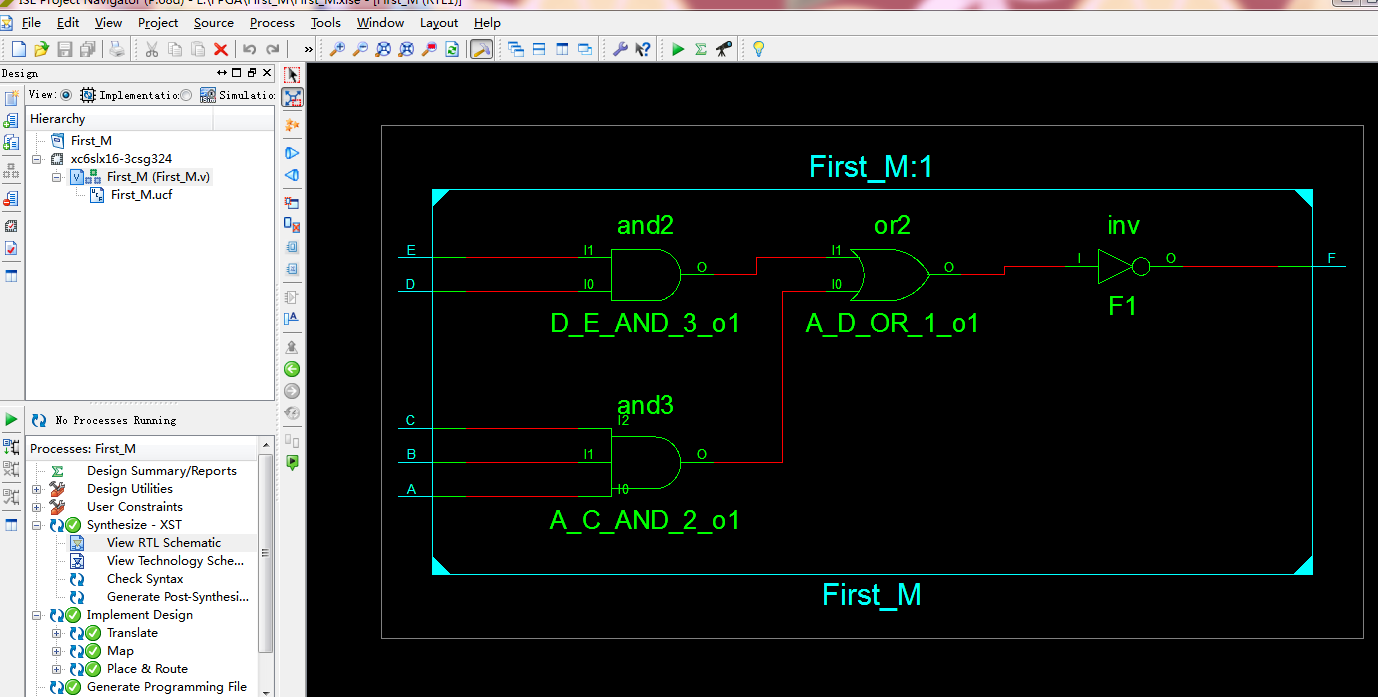

双击顶层模块可进入与之相应的模块内部RTL视图

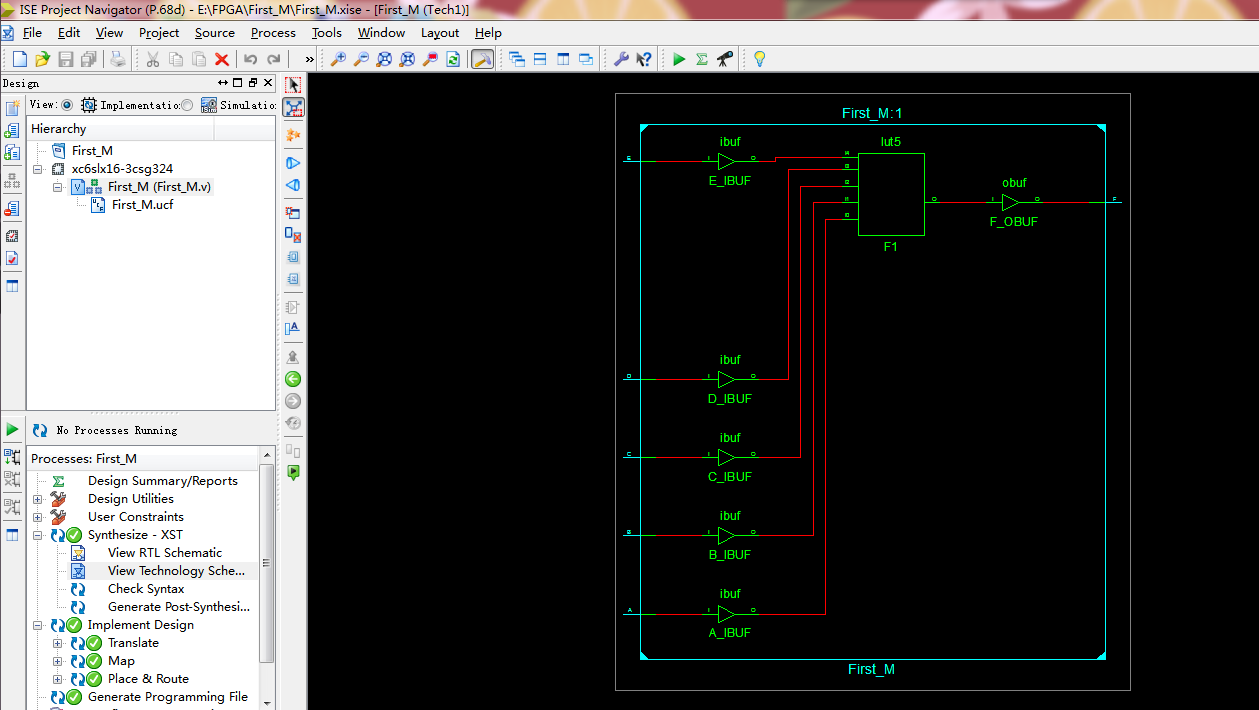

双击View Technology Schematic,可查看工艺级视图

配置管脚,可直接右键新建Implementation Constraints File生成约束文件,也可点击Tools下的PlanAhead,在I/O Prots中分配引脚。

双击Implementation Design进行逻辑综合与实现

双击Generate Programming File生成二进制比特文件

打开Adept软件,将Nexys3通过USB连接电脑,软件会自动识别,点击Browse,找到工程文件夹中的first_m.bit文件,点击Program,文件会下载到开发板上。下载过程中,Done灯处于熄灭状态,下载完成后会出现Programming Successful,Done灯会再次点亮,表明代码下载成功。

在板上验证结果。

这是一个比较完整的项目开发流程,实际使用中,可能并不需要测试仿真等步骤,这个自行选择即可。

未完待续~

这篇关于基于FPGA的数字电路实验(一):实验准备及示例项目的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!