本文主要是介绍双倍数据速率I/O (ALTDDIO_IN、ALTDDIO_OUT)使用方法,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- ALTDDIO特性

- 应用场景

- 端口定义

- 1、ALTDDIO_IN

- 2、ALTDDIO_OUT

- DDR I/O时序

- ip仿真测试

学习双倍数据速率 I/O,在I/O单元(IOE)中实现DDR寄存器。其中

ALTDDIO_IN IP内核实现DDR输入的接口(输入端口)。

ALTDDIO_OUT IP内核实现DDR输出的接口(输出端口)。

ALTDDIO_BIDIR IP内核实现双向DDR输入和输出的接口(双向端口)。

ALTDDIO特性

ALTDDIO_IN IP内核在参考时钟的上升和下降沿接收数据

ALTDDIO_OUT IP内核在参考时钟的上升和下降沿发送数据

ALTDDIO_BIDIR IP内核在参考时钟的上升和下降沿发送和接收数据

总之,数据被锁存在时钟的上升和下降沿

应用场景

DDR寄存器可连接DDR SDRAM、DDR2 SDRAM等存储器器件,也就是用作它们的存储接口,使得它们可以两倍速率读写数据。

在LVDS应用中,经常使用DDR数据来实现高速标准(将DDR I/O寄存器用作SERDES旁路机制)。

不管是DDR还是LVDS都是后续需要掌握的知识。

端口定义

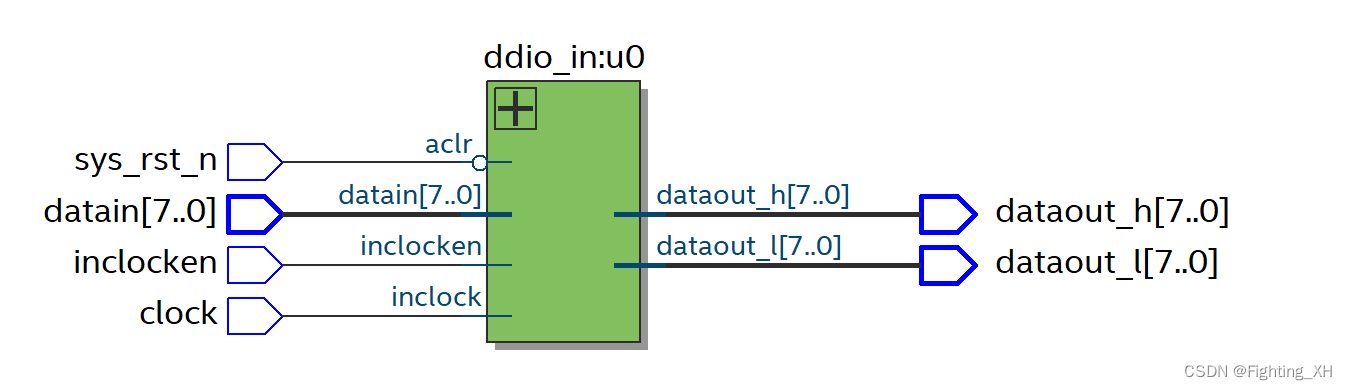

1、ALTDDIO_IN

datain:管脚到DDR电路的输入数据,可指定数据位宽

.

inclocken:时钟使能信号,高电平时输出以时钟上升沿采样,否则下降沿采样

.

inclock:时钟信号来采样DDR输入数据,inclocken使能有效时,数据的第一个比特在输入时钟的上升沿被采集。否则数据的第一个比特在输入时钟的下降沿被采集。

.

outclock信号寄存数据输出 时钟使能信号

.

aclr:异步清零输入;sclr:同步清零输入;aset:异步置数;sset:同步置数。(清零:计数满置0;置数:计数满输出设定值)

.

dataout_h:采集 在inclock信号上升沿的datain;否之,采集 在clock信号下降沿的datain

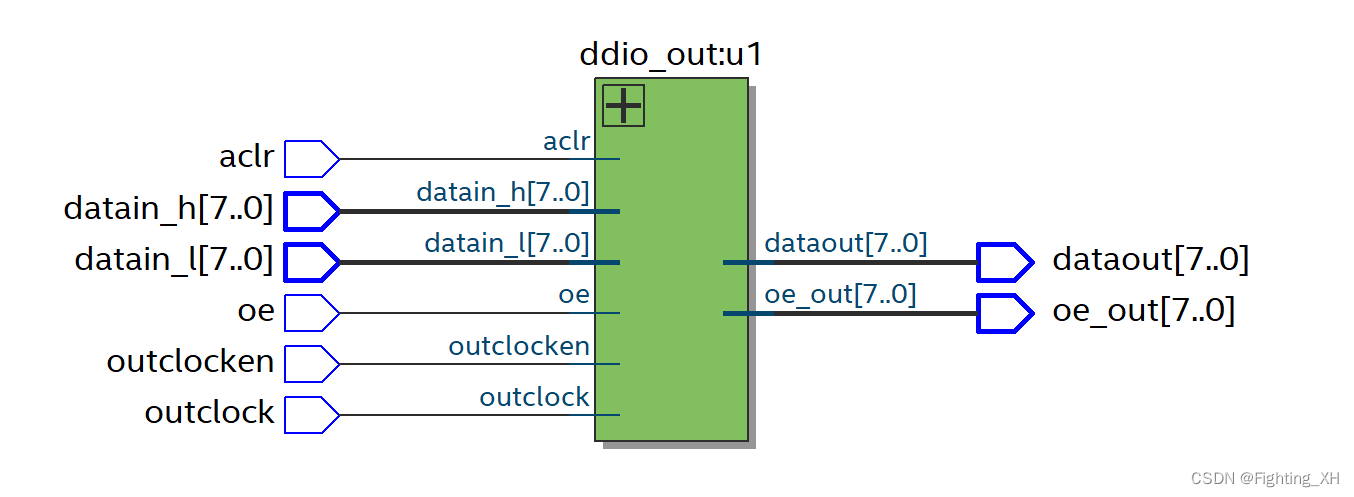

2、ALTDDIO_OUT

dataout_h:outclock上升沿的输入数据,dataout_l:outclock下降沿的输入数据

.

outclock:输出的时钟信号;outclocken:输出时钟使能信号,防止数据被传递。

.

dataout:DDR电路到管脚的输出数据端口。 该选项仅适用于Cyclone III和Cyclone II器件

.

oe:连接到三态输出缓冲区的使能信号,从而对数据被加载到 dataout端口进行控制。(高电平有效,若想低电平有效,取反即可)

.

oe_out:采用三态门的方式进行输出。双向输出端口。

.

DDR I/O时序

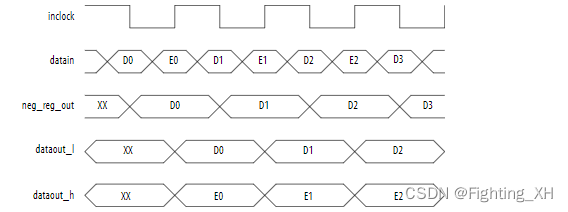

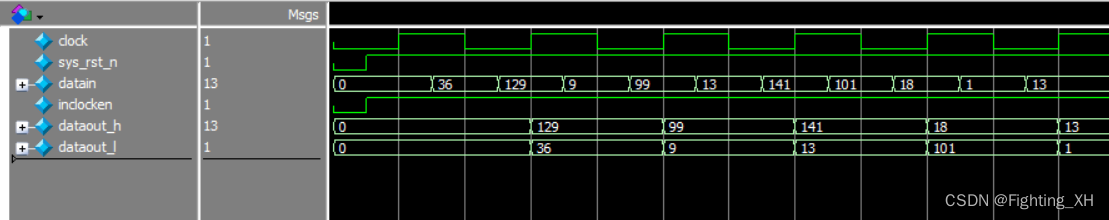

ALTDDIO_IN输入时序波形:

可看到neg_reg_out是对下降沿采集的数据进行寄存。

dataoutl:在时钟上升沿采样下降沿寄存的数据。

dataouth:在时钟上升沿采样data的数据。

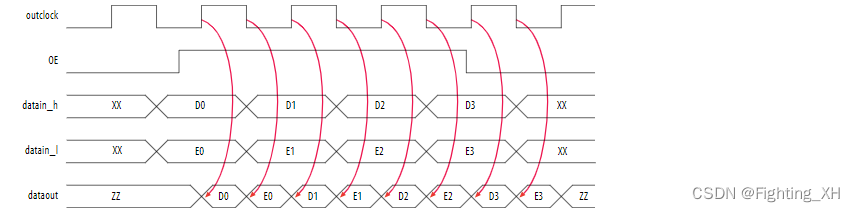

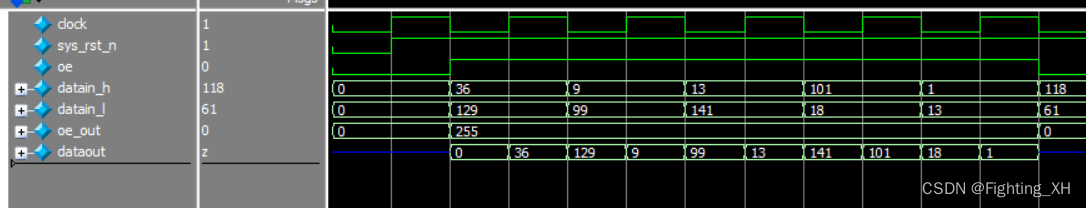

ALTDDIO_OUT输出时序波形:

Quartus II软件将oe信号作为高电平有效,因此下图给出的也是高电平有效的情况。

datain_h和datain_l是两路上升沿采样的数据,通过DDIO端口,我们输出一路数据。

dataout可看到,它是在outclock的上升沿和下降沿都进行数据的采样,从而获得了双倍速率数据。

ip仿真测试

ALTDDIO_IN顶层代码:

module ddr_io(

//ddio_in输入输出input sys_rst_n , //复位input clock,input [7:0] datain,input inclocken, //高有效output [7:0] dataout_h,output [7:0] dataout_l);ddio_in u0(.aclr(~sys_rst_n),.inclock(clock),.datain(datain),.inclocken(inclocken),.dataout_h(dataout_h),.dataout_l(dataout_l));endmoduletb测试代码:

`timescale 1ns/1ns //时间单位/精度//------------<模块及端口声明>----------------------------------------

module ddr_io_tb();reg clock ;

reg sys_rst_n;

reg [7:0] datain ;

reg inclocken;wire [7:0] dataout_h ;

wire [7:0] dataout_l ;//------------<例化被测试模块>----------------------------------------ddr_io inst_ddr_io(.sys_rst_n ( sys_rst_n) ,.clock ( clock ) ,.datain ( datain ) ,.inclocken(inclocken),.dataout_h ( dataout_h ) ,.dataout_l ( dataout_l )

);initial beginclock = 1'b0; //条件为0sys_rst_n <= 1'b0;inclocken <= 1'b0;datain <= 8'd0;#5 //35个时钟周期sys_rst_n <= 1'b1; //拉高复位inclocken <= 1'b1; #10datain = $random % 256; //产生8位的随机数#10datain = $random % 256; #10datain = $random % 256; #10datain = $random % 256; #10datain = $random % 256; #10datain = $random % 256; #10datain = $random % 256; #10datain = $random % 256; #10datain = $random % 256; #10datain = $random % 256; #20$stop;

endalways #10 clock = ~clock; //产生系统时钟,周期20nsendmodule

ALTDDIO_OUT顶层代码:

module ddr_io(//ddio_out输入输出input sys_rst_n , //复位input clock,input [7:0] datain_h,input [7:0] datain_l,input oe,input outclocken,output [7:0] oe_out,output [7:0] dataout);ddio_out u0(.aclr(~sys_rst_n),.outclock(clock),.datain_h(datain_h),.datain_l(datain_l),.oe(oe),.outclocken(outclocken),.oe_out(oe_out),.dataout(dataout));endmodule

`timescale 1ns/1ns //时间单位/精度//------------<模块及端口声明>----------------------------------------

module ddr_io_tb();reg clock ;

reg sys_rst_n ;

reg oe ;

reg [7:0] datain_h ;

reg [7:0] datain_l ;wire [7:0] oe_out;

wire [7:0] dataout ;

//------------<例化被测试模块>----------------------------------------ddr_io ddio_inst

(.clock (clock ),.sys_rst_n (sys_rst_n ),.oe (oe ),.datain_h (datain_h ), .datain_l (datain_l ),.oe_out(oe_out),.dataout (dataout )

);//------------<设置初始测试条件>----------------------------------------

initial beginclock = 1'b0; //初始条件为0sys_rst_n <= 1'b0; oe <= 1'b0; datain_h <= 8'd0;datain_l <= 8'd0;#10 sys_rst_n <= 1'b1;#10oe <= 1'b1; #100oe <= 1'b0; #20$stop;

endalways #10 clock = ~clock; //系统时钟,周期20nsalways #20 datain_h = $random % 256; //每20ns生成一个0~255的随机数

always #20 datain_l = $random % 256; //每20ns生成一个0~255的随机数 endmodule

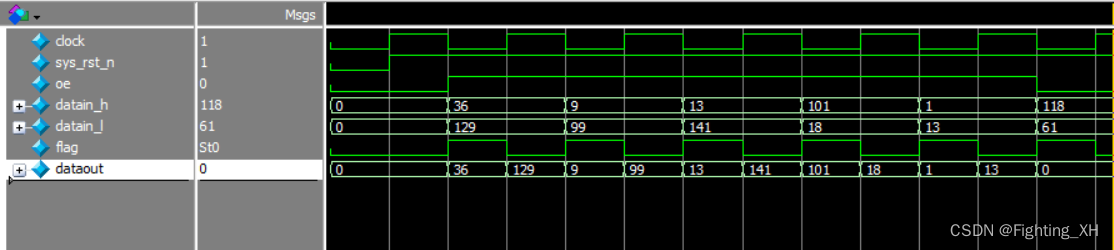

根据上面的原理,手写代码实现时钟上下沿采样数据,达到一个clk双倍数据速率传输

module ddr_io(//ddio_out输入输出input sys_rst_n, //复位input clock,input [7:0] datain_h,input [7:0] datain_l,input oe,output [7:0] dataout

);reg flag1;

reg flag2;

wire flag;//上升沿二分频

always @(posedge clock or negedge sys_rst_n) if (!sys_rst_n)flag1 <= 0;elseflag1 <= ~flag1;//下降沿二分频

always @(negedge clock or negedge sys_rst_n) if (!sys_rst_n)flag2 <= 0;else flag2 <= ~flag2;assign flag = flag1^flag2;assign dataout = oe ? (flag ? datain_h : datain_l) : 0;endmodule

`timescale 1ns/1ns //时间单位/精度//------------<模块及端口声明>----------------------------------------

module ddr_io_tb();reg clock ;

reg sys_rst_n ;

reg oe ;

reg [7:0] datain_h ;

reg [7:0] datain_l ;wire [7:0] dataout ;

//------------<例化被测试模块>----------------------------------------ddr_io ddio_inst

(.clock (clock ),.sys_rst_n (sys_rst_n ),.oe (oe ),.datain_h (datain_h ), .datain_l (datain_l ),.dataout (dataout )

);//------------<设置初始测试条件>----------------------------------------

initial beginclock = 1'b0; //初始条件为0sys_rst_n <= 1'b0; oe <= 1'b0; datain_h <= 8'd0;datain_l <= 8'd0;#10 sys_rst_n <= 1'b1;#10oe <= 1'b1; #100oe <= 1'b0; #20$stop;

endalways #10 clock = ~clock; //系统时钟,周期20nsalways #20 datain_h = $random % 256; //每20ns生成一个0~255的随机数

always #20 datain_l = $random % 256; //每20ns生成一个0~255的随机数 endmodule

这篇关于双倍数据速率I/O (ALTDDIO_IN、ALTDDIO_OUT)使用方法的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!