本文主要是介绍数字电子技术—逻辑门电路,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一、概述

对于传统的集成电路逻辑门大致可以分为两类:

双极型晶体管逻辑门(TTL)、绝缘栅场效应管逻辑门(CMOS)

二、分立元件逻辑门

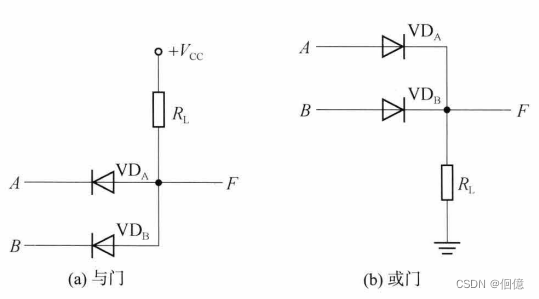

1、二极管与门、或门

分析:假设A、B输入的高电平为,低电平为0V

对与门而言,只要有一个输入是低电平就会有二极管导通,并且输出电压为0.7V,对应”0“状态

只有当两个输入都为高电平时,两个二极管均截至,输出为,对应"1"状态

对或门而言,只要有一个输入是高电平就会有二极管导通,并且输出电压为(-0.7)V,对应”1“状态,

只有当两个输入都为低电平时,两个二极管均截至,输出为0V,对应"0"状态

缺点:当输入电平确定后,与门输出的低电平将要上浮0.7V左右,或门的输出高电平将要下降0.7V左右,不利于实现多级的逻辑运算,而且缺乏驱动能力,输出端接入负载后会进一步影响输出的电压水平

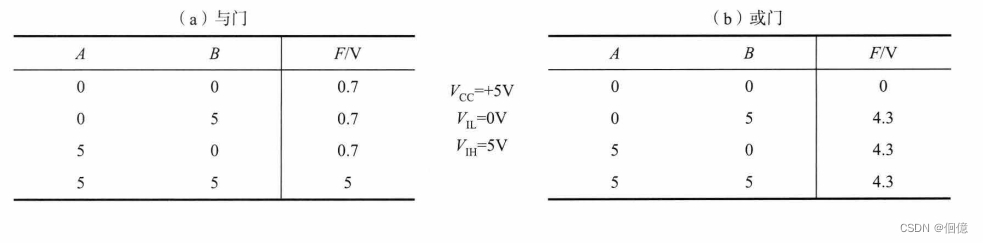

2、晶体管非门

分析:假设A输入的高电平为,低电平为0V

当A为高电平时,晶体管饱和导通,输出电压为0.3V,对应"0"状态

当A为低电平时,晶体管截至,输出电压为,对应"1"状态

三、CMOS集成逻辑门

CMOS是 Complementary Metal Oxide Semiconductor的缩写

C是互补的意思,在CMOS门中,N沟道和P沟道的管子一定是成对存在的,所以称之为CMOS

用的都是增强型的MOS管,沟道用虚线表示

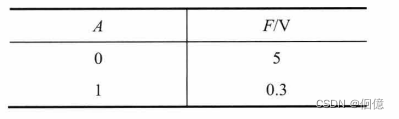

1 、CMOS非门

分析:假设A输入的高电平为,低电平为0V

当输入为高电平时,下面NMOS导通,上方PMOS关断,输出电压为0V,对应"0"状态

当输入为低电平时,下面NMOS关断,上方PMOS导通,输出电压为,对应"1"状态

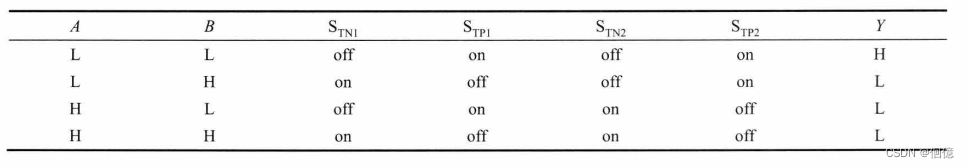

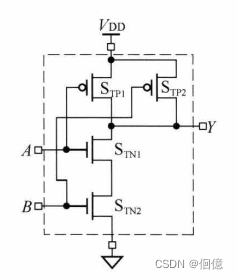

2、 CMOS或非门

分析:假设A输入的高电平为,低电平为0V

当A、B输入为高电平时,下面NMOS导通,上方PMOS关断,输出电压为0V,对应"0"状态

当有一个输入为高电平、一个输入为低电平时,总能保证上方的PMOS有一个处于关断状态,下方的NMOS有一个处于开通状态,此时输出电压为0V,对应"0"状态

当A、B输入为低电平时,下面NMOS都关断,上方PMOS都导通,输出电压为,对应"1"状态

分析可知只有输入同时为低电平时,才能输出高电平,电路形成或非关系

3、 CMOS与非门

分析:假设A输入的高电平为,低电平为0V

当A、B都为高电平时,下面NMOS全部导通,上方PMOS全部关断,输出电压为0V,对应"0"状态

只要有一个输入为低电平时,总能使上方的PMOS有一个处于开通状态,下方的NMOS有一个处于关断状态,此时输出电压为,对应"1"状态

分析可知只有输入同时为高电平时,才能输出低电平,电路形成与非关系

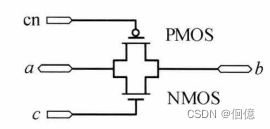

4、 CMOS传输门(TG)

分析:将PMOS和NMOS的源极和漏极极分别都连接在一起,只将栅极引出做控制,cn为PMOS 的栅极,c为NMOS 的栅极

当cn=0或者c=1时,均有MOS管导通【任意一个满足即可,二者都满足也符合】

四、TTL集成逻辑门

用三极管构成

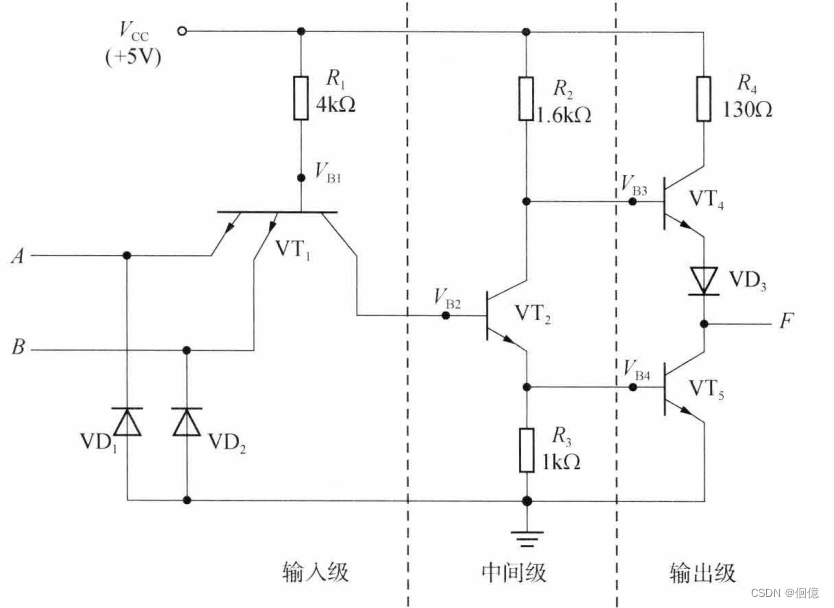

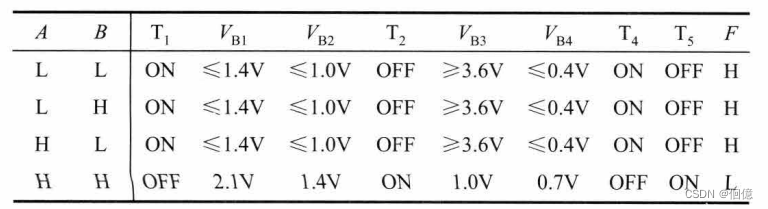

1、TTL与非门

分析:假设输入端的电压大于2V为高电平H,小于0.8V为低电平L

当A、B中有一个为低电平时,T1的发射结导通,将VB1电压钳位,此时VB1的电压无法维持T2和T5两管的导通【至少要大于1.4V才能维持】,所以T2和T5截止,此时T4管导通,F输出为高电平,对应“1”状态

当A、B都为高电平时,VB1的电压将会被钳位在2.1V,此时T1管倒置工作,T2和T5饱和导通,F输出为低电平,对应“0”状态

【注】1.输入用的是多发射极的三极管,多发射级三极管输入端是与的关系

2.电路导通时要么上拉到电源、要么下拉到地。输出端采用推拉式结构,可以提高TTL与非门的带负载能力。

3.输出电阻小,带负载能力强。

2、集电极开路门(OC门)、漏极开路门(OD门)

特点:门电路内部输出晶体管的集电极开路

OC门是TTL,OD门是CMOS,工艺不同原理相同,一个是晶体管集电极开路,一个是MOS管漏极开路

0C门的实现条件:内部集电极开路,外部必须上拉电阻使用

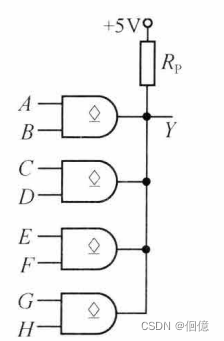

OC门的应用:

1.实现线与

OC/OD门可以实现线与的功能,输出端可以并接。普通的门电路不可以直接进行线与,假如一个输出1一个输出0,会直接短路接地造成大电流,损坏电路

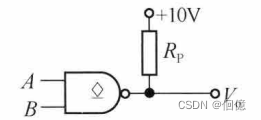

2.实现电平转换

可以根据输出端外部上拉的电源电压不同,输出不用于门电路供电电源的电压

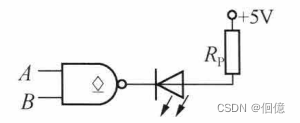

3.做驱动器

用来驱动大电流的应用场景

OC门涉及的计算问题:上拉电阻RL的计算

1.求RLMAX

m:高电平 看负载门的输入端子数

n:OC门的个数

![]()

2.求RLMin

m:低电平 看负载门的个数,和端子数无关,电流总要流进OC门

考虑OC门这里只有一个输出0,电流全部灌进这个OC门,

可以得到扛得住的最大电流,即得到最小电阻

![]()

3.RL的范围

![]()

3、三态门(TSL)

三种状态:0、1、高阻,相比于普通电路加了控制信号EN

输出端可以并接,但同一时刻只允许一个EN有效

应用场景:总线、可以一反一正,使能信号接在一起构成双向传输

核心:使能端的控制

五、集成逻辑门的性能参数

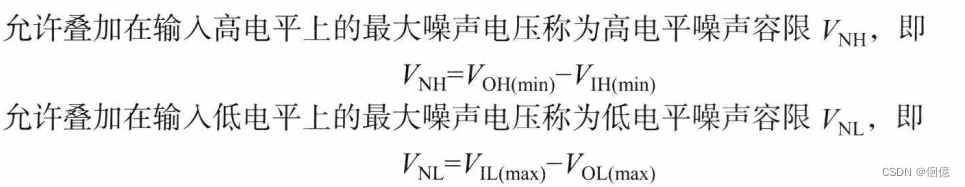

1、噪声容限:在工作过程中,输入端允许加入的干扰噪声大小

低电平噪声容限:正脉冲有影响

高电平噪声容限:负脉冲有影响

噪声容限越大,抗干扰能力越强

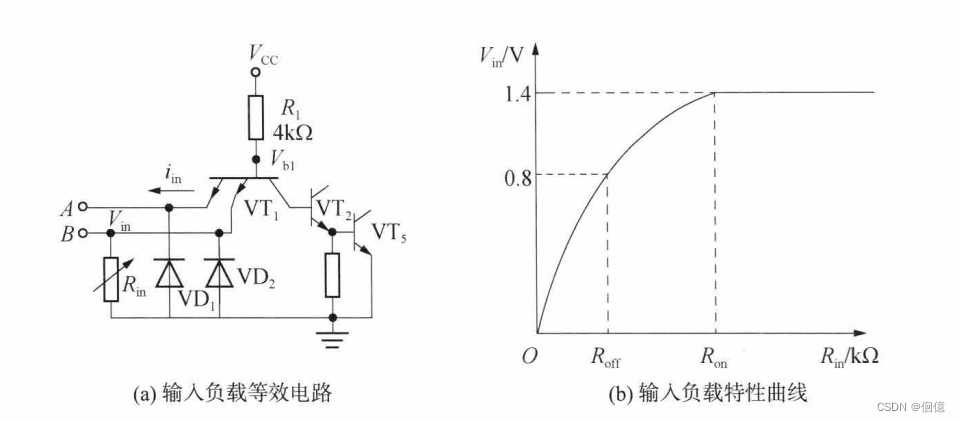

2、输入端负载特性

在电路的实际使用过程中,通常会在输入端和地之间加一个输入电阻,输入负载特性就是输入电压与输入电阻之间的关系

【理解】其中一个输入的电压相当于电阻串联分到的电压,利用开门电压和关门电压可以计算输入电阻的范围

根据分压公式极端的看,当输入电阻无穷大时相当于输入高电平,当输入电阻无穷小时相当于输入低电平

【注】CMOS输入端没有电流,输入电阻大小无所谓,无论多大电阻都不会改变输入本来的状态

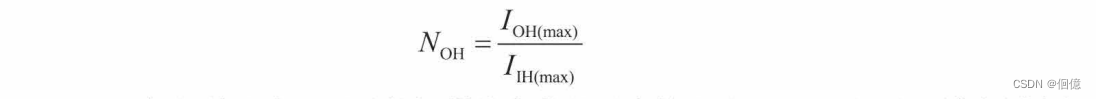

3、扇入与扇出系数

扇入系数 :一个逻辑门电路所能允许的输入端数目的个数

扇入系数 :一个逻辑门电路所能驱动同类门电路的最大个数,扇出系数越大,表示门电路带负载能力越强

扇入与扇出系数反映了门电路的输入端数目和输出驱动能力的指标,一般来说CMOS门电路带负载能力更强一点

当输出达到IOH时是能带载的最大能力,由此计算扇出系数

当输出电流大于IOH,输出的高电平得不到保证

输出0时,带的负载门电流是往里流【灌电流】会抬高输出电压

输出1时,带的负载门电流是往外流【拉电流】会拉低输出电压

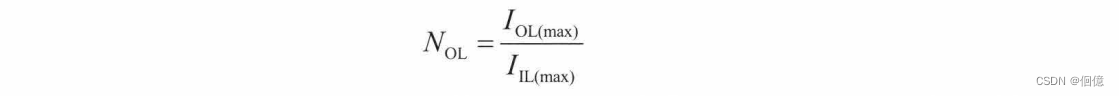

逻辑门输出高电平时的扇出系数为:

逻辑门输出低电平时的扇出系数为:

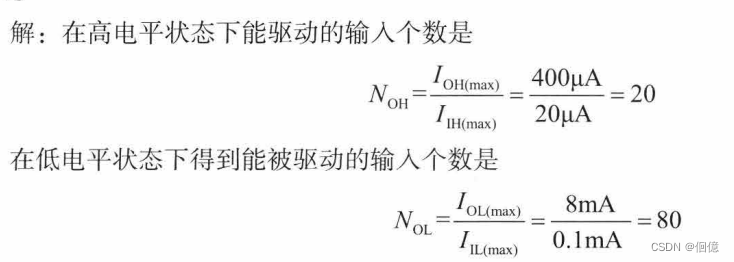

例:已知某门电路的电流参数为OL(max) = 8mA,

IL(max) = 0.1mA,

OH(MAX) = 0.4mA,

IH(max) =20uA,求可以带多少个同类门电路的输出

【注】在实际应用过程中如果高电平扇出系数和低电平系数不同,应采用较小的那个

3、平均传输延迟时间

由于晶体管的导通和截至都需要一定的时间,因此当集成逻辑门电路的输入信号发生变化时,输出信号的变化并不是立刻的,中间存在一定的延迟时间

平均传输延迟时间用pd表示,是衡量门电路工作速度的重要指标,

pd越小,逻辑门电路的工作速度就越快

4、集成逻辑门器件的功耗

集成逻辑门器件的功耗是指在正常工作所消耗的功率,用D表示

CMOS集成逻辑门的功耗相较于TTL逻辑门的功耗要低

以上为本人学习数字电子技术所做笔记,若有不妥之处,恳请各位指正

这篇关于数字电子技术—逻辑门电路的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!