本文主要是介绍Vivado XADC IP核 使用详解,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

本文介绍Vivado中XADC Wizard V3.3的使用方法。

XADC简介

XADC Wizard

Basic

- Interface Options:

一共三种,分别是AXI4Lite、DRP、None。勾选后可在界面左侧看到相应通信接口情况。 - Startup Channel Selection

Simultaneous Selection:同时监控两个外部通道。

Independent ADC:XADC独立地监视外部通道,同时监视FPGA内部的电压和温度。

Single Channel:只能选择一个通道进行监控。

Channel Sequencer:可以选择任意数量的通道进行监控。 - AXI4-Stream Options

Enable AXI4-Stream:勾选后使能AXI4 Stream接口。

FIFO Depth:设置FIFO深度,范围为7-1,020。 - Timing Mode

Continuous Mode(连续采样模式):XADc持续采样和转换所选通道。

Event Mode(单次触发采样模式):通过外部触发事件CONVST或CONVSTCLK信号来启动所选通道上的转换。该模式只能用于外部通道。 - DRP Timing Options

在DRP接口下,必须有DCLK时钟,DCLK时钟频率最高250 MHz。

ADC转换速率最大为1 Msps。在设定Acquisition Time(采集时间)后,可以得到Actual Conversion Rate(实际转换速率)。 - Analog Sim Options

设置模拟输入激励文件。 - Control/Status Ports

reset_in:允许外部输入复位信号。

convst_in:勾选该信号作为Even Mode的触发源。

convstclk_in:勾选该信号作为Even Mode的触发源。

Temp Bus:勾选后启用一个特殊的总线,它在每一个给定的时间间隔更新温度。

JTAG Arbiter:允许显示JTAG状态端口(JTAGMODIFIED、JTAGLOCED、JTAGBUSY)。

ADC Setup

ADC Setup

Sequencer Mode:如果XADC配置为Channel Sequencer、 Simultaneous Sampling 或Independent ADC模式,则此处可选Continuous, One-pass or Default mode。

Channel Averaging:通道数据平均个数,可选None、16、64和256。 - ADC Calibration

勾选以启动不同功能的校准。 - Supply Sensor Calibration

勾选以启动不同功能的校准。 - External Multiplexer Setup

外部多路复用器设置。如果选中,则有必要指定多路复用器(MUX)连接的外部通道。即是将内部的通道作为外部模拟输入通道来使用。

勾选Enable muxaddr_out port选项用于使用动态重新配置使能Channel for MUX。 - Power Down Options

控制ADCB或ADCA可以在不使用时关闭电源。只有ADCB已经关闭时,ADCA才能关闭。

Alarm

勾选不同复选框以启用对应的告警。 - Over Temperature,User Temperature Alarm

分别设置触发和复位阈值。 - VCCINT,VCCAUX,VBRAM Alarm

分别设置上、下告警值, 如果测量值超出这些限制,则报警逻辑输出变为活动。 - VCCPAUX ,VCCDDRO Alarm(只适应于Zynq-7000系列FPGA芯片)

Channel Sequencer

如果XADC配置为Channel Sequencer、 Simultaneous Sampling 或Independent ADC模式,通道序列器才启用。选择不同的通道进行监控,启用所选通道的平均,启用外部通道的双极模式,并增加所选通道的采集时间。

XADC配置为Single Channel模式时,则只能设置一个通道的参数。

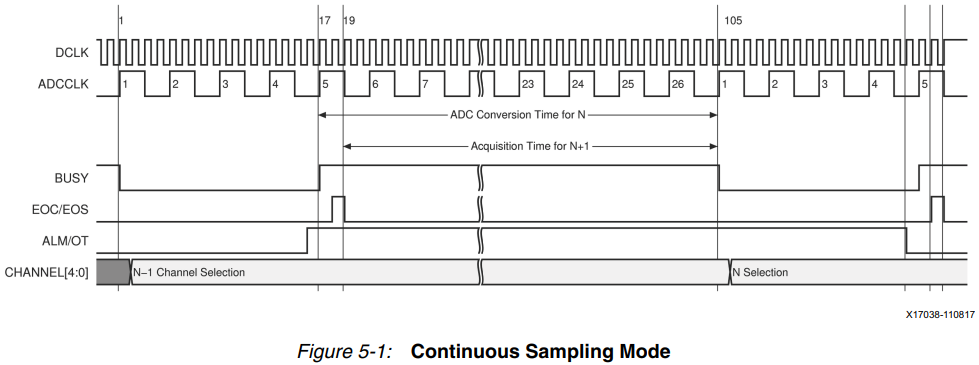

连续采样

连续采样模式下,仿真时序图如下。图中有几个通道,取决于IP核中所勾选的ADC通道。

单次触发采样

需要注意的是,CONVST/CONVSTCLK只启动一次转换。当使用自动通道定序器或平均时,转换的次数是序列中的通道数和被平均的样本数的乘积。

DRP时序

DRP读写操作如上图所示,当DEN为逻辑高电平时,DRP地址(DADDR)和写使能(DWN)在DCLK的下一个上升沿有效。DEN应该只在一个DCLK周期内为逻辑高电平。

如果DWE为逻辑低电平时,则执行DRP读操作,当DRDY由低变高时,所读数据在DO[15:0]总线上有效。

如果DWE为逻辑高电平时,DI[15:0]和DADDR[6:0]将在 DCLK的下一个上升沿被捕获。当数据被成功写入DRP寄存器时,DRDY信号变为逻辑高电平。在DRDY信号变低之前,不能发起新的读或写操作。

将寄存器(41H、42H、43H)中的值读取出来,仿真时序如下。

与IP核寄存器默认值一致。

同理,读取XADC的转换结果数据时,只需要读取对应寄存器位置中的数据即可。

电压转换

数据寄存器示意图如下,只有12位有效数据。

XADC的所有片上传感器都使用ADC的单极性工作模式;外部模拟输入通道,可以被配置单极性或双极性输入模式。两种输入模式的传递函数如下。

需要注意的是,外部模拟输入通道的满量程输入是1 V;而内部电源传感器的输入经过了3倍的衰减,所以对应满量程输入是3 V。

温度转换

片上温度测量结果转换公式和传递函数如下图所示。

参考资料:

ug480_7Series_XADC.pdf

pg091-xadc-wiz.pdf

这篇关于Vivado XADC IP核 使用详解的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!