本文主要是介绍BUS总线-Sky课程总结(1),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

非原创,是sky的bus课程,这里做一下归纳,方便大家回顾。

1.内容

(1)DDR的行为

(2)Cache的行为

(3)on-chip总线数据传输原理

(4)APB总线介绍

(5)AHB总线介绍

(6)AHB/AXI总线对比

(7)Bus-Arbiter/Bus-Matrix/Bus-Noc介绍

(8)AXI总线效率提升

(9)其他片上总线

2.课程的目的

(1)理解总线使用的目的

(2)理解总线数据传输原理

(3)掌握常用总线数据传输方法

(4)对一个总线框架的数字系统的基本构成与工作方式有基本的认识

(5)AHB/AXI总线的效能对比(设计复杂度,面积,数据传输带宽)

(6)AXI总线中提升数据传输带宽的必要性

3.为什么需要BUS

(1)统一标准:遵循相同的协议

(2)互连容易:功能增减非常的方便

4.什么是带宽

定义:每秒种传输了多少数据量

计算公式:带宽 = 时钟频率*数据位宽

带宽效率 = 实际带宽/峰值带宽

5.DDR的内部结构

(1)DDR主存为4个BANK或者8个BANK

(2)读写的操作不同于一般的访问SRAM,遵循规则如下

首先需要发送active指令,active指令的作用是选中多个bank中的某一个bank,在这个bank中选择一个row。

然后再发送读写指令,读写指令是选中这个row中的一个column。

注意:一个bank只能打开一个row,需要打开其他row,需要关闭上一个row。

(3)DDR的突发长度为4或者8。

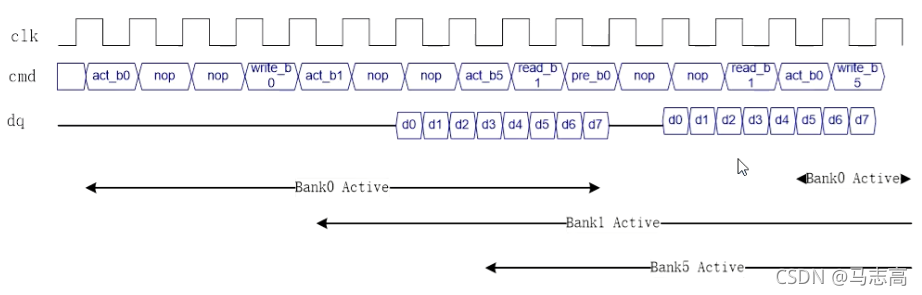

6.DDR Read/write WaveForm

存在问题:读写效率低下,如何提高效率

7.DDR Bank Interleave

如何理解:

1个bank开一个row,

我们有四个或者八个bank,那么可以每个bank都开一个row,

把不同的bank指令参杂在一起,从而提高了读写效率,

这就是bank Interleave。

(学了计算机原理之后会发现这个思想就是流水线的思想)

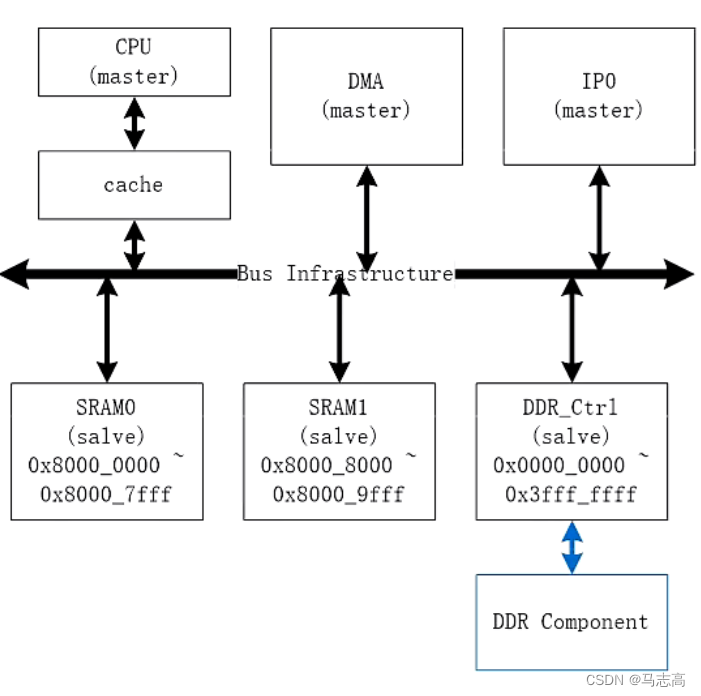

8.Cache所处的位置

9.Cache的功能和工作行为

1.cache的功能:buffer近期经常访问的数据,提高数据存取的效率,减小BUS的带宽消耗

2.cache的读行为

(1)若hit,则cpu直接从cache中读取数据即可

(2)若miss,有两种处理方式

1.read through ,从内存(最终的slave)中读取数据,但不缓存到cache

2.read allocate,从内存(最终的slave)中读取数据,同时缓存到cache

那么为什么要使用read through,只用read allocate是否可行

1.不是经常访问的数据不需要存入cache中,使用read through即可,否则回把常用的数据从cache中踢出。

2.UART,IIC等数据地址不能存入到cache中,否则会导致功能出错。

3.cache的写行为

(1)若hit,有两种处理方式

1.write through :把数据同时写到cache和内存中。

2.write back :把数据写到cache中,然后通过flush方式写入到内存中。

(2)若miss,有两种处理方式

1.write allocate:先把要写的数据载入到cache中,然后再write through or write back。

2.No write allocate:直接把要写的数据写入到内存当中。

为什么需要有write through?

一致性的问题,当很多master共享数据的时候,虽然浪费了写的带宽,但是节省了读的带宽。(还是不理解)

为什么要有no write allocate

还是uart等外接接口,需要把数据直接写入终端,而不能写入cache。

4.cache的flush

通过flush指令,强制把cache中的某部分数据(或全部数据)写回到终端地址,该部分数据仍然在cache中。(强制刷新)

为什么需要flush?

当大量数据计算时(不太明白)

5.cache invalidate

通过invalidate指令,强制把cache中某部分数据(或全部数据)标志为无效,同时把该部分写回到终端地址。(强制清空)

为什么需要invalidate?

当关机或者应用切换的时候。

6.cache的硬件原理

cache line (cache的最小地址)

cache bank size

7.cache只能服务与cpu吗?

cache也可以服务与其他IP。

这篇关于BUS总线-Sky课程总结(1)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!