本文主要是介绍STM32 FSMC (Flexible static memory controller) 灵活静态内存控制器介绍,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- 1. 介绍FSMC

- 2. FSMC特点

- 3. Block示意图

- 4. AHB接口

- 4.1 Supported memories and transactions

- General transaction rules

- Configuration registers

- 5. 外部设备地址映射

- 5.1 NOR/PSRAM地址映射

- 将NOR Flash/PSRAM的支持进行封装

- 5.2 NAND/PC Card地址映射

1. 介绍FSMC

说到STM32的FSMC(Flexible Static Memory Controller),这个玩意儿可真是STM32家族的“多面手”。想象一下,如果STM32是个热衷于DIY的工程师,那FSMC就是他的瑞士军刀,无论是连接SRAM、PSRAM、NOR/NAND Flash还是LCD模块,FSMC都能应对自如,简直就是连接外部存储和记忆界的“桥梁”。

FSMC的灵活性主要体现在它支持多种存储器类型和访问模式,这就像是它可以说多国语言,无论你来自哪个存储器国家,它都能和你愉快地交流。而且,FSMC能够让STM32以最高效的方式访问这些外部设备,这就像是它拥有VIP通道,能够迅速通过安检进入存储器的心脏区域。

具体来说,FSMC能让你配置各种访问参数,比如数据宽度(可以是8位或16位),存储器类型(SRAM、NOR Flash等),还有访问模式(直接模式、间接模式)。这就像是你在玩一个高级定制的游戏,你可以根据外设的特性和你的需求,调整FSMC的设置,以达到最优的访问速度和性能。

不过,FSMC也有它的复杂性,配置起来就像是在玩一个需要高度策略的游戏,每个选项都需要精心考虑。你得了解你的外部设备,知道它的语言和习惯,然后通过FSMC的配置,来告诉STM32如何与之有效交流。这就需要你深入阅读数据手册,可能还要做一些试验,来找到最佳配置。

总之,FSMC就像是STM32的“通讯专家”,能够让STM32轻松地扩展存储和连接各种外设。但要想完全驾驭它,你可能需要像学习外语一样,花一些时间和精力来深入了解它。别担心,一旦你熟悉了FSMC,你就能打开一个全新的可能性世界,让你的STM32项目更加强大和灵活!

2. FSMC特点

FSMC模块能够与同步和异步存储器以及16位PC内存卡进行接口。其主要目的是:将AHB事务转换为适当的外部设备协议,满足外部设备的访问时序要求。所有外部存储器与控制器共享地址、数据和控制信号。每个外部设备通过唯一的芯片选择来访问。FSMC一次只对一个外部设备进行访问。

FSMC具有以下主要特点:

- 与静态内存映射设备接口,包括:

- 静态随机访问存储器(SRAM)

- NOR Flash 存储器/OneNAND Flash 存储器

- PSRAM(4个内存Bank)

- 具有ECC硬件检查最多8 K字节数据的两个 NAND Flash 存储区

- 支持16位 PC 卡兼容设备

- 支持对同步设备(NOR Flash 和 PSRAM)进行突发模式访问

- 8位或16位宽数据总线

- 每个内存Bank独立芯片选择控制

- 每个内存Bank独立配置

- 可编程定时以支持各种不同类型的设备,特别是:

- 可编程等待状态(最多15个)

- 可编程总线回转周期数(最多15个)

- 可编程输出使能和写使能延迟时间(最多15个)

- 独立读取和写入时序和协议,以支持各种记忆体和时序变化。

- 用于PSRAM 和 SRAM 设备的写使能和字节通道选择输出。

- 将32位宽 AHB 事务转换为连续16位或8位对外部16位或8位装置进行访问。

- A Write FIFO,长度为2字(STM32F42x and STM32F43x长度为16字),每一个词都是32比特宽,仅仅保存了数据而没有地址.因此这样可以缓冲AHB 写突发事务. 这样就可以向慢速度记忆体中写入并且迅速释放AHB用于其他操作.只有一个突发同时被缓冲:如果新出现了一个AHB 突发或者单次传输在之前

- 外部异步等待控制

定义外部设备类型和相关特性的FSMC寄存器通常在启动时设置,并且在下一次复位或上电之前不会改变。然而,可以随时更改这些设置。

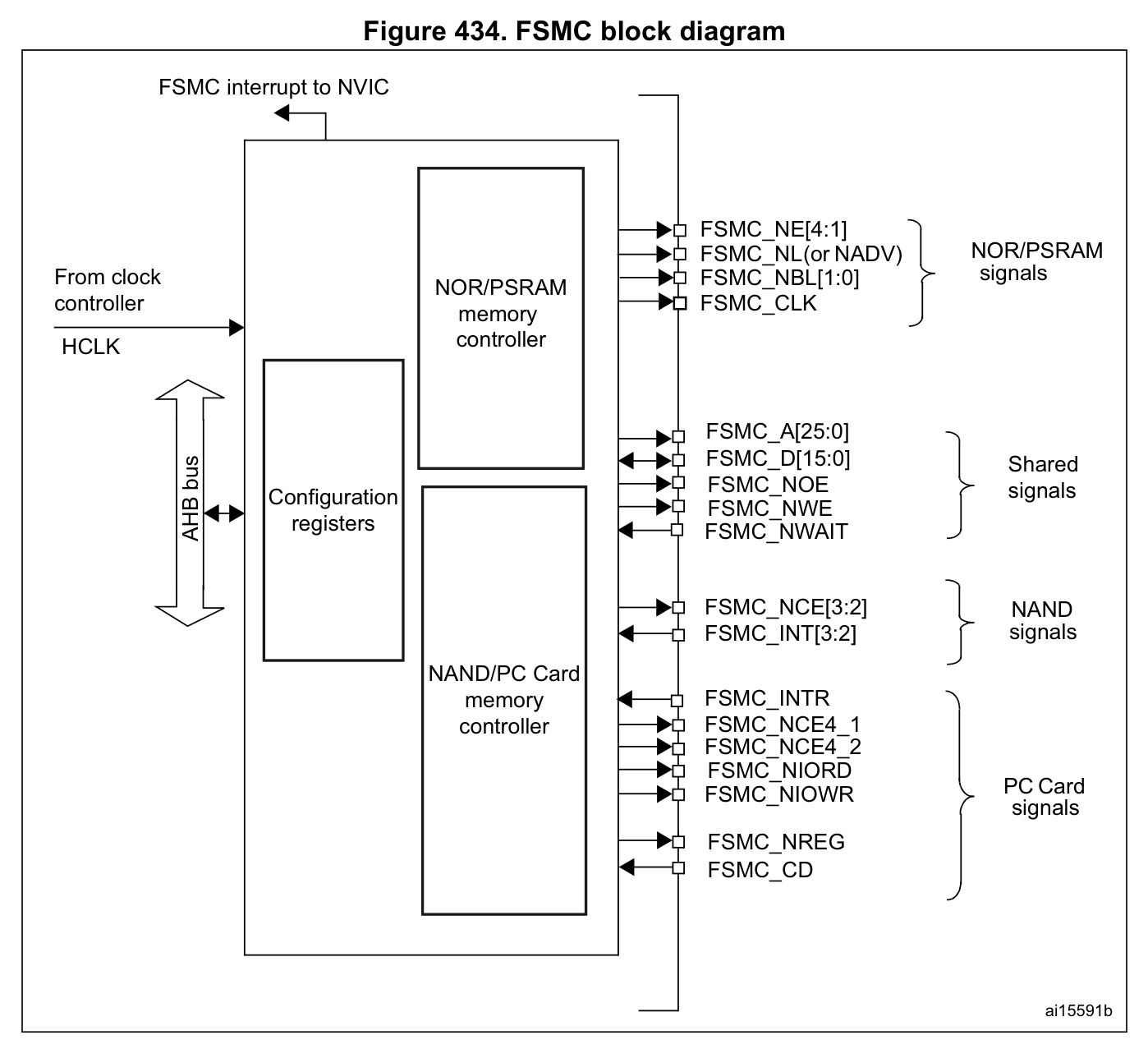

3. Block示意图

FSMC由四个主要模块组成:

-

AHB接口(包括FSMC配置寄存器)

-

NOR Flash/PSRAM控制器

-

NAND Flash/PC卡控制器

-

外部设备接口。

图434显示了该模块的框图。

4. AHB接口

AHB从设备接口使得内部CPU和其他总线主设备能够访问外部静态存储器。AHB事务被转换为外部设备协议。特别地,如果选择的外部存储器是16位或8位宽度,则在AHB上的32位宽度事务会被分割成连续的16位或8位访问。FSMC芯片选择(FSMC_NEx)在执行带有扩展模式的D模式下除了进行连续访问时不会切换。

FSMC在以下情况下生成AHB错误:

- 当读取或写入未启用的FSMC存储器时

- 当在FSMC_BCRx寄存器中FACCEN位被复位时,读取或写入NOR Flash存储器

- 当输入引脚FSMC_CD(卡片存在检测)为低电平时,读取或写入PC卡存储器

这个AHB错误的影响取决于尝试进行读写访问的AHB主设备:

-

如果是带有FPU的Cortex®-M4 CPU,将会生成一个硬件故障中断。

-

如果是DMA,则会产生DMA传输错误,并自动禁用相应的DMA通道。

AHB时钟(HCLK)是FSMC的参考时钟。

4.1 Supported memories and transactions

General transaction rules

所请求的AHB事务数据大小可以是8位、16位或32位,而访问的外部设备具有固定的数据宽度。这可能导致传输不一致。因此,必须遵循一些简单的事务规则:

-

AHB事务大小和内存数据大小相等时,在这种情况下没有问题。

-

AHB事务大小大于内存大小时,在这种情况下,FSMC将AHB事务分割成较小的连续内存访问,以满足外部数据宽度。

-

AHB事务大小小于内存大小时,异步传输可能与外部设备类型有关

-

对于具有字节选择功能(SRAM、ROM、PSRAM)的设备进行异步访问。

- FSMC通过其字节通道NBL[1:0]允许写入操作来访问正确的数据。

- 允许读取操作。读取所有内存字节并丢弃无用字节。在读取操作期间保持NBL[1:0]低电平。

-

对于没有字节选择功能(NOR和NAND Flash 16位)的设备进行异步访问。

当请求对16位宽Flash存储器进行字节访问时会出现这种情况。显然,不能以字节模式访问该设备(只能从/向Flash存储器读取/写入16位词),因此: -

不允许写入操作

-

允许读取操作。读取所有内存字节并丢弃无用字节。在读取操作期间将NBL[1:0]设置为0.

-

Configuration registers

FSMC可以通过寄存器集进行配置。详细描述了NOR Flash/PSRAM控制寄存器的内容,请参见第36.5.6节。详细描述了NAND Flash/PC卡寄存器的内容,请参见第36.6.8节。

5. 外部设备地址映射

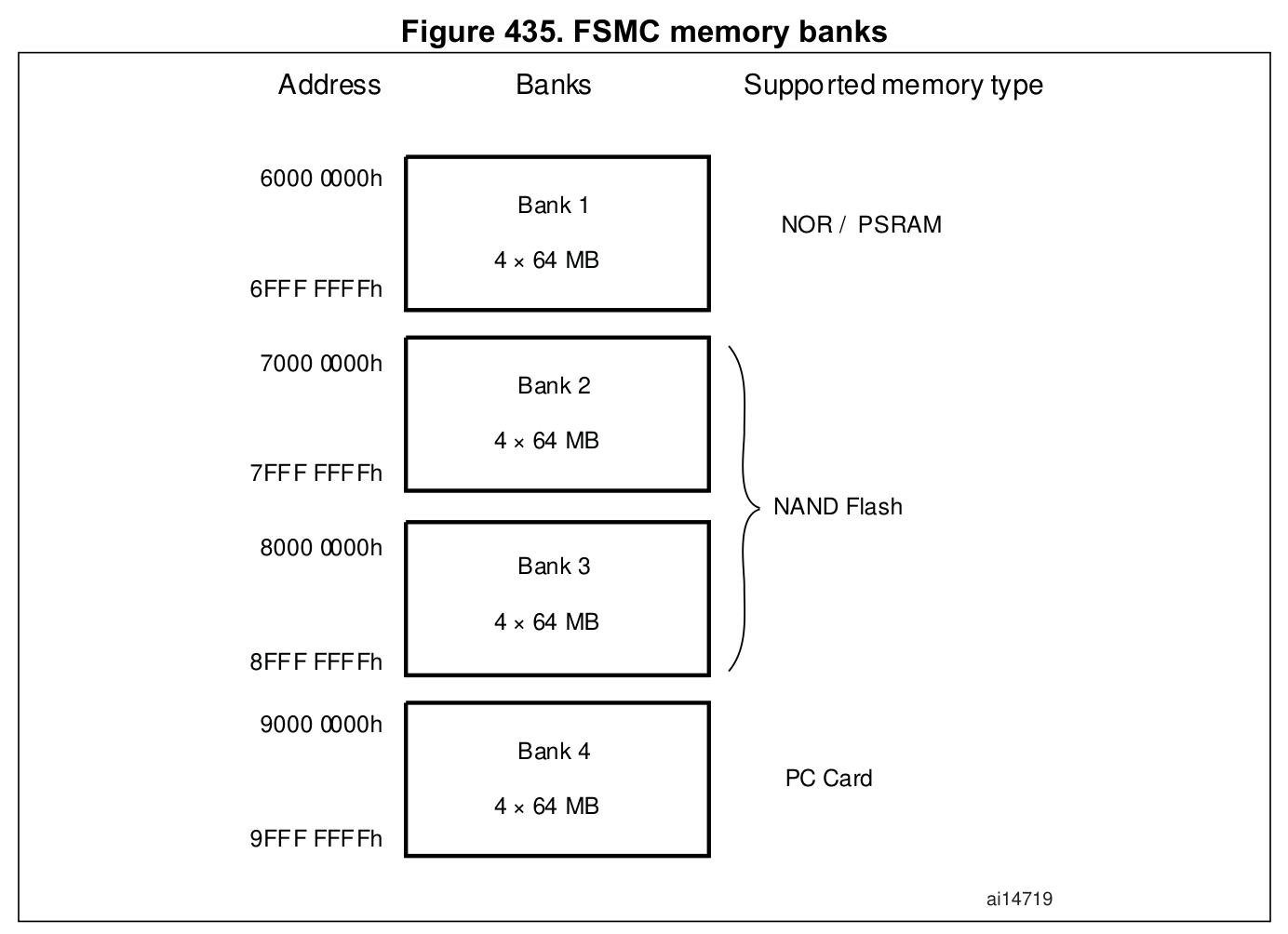

从FSMC的角度来看,外部存储器被分为4个固定大小的256兆字节的Bank(参见图435):

-

Bank1用于寻址最多4个NOR Flash或PSRAM存储器设备。该Bank被分成4个NOR/PSRAM子Bank,每个子Bank有4个专用芯片选择信号,如下所示:

-

Bank1 - NOR/PSRAM 1

-

Bank1 - NOR/PSRAM 2

-

Bank1 - NOR/PSRAM 3

-

Bank1 - NOR/PSRAM 4

-

-

Bank2和3用于寻址NAND Flash设备(每个Bank一个设备)

-

Bank4用于寻址PC卡设备

对于每个Bank,要使用的存储器类型由配置寄存器中用户定义。

5.1 NOR/PSRAM地址映射

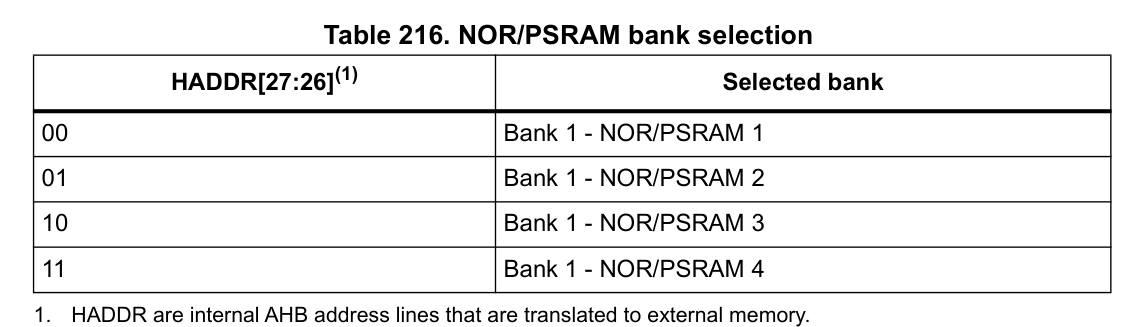

HADDR[27:26]位用于根据表216中的显示选择四个内存Bank之一。

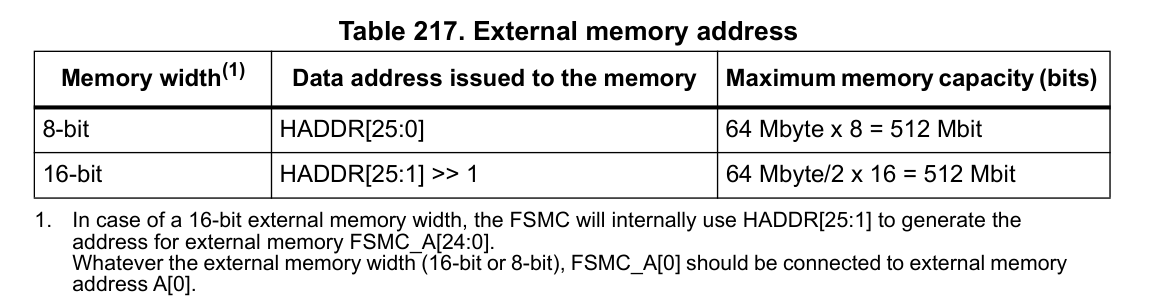

HADDR[25:0]包含外部存储器的地址。由于HADDR是字节地址,而存储器是按字寻址的,根据存储器数据宽度,实际发给存储器的地址会有所变化,如下表所示。

将NOR Flash/PSRAM的支持进行封装

不支持同步存储器的Wrap burst模式。必须将存储器配置为未定义长度的linear burst模式。

5.2 NAND/PC Card地址映射

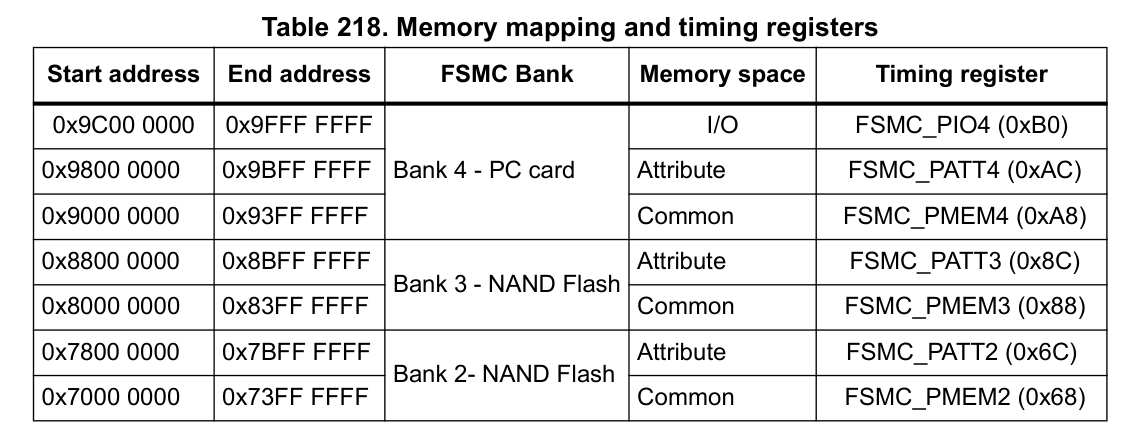

在这种情况下,有三家Bank可供选择,每个Bank都被划分为表218中所示的内存空间。

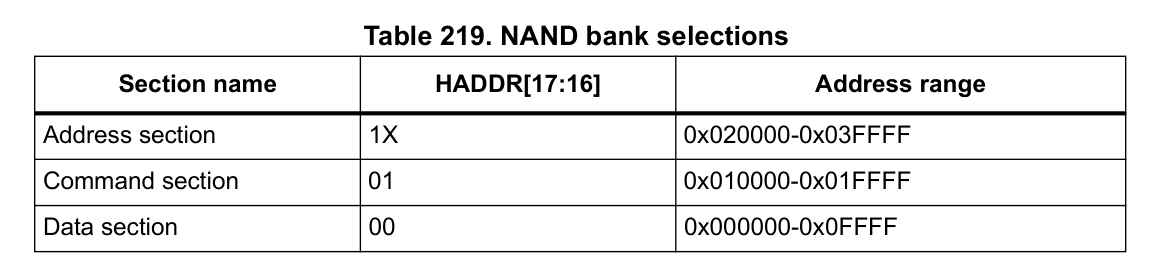

对于NAND Flash存储器,常见和属性内存空间被细分为三个部分(见下表219)位于较低的256 K字节中:

- 数据部分(在常见/属性内存空间中的前64 K字节)

- 命令部分(在常见/属性内存空间中的第二个64 K字节)

- 地址部分(在常见/属性内存空间中接下来的128 K字节)

应用软件使用3个部分来访问NAND Flash存储器:

- 发送命令到NAND Flash存储器:软件必须将命令值写入命令部分的任何内存位置。

- 指定要读取或写入的NAND Flash地址:软件必须将地址值写入地址部分的任何内存位置。由于地址可能是4或5字节长(取决于实际内存大小),需要连续多次写入地址部分以指定完整的地址。

- 读取或写入数据:软件从数据部分的任何内存位置读取或写入数据值。

由于NAND Flash存储器自动递增地址,因此无需递增数据部分的地址以访问连续的内存位置。

这篇关于STM32 FSMC (Flexible static memory controller) 灵活静态内存控制器介绍的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!