本文主要是介绍FPGA-TCS模块,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

摘要: TCS部分,包含10ms的generate module、state module、switch module,该部分主要是在拿到1PPS后,模块内部会生成10ms的脉冲。这个10ms脉冲会给予到各个模块(state module 和 switch module)使用,state module会产生DL、UL、GP的单比特信号给到switch module 使用,switch module会产生各种控制开关的信号。

文章目录

- 前言

- 一、TCS

- 二、state machine

- 三、switch

前言

简单的小工程,可以当作入门练习或者学习

一、TCS

说实话,我对TCS的理解并不是很深入,只是按照项目要求完成了其中的部分功能。

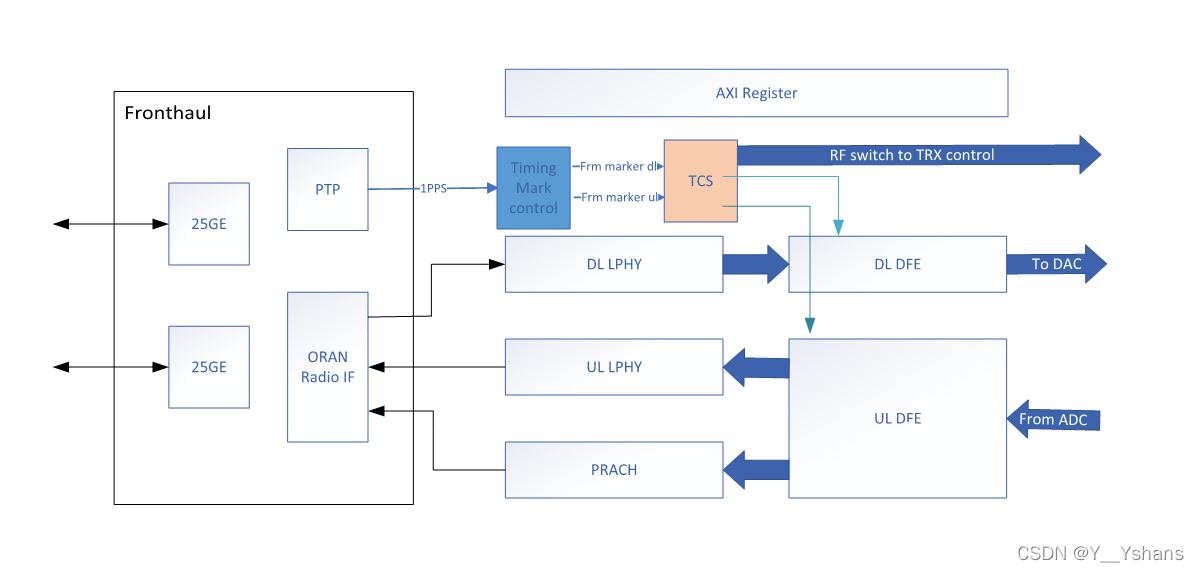

我对TCS的理解是:产生控制信号的模块。那么负责哪些控制模块呢?我觉得主要是给DFE的UL信号和DL信号,以及switch信号。当然项目不同,功能也可能不同。

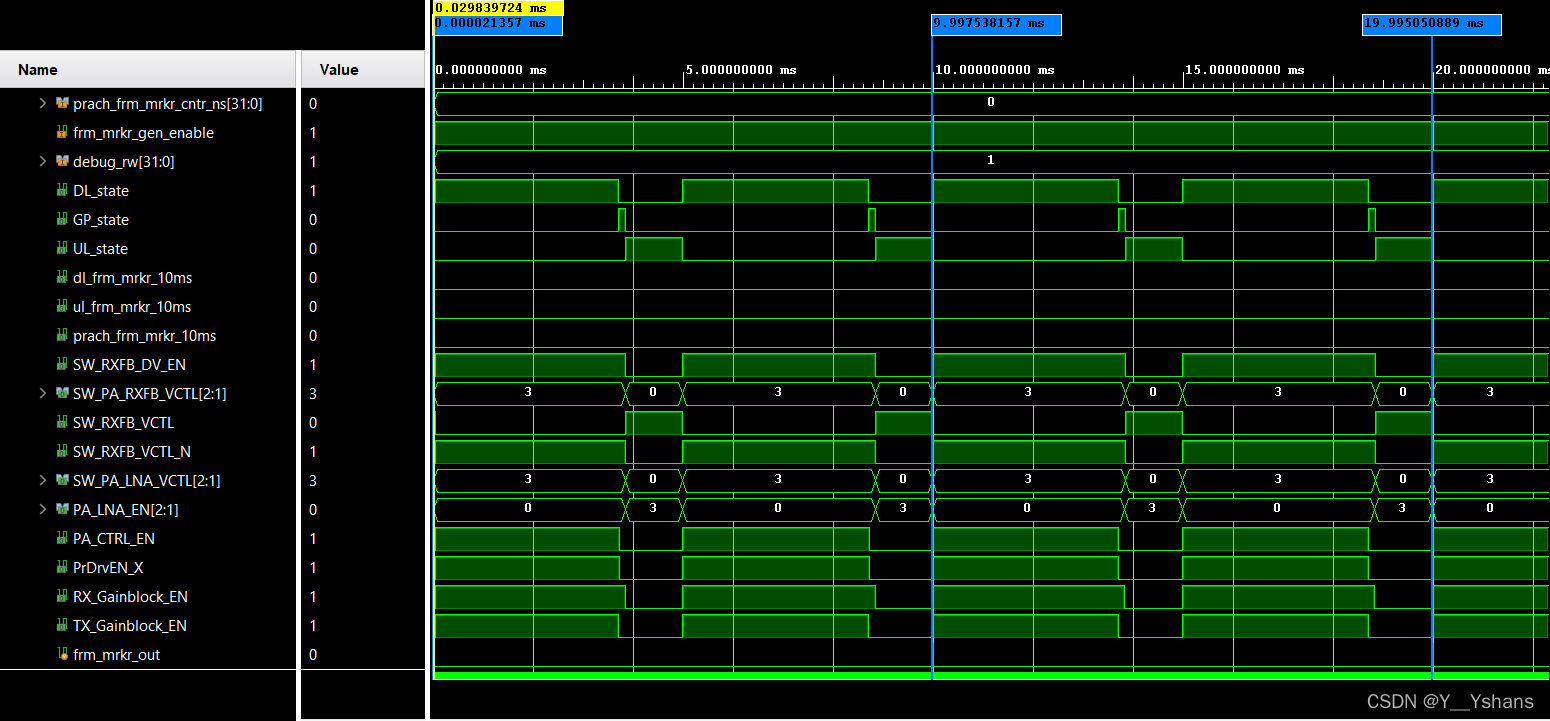

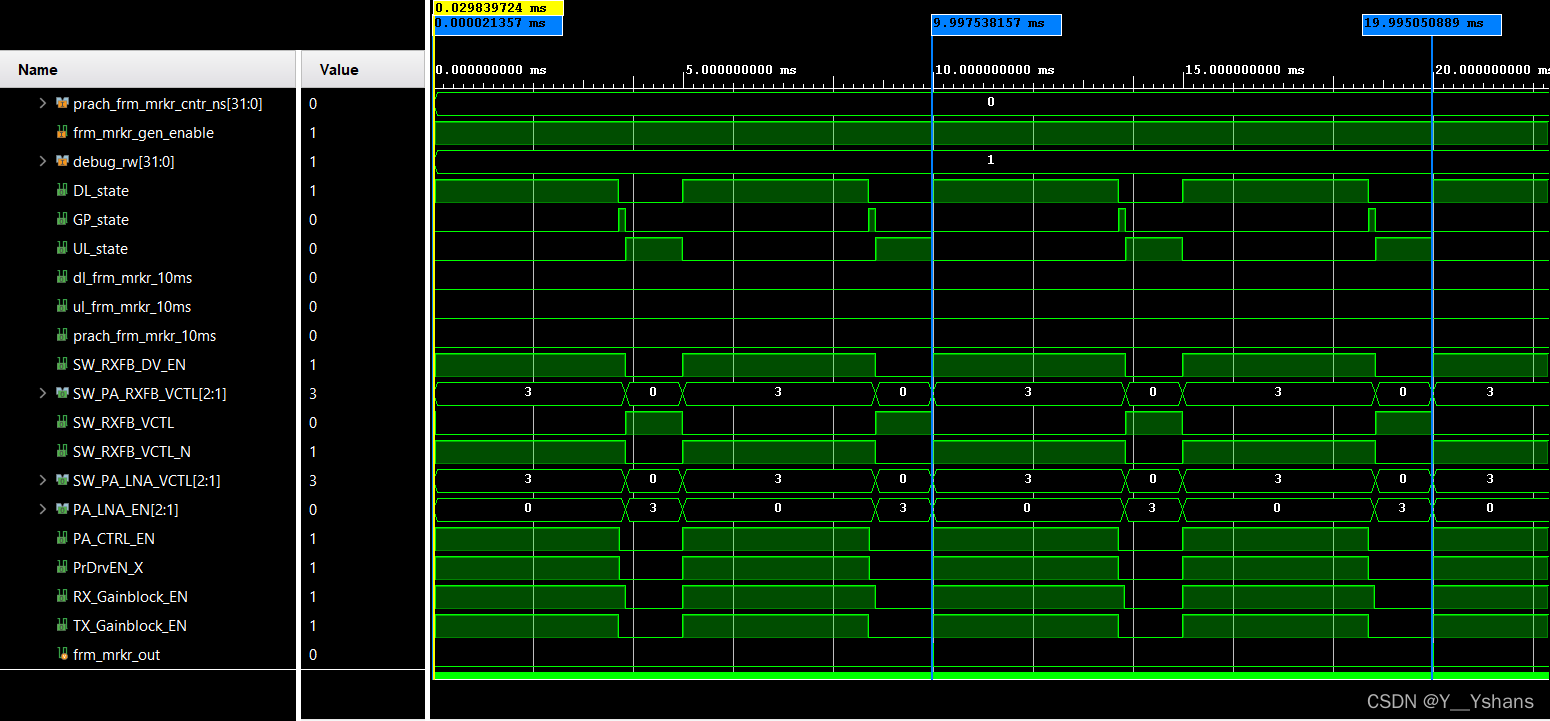

TCS整个模块最后产生的效果,如图:

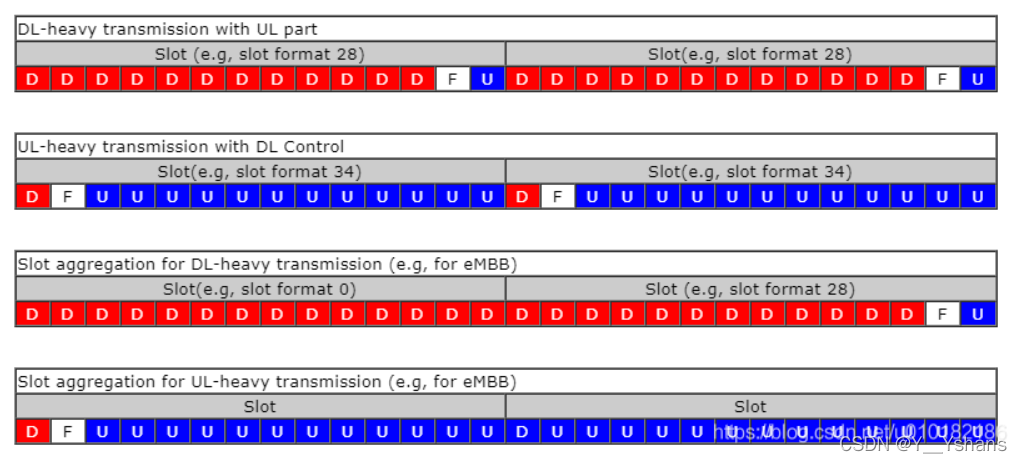

DL、UL、以及各种switch信号都成周期信变化(10ms一个周期)。在这里面,DL、UL的持续时间,以及开关在什么时刻开和关都是有规定的。比如在完成这部分的时候就需要知道时隙结构、无线帧结构。

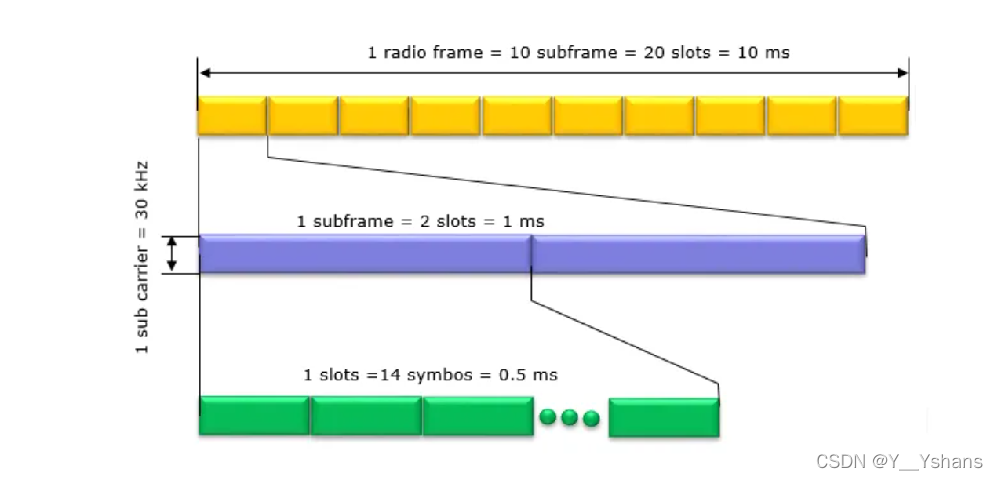

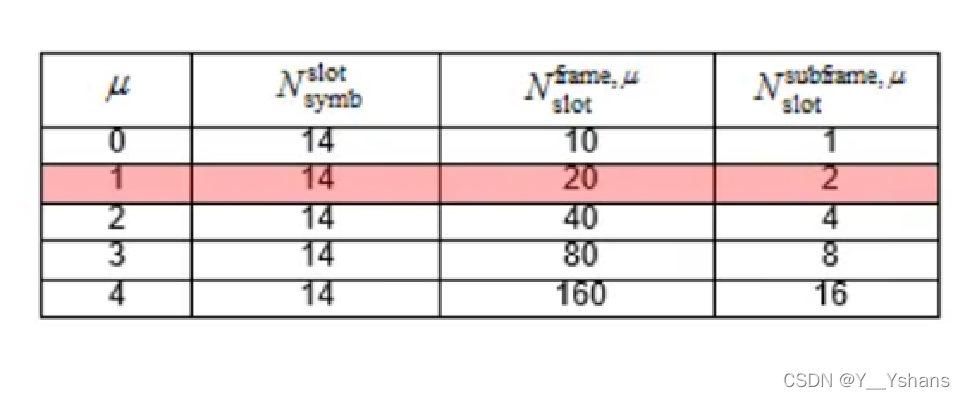

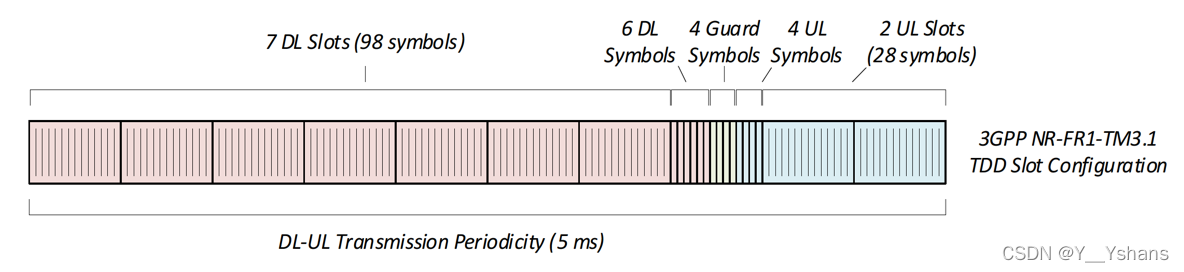

对于无线帧结构,它的长度一般是10ms,子帧长度是1ms,在一个子帧中可以放置不同数量的时隙,slot越多,它的长度就会越短,子载波间隔就会越大。这里在实现的时候选择配置的是2个时隙,也就是说,一帧里面有十个子帧,一个子帧里面有两个slot,一个slot里面有14个symbol。

时隙里也有对应组合结构,时隙格式规定了如何使用单个时隙中得每个符号,它定义了哪些符号用于上行链路,哪符号用于下行链路,并不一定每个符号都需要使用。那么多不同类型得时隙格式是为了使调度更加灵活,便于TDD的操作。 D和U里面一般都放各种各样的数据,F(GP)里面会放一些天线校准数据。

我在初步设计的时候,只加了两个两种格式吧,一种全是DL的,一种DL:UL=7:3。这里只附图7:3的格式

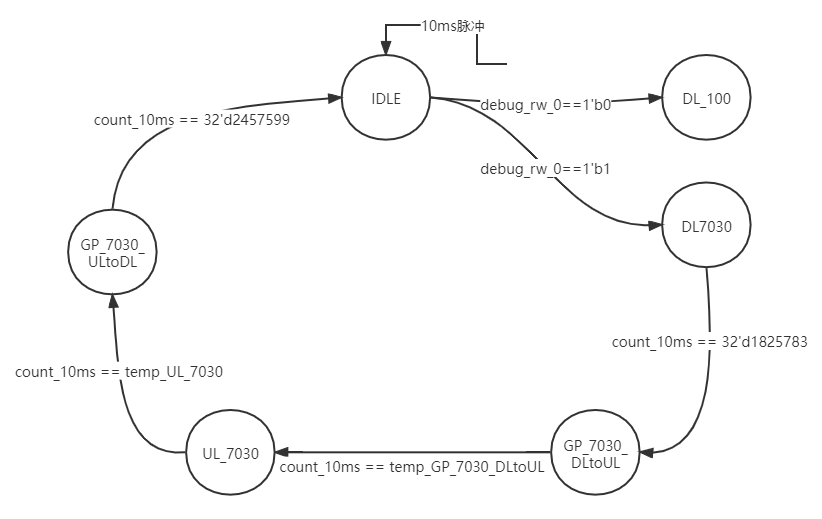

二、state machine

状态机这部分感觉没什么多讲的,有状态图的话,直接就能写出来了。当时犯了两个错误吧,状态机,个人建议最好用三态式,然后状态跳转的部分可以使用组合逻辑(一般对于程序不会有太大的影响),其它的部分最好用时序逻辑,如果不这样可能会对整个项目的时序产生影响(个人理解虽然还不知道原因以及会造成什么不好的影响)。

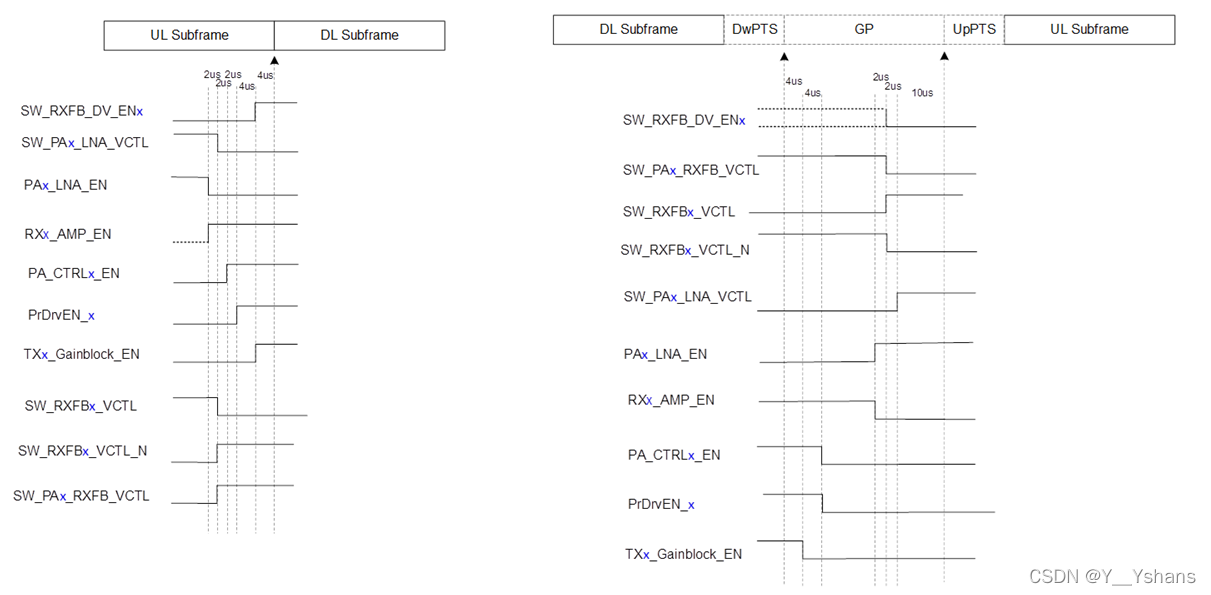

三、switch

上下行持续时间确定了,那么开关也是根据DL和UL确定的。开关会在DL和UL之前打,我想是因为,开关开启或者关闭都需要一点时间,所以才会提前开关。

总结

这个工程暂不想提供下载,如果实在需要,私聊。

(工程代码已经上传。)

FPGA-TCS.7z-硬件开发文档类资源-CSDN下载

最终实现效果图,放一下吧。

参考文章

子载波间隔

5G学习笔记:NR帧结构

LTE-FDD和TDD帧结构

这篇关于FPGA-TCS模块的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!